## ARM Microprocessors 3

# Code Size: ARM vs. Thumb

| if     | (x>=0) return x  |                               |                        |

|--------|------------------|-------------------------------|------------------------|

| els    | se return -x     |                               |                        |

| 🔶 AR   | M assembly versi | on                            |                        |

| iabs   | CMP r0,#0        | ;Compare r0 to zero           | $2 \times 4 = 8$ bytes |

|        | RSBLT r0,r0,#0   | ;If r0<0 (less than=LT) then  | do r0= 0-r0            |

|        | MOV pc,lr        | ;Move Link Register to PC (   | Return)                |

| 🔷 Thi  | umb assembly ver | sion                          |                        |

|        | CODE16           | ;Directive specifying 16-bit  |                        |

| (Thum  | b)               |                               |                        |

|        |                  | ;instructions                 | 4 x 3 = 12 bytes       |

| iabs   | CMP r0,#0        | ;Compare r0 to zero           |                        |

|        | BGE return       | ;Jump to Return if greater or | equal to zero          |

|        | NEG r0,r0        | ;If not, negate r0            |                        |

| return | MOV pc,lr        | ;Move Link register to PC (I  | Return)                |

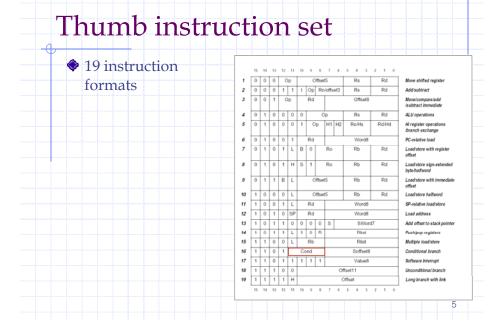

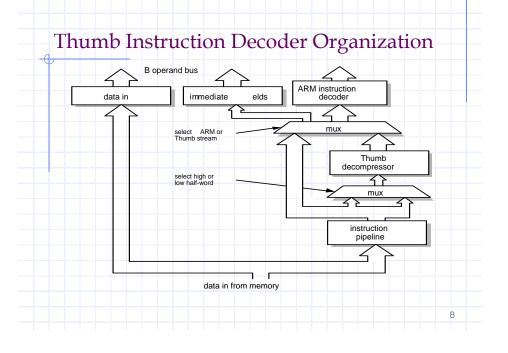

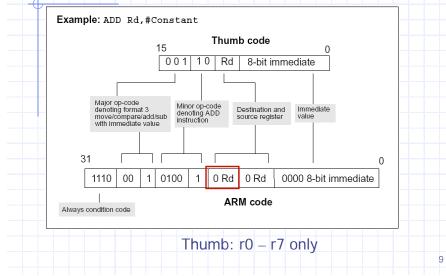

# The Thumb Instruction Set 16-bit Instructions (vs. 32-bit ARM instructions) Used to improve the code density About 30% reduction over ARM for the same code Each Thumb instruction mapped to the equivalent ARM instruction: ADD r0, #3 → ADDS r0, r0, #3 Not conditionally executed except for 'B' Separate instructions for the barrel shift operations

# **Thumb-ARM Differences**

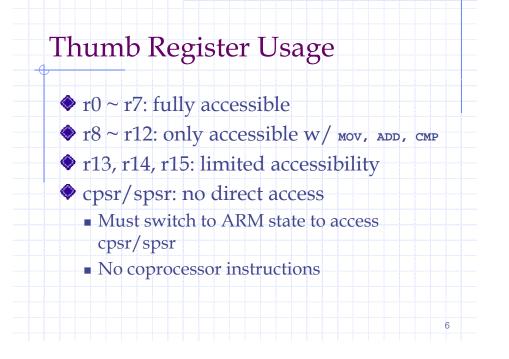

- Most Thumb instructions executed unconditionally

- All the ARM instructions executed conditionally

- Many Thumb data processing instructions use a 2-address format (destination reg == one of source reg)

- Less regular instruction formats over ARM (for the code density)

| otra                                              | action                                | On                     | 000                    | 100       | Mnemonic | Instruction                    | Lo register<br>operand | Hi register<br>operand | Conditio<br>codes se |

|---------------------------------------------------|---------------------------------------|------------------------|------------------------|-----------|----------|--------------------------------|------------------------|------------------------|----------------------|

| struction Opcodes                                 |                                       |                        |                        |           | ADC      | Add with Carry                 | ~                      |                        | ~                    |

| <del>,                                     </del> |                                       |                        |                        |           | ADD      | Add                            | ~                      | ~                      | <b>v</b> 0           |

|                                                   |                                       |                        |                        |           | AND      | AND                            | r                      |                        | r                    |

|                                                   |                                       |                        |                        |           | ASR      | Arithmetic Shift Right         | ~                      |                        | ~                    |

|                                                   |                                       |                        |                        |           | в        | Unconditional branch           | ~                      |                        |                      |

|                                                   |                                       |                        |                        |           | Bxx      | Conditional branch             | v                      |                        |                      |

| Mnemon                                            | ic Instruction                        |                        | 100                    | Condition | BIG      | Bit Glear                      | r                      |                        | r                    |

| Mnemon                                            | ic Instruction                        | Lo register<br>operand | Hi register<br>operand | codes set | BL       | Branch and Link                |                        |                        |                      |

| NEG                                               | Negate                                | ~                      |                        | ~         | BX       | Branch and Exchange            | ~                      | ~                      |                      |

| ORR                                               | OR                                    | ~                      |                        | ~         | CMN      | Compare Negative               | ~                      |                        | ~                    |

| POP                                               | Pop registers                         | ~                      |                        |           | GMP      | Compare                        | r                      | r                      | r                    |

| PUSH                                              | Push registers                        | ~                      |                        |           | EOR      | EOR                            | ~                      |                        | ~                    |

| ROR                                               | Rotate Right                          | -                      |                        | -         | LDMIA    | Load multiple                  | ~                      |                        |                      |

| SBC                                               | Subtract with Carry<br>Store Multiple | -                      |                        | ~         | LDR      | Load word                      | ~                      |                        |                      |

| STMA                                              | Store word                            | ~                      |                        | _         | LDRB     | Load byte                      | ~                      |                        |                      |

| STRB                                              | Store byte                            | ~                      |                        |           | LDRH     | Load halfword                  | ~                      |                        |                      |

| STRH                                              | Store halfword                        | 1                      |                        |           | LSL      | Logical Shift Left             | ~                      |                        | ~                    |

| SWI                                               | Software Interrupt                    |                        |                        |           | LDSB     | Load sign-extended             | ~                      |                        |                      |

| SUB                                               | Subtract                              |                        |                        | byte      |          |                                |                        |                        |                      |

| TST                                               | Test bits                             | v                      |                        | ~         | LDSH     | Load sign-extended<br>halfword | ~                      |                        |                      |

|                                                   |                                       |                        |                        |           | LSR      | Logical Shift Right            | ~                      |                        | ~                    |

|                                                   |                                       |                        |                        |           | MOV      | Move register                  | ~                      | ~                      | <b>v</b> 2           |

|                                                   |                                       |                        |                        |           | MUL      | Multiply                       | ~                      |                        | ~                    |

|                                                   |                                       |                        |                        |           | MVN      | Move Negative register         | ~                      |                        | ~                    |

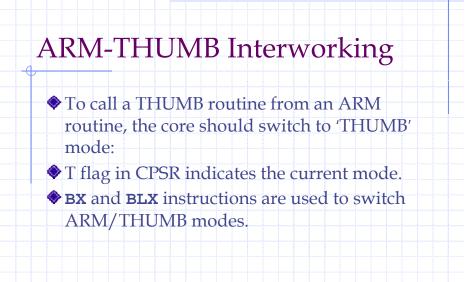

# BX & BLX Instructions

BX Rm ; branch exchange

pc = Rm & 0xfffffffe

$\blacksquare T = Rm[0]$

**BLX** *Rm* | *label* ; branch exchange w/link

Ir = inst. addr after BLX + T

$\square$  pc = label, T = label[0]

= pc = Rm & 0xffffffe, T = Rm[0]

10

12

## BLX Example (ARM -> Thumb)

CODE32 LDR r0, =thumbCode + 1 BLX r0

CODE16

thumbCode ADD r1, #1

BX lr

| BLX Example (Thumb $\rightarrow$ ARM) | Thumb Advantages                                                                   |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| CODE16                                | Space: About 70% of ARM code                                                       |  |  |  |

| LDR r0, =ARMCode                      | # of Instructions: About 140% of ARM cc                                            |  |  |  |

| BLX r0                                | Exec. Time:                                                                        |  |  |  |

| DLA IO                                | • With a 32-bit memory, ARM code is about 4                                        |  |  |  |

| CODERS                                | faster over Thumb code                                                             |  |  |  |

| CODE32                                | <ul> <li>With a 16-bit memory, Thumb code is about faster over ARM code</li> </ul> |  |  |  |

| ARMCode                               | Thumb code consumes about 30% less                                                 |  |  |  |

| ADD r1, #1                            |                                                                                    |  |  |  |

| BX lr ; lr[0] was already set to 1.   | memory power.                                                                      |  |  |  |

| 13                                    |                                                                                    |  |  |  |