### Chapter 4 Differential Amplifiers

## **CMOS Differential Amplifiers**

**Basic Concepts-L15**

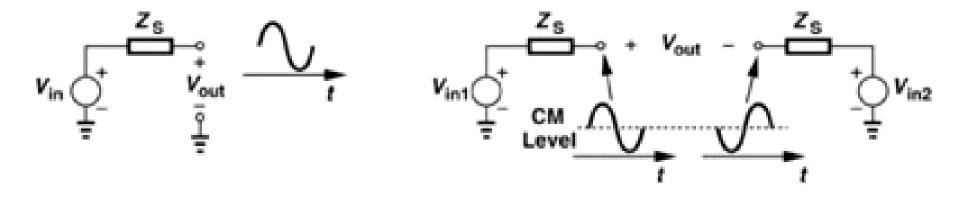

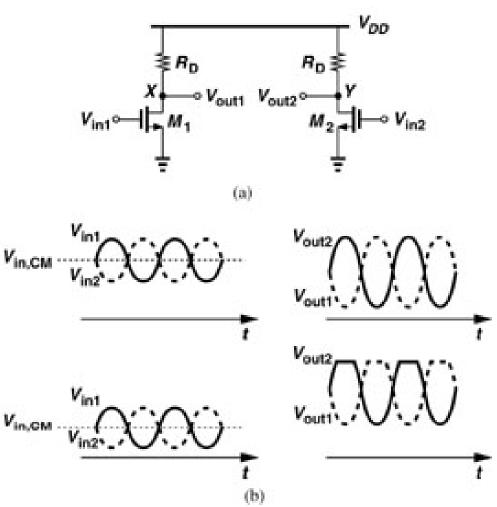

#### Single-ended vs. Differential Signals

- Single-ended signal: Measured with respect to a fixed potential, typically ground.

- Differential signal: Measured between two symmetric nodes (nodes have equal and opposite signal excursions around a fixed potential, called a "common-mode" level)

## Why Differential?

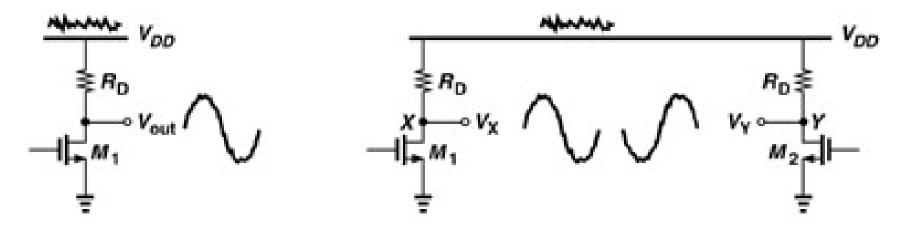

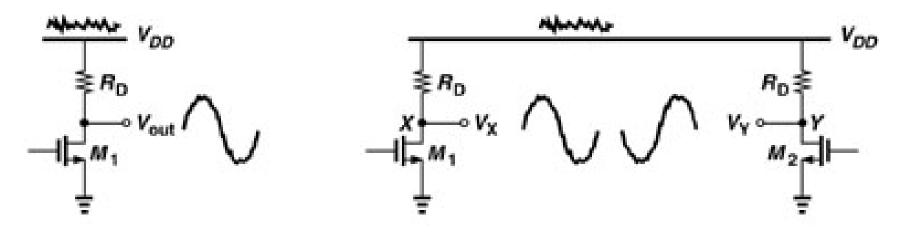

- In a single amplifier V<sub>DD</sub> fluctuations appear directly on the amplified signal.

- In a differential pair, if we measure  $V_X$   $V_Y$  the fluctuations cancel out.

## Why Differential?

- In a single CS amplifier, the maximum swing is  $V_{DD}$ -( $V_{GS}$ - $V_{TH}$ )

- In a differential pair it can be shown that the swing of  $V_X-V_Y$  can reach  $2[V_{DD}-(V_{GS}-V_{TH})]$ .

# Other advantages of differential amplifying

- Simpler biasing

- Higher linearity

#### Simple Symmetric Differential Pair won't do!

Good features: Rejection of VDD fluctuations, Larger swing.

Key problem: Input signal commonmode affects bias conditions, and differential amplification.

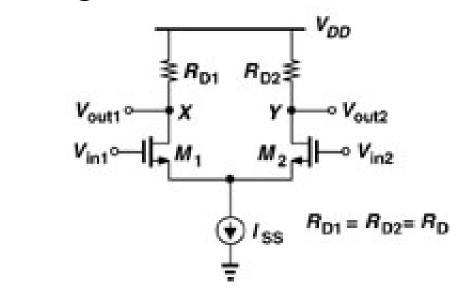

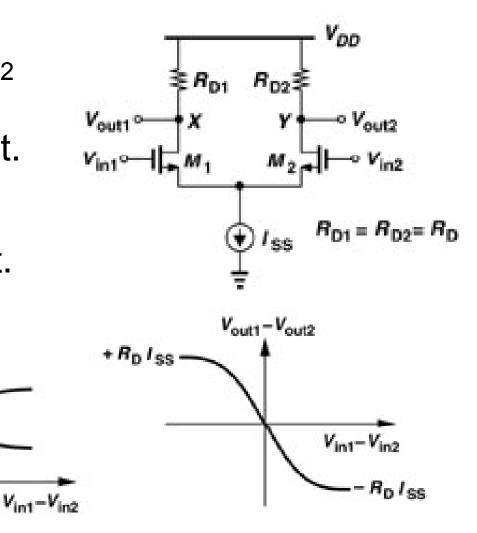

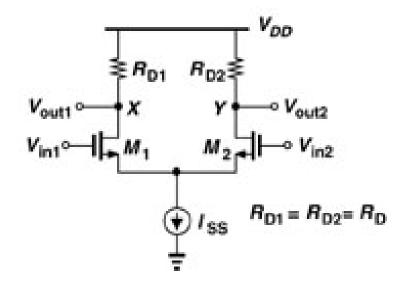

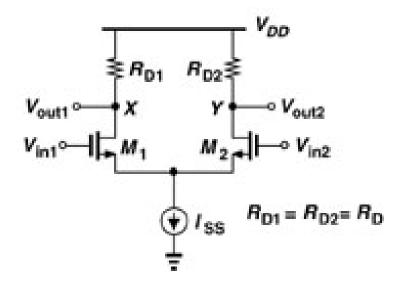

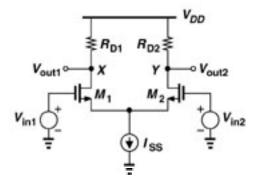

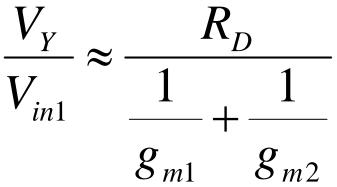

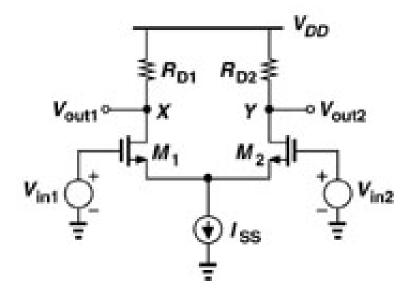

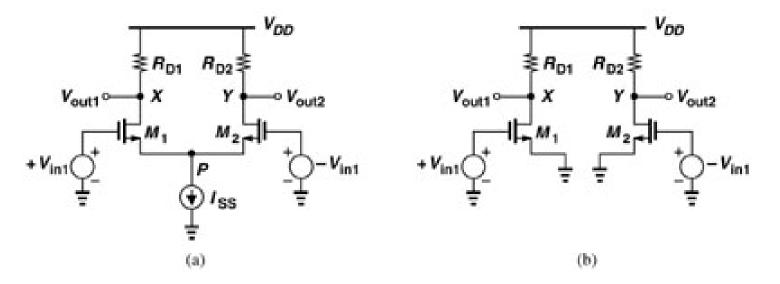

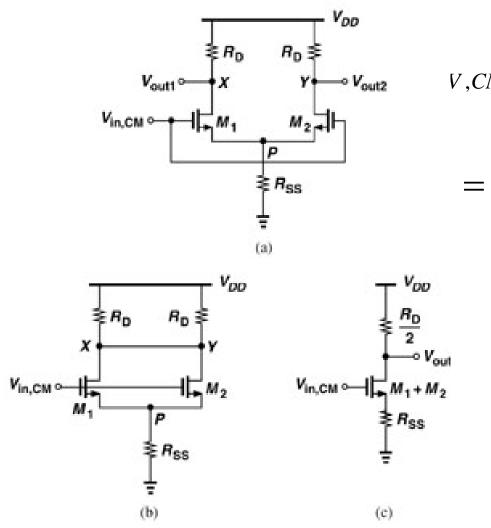

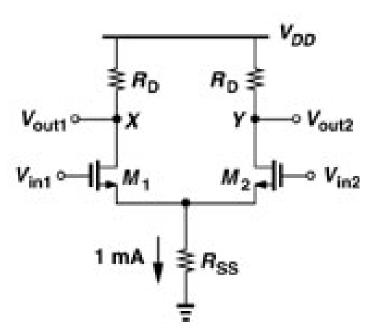

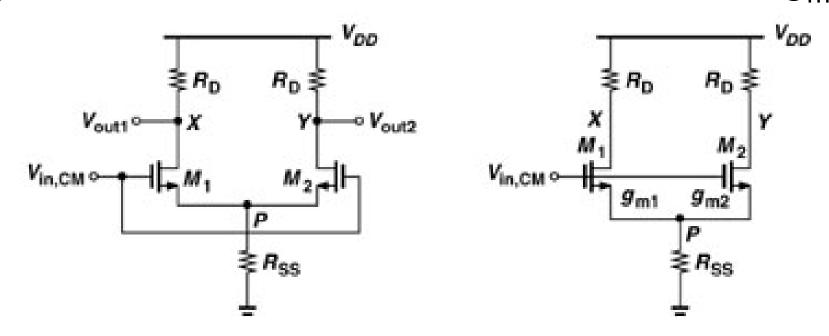

## Solution: Source-coupled ("long-tailed") Pair, biasing with a current source

If  $V_{in1}=V_{in2}$  then  $I_{D1}=I_{D2}=I_{SS}/2$ Then  $V_{out1}=V_{out2}=V_{DD}-R_DI_{SS}/2$

#### "Current stealing " phenomenon

If  $V_{in1}$  >>  $V_{in2}$ , then  $M_2$ turns off and  $M_1$ steals all the current.

If  $V_{in1} << V_{in2}$  then  $M_2$  takes all the current.

V<sub>DD</sub> - R<sub>D</sub> I<sub>SS</sub>

V<sub>out1</sub>

V<sub>out2</sub>

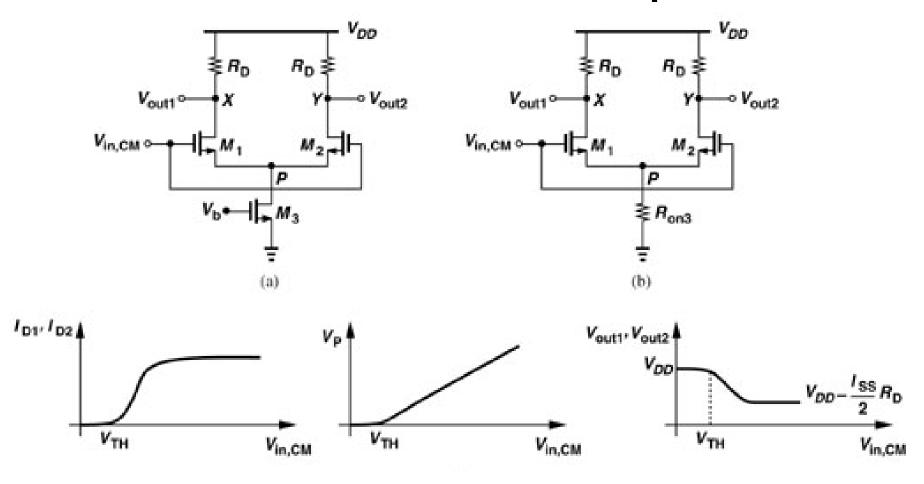

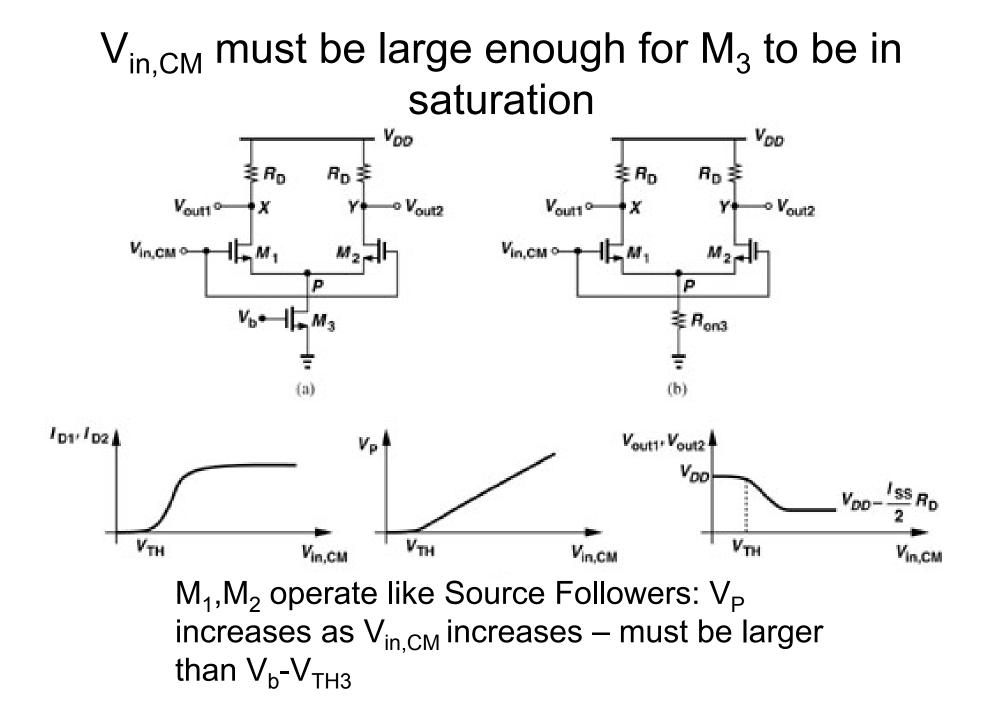

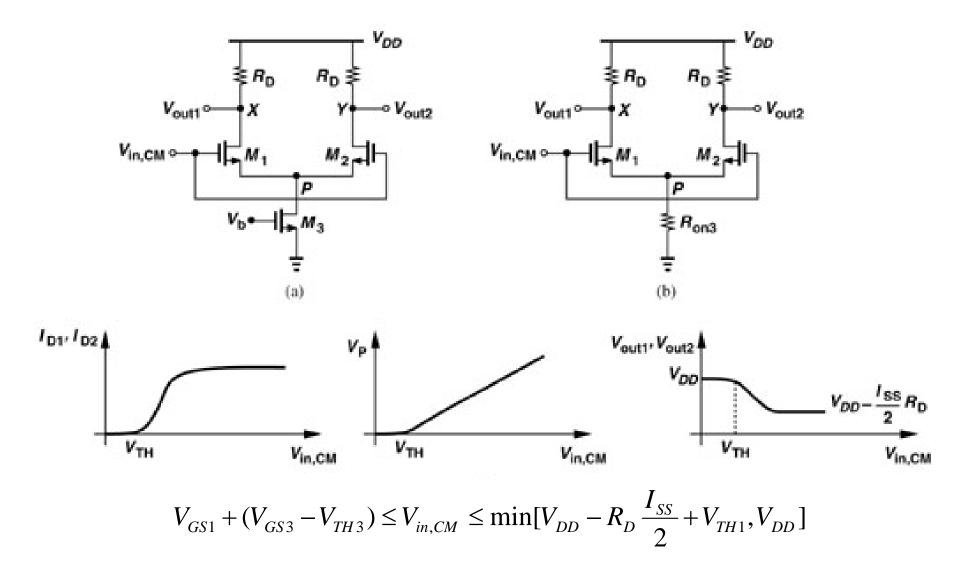

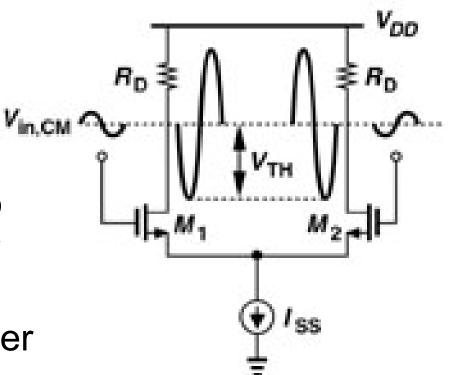

#### **Common-Mode Response**

Can  $V_{in,CM}$  be arbitrarily large or small?

$V_{in,CM}$  must not be too large to keep  $M_1$  and  $M_2$  from entering Triode Mode

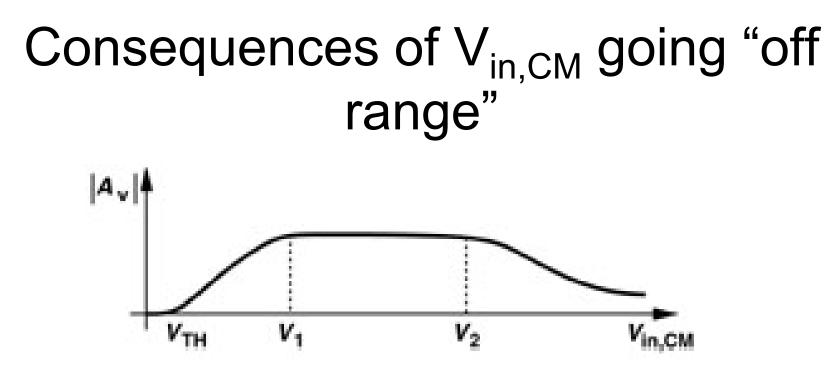

- As long as common mode voltage is within the permitted range, differential gain is almost insensitive to it.

- Once too small or too large gain falls off.

## Common-Mode Input vs. Output Swing Tradeoff

Each drain voltage can go as high as  $V_{DD}$  and as low as  $V_{in,CM}$ - $V_{TH}$ . The larger  $V_{in,CM}$  the smaller the swing.

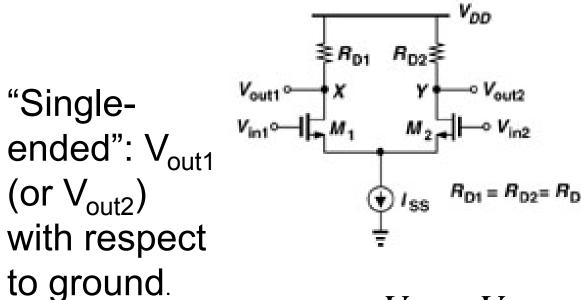

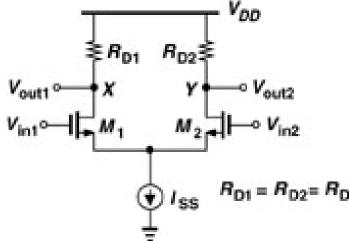

## Two types of Differential Gains

$$A_{v}(diff) = \frac{V_{out1} - V_{out2}}{V_{in1} - V_{in2}} = ?$$

$$A_{v}(S.E.) = \frac{V_{out1}}{V_{in1} - V_{in2}} = ?$$

#### **Current Division Mechanism**

Calculate  $I_{D1}$  and  $I_{D2}$  in terms of  $V_{in1}$  and  $V_{in2}$ , assuming the circuit is symmetric,  $M_1$  and  $M_2$  are saturated, and  $\lambda$ =0.

Since the voltage at node P is equal to  $V_P = V_{in1} - V_{GS1} = V_{in2} - V_{GS2}$ ,

$$V_{GS} = \sqrt{\frac{2I_D}{k_n' \frac{W}{L}}} + V_{TH}$$

$V_{in1}-V_{in2}=V_{GS1}-V_{GS2}$

#### **Current Division Mechanism**

Given the inputs and I<sub>SS</sub>: Solve two equations with two unknowns for the transistor currents:

$$V_{in1} - V_{in2} = \sqrt{\frac{2I_{D1}}{k_n'\frac{W}{L}}} - \sqrt{\frac{2I_{D2}}{k_n'\frac{W}{L}}}$$

$$I_{SS} = I_{D1} + I_{D2}$$

## **CMOS Differential Amplifiers**

Small-Signal Differential Gain-L16

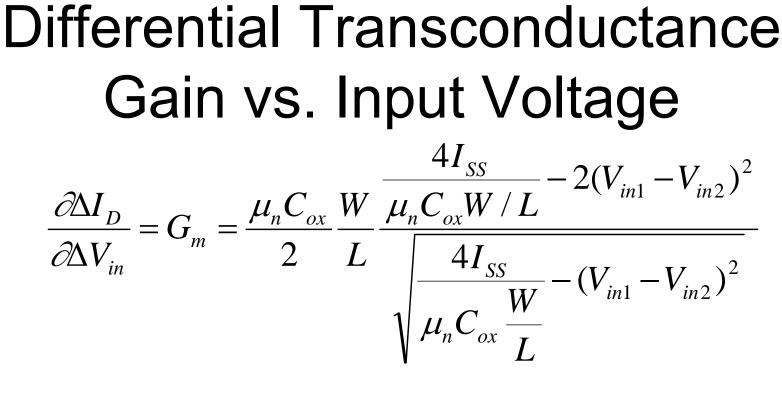

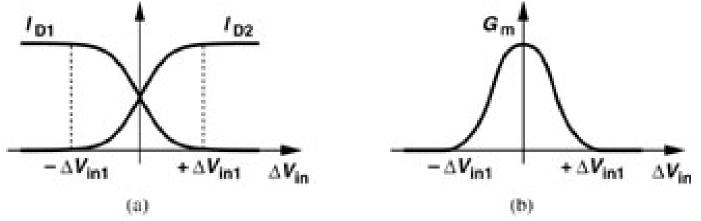

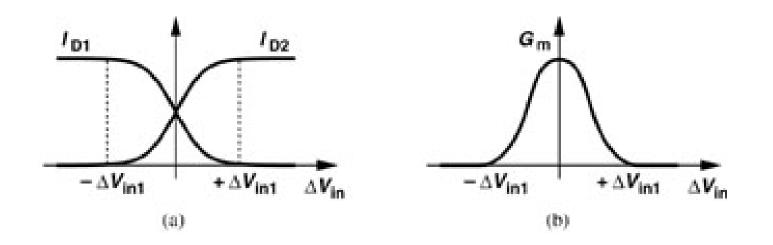

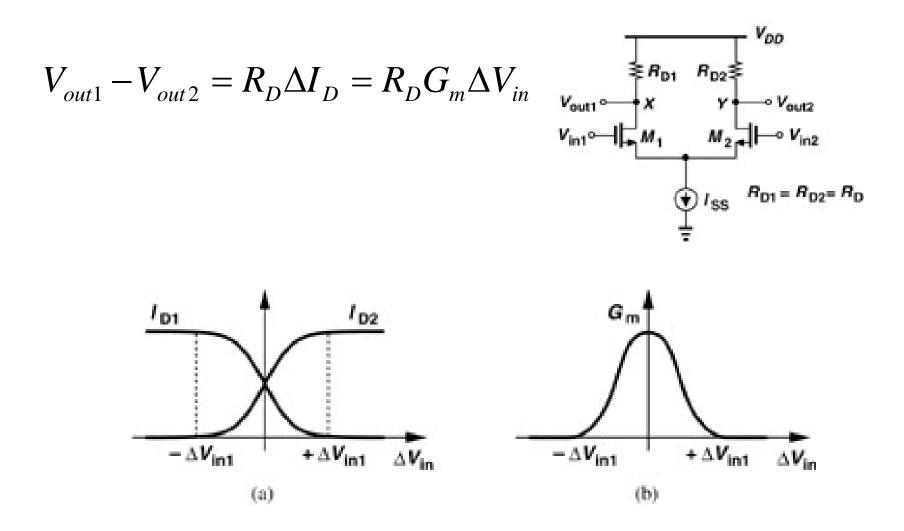

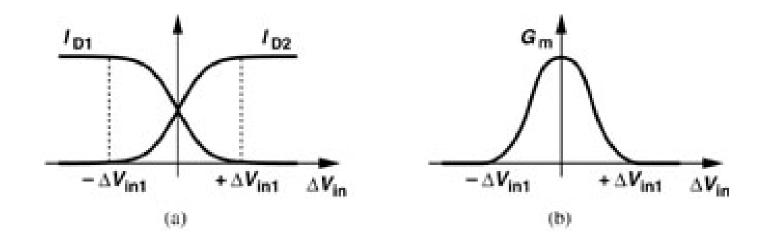

#### **Current Difference Properties**

Even though each current is an even function of its respective gatesource voltage, the current difference is an odd function of the input voltage difference

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in1} - V_{in2}) \sqrt{\frac{4I_{SS}}{\mu_n C_{OX} \frac{W}{L}} - (V_{in1} - V_{in2})^2}$$

Maximum Differential Transconductance Gain Occurs at  $\Delta V_{in}=0$

$$G_{m,\max} = \sqrt{\mu_n C_{ox} \left(\frac{W}{L}\right)} I_{SS}$$

#### **Differential Voltage Gain**

#### Differential Voltage Gain near $\Delta V_{in} = 0$

$$|A_{V}| = \frac{\Delta V_{out}}{\Delta V_{in}} = G_{m,\max}R_{D} = \sqrt{\mu_{n}C_{ox}\frac{W}{L}I_{SS}R_{D}}$$

## Differential Transconductance Gain Falls to Zero at $\Delta V_{in} = \Delta V_{in1}$

$$\Delta V_{in1} = \sqrt{\frac{2I_{SS}}{\mu_n C_{ox}} \frac{W}{L}}$$

#### **Current Difference Properties**

It appears as if  $\Delta I_D$  also becomes zero at  $\Delta V_{in2} = (4I_{SS}/(\mu_n C_{OX}W/L))^{1/2}$

But this is incorrect.

$\Delta V_{in2} > \Delta V_{in1}$  at which a total current stealing occurs.

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in1} - V_{in2}) \sqrt{\frac{4I_{SS}}{\mu_n C_{OX} \frac{W}{L}} - (V_{in1} - V_{in2})^2}$$

$\Delta V_{in} = \Delta V_{in1}$  is the maximum differential input that the amplifier can "handle"

$$\Delta V_{in1} = \sqrt{\frac{2I_{SS}}{\mu_n C_{ox} \frac{W}{L}}}$$

Also note that at  $\Delta V_{in}$ =0 each transistor carries a current of  $I_{SS}$ /2 and therefore :

$$(V_{GS} - V_{TH})_{1,2} = \sqrt{\frac{I_{SS}}{\mu_n C_{ox} \frac{W}{L}}}$$

Compare this equilibrium overdrive to the maximum differential input permitted:

$$\Delta V_{in1} = \sqrt{\frac{2I_{SS}}{\mu_n C_{ox} \frac{W}{L}}}$$

$$(V_{GS} - V_{TH})_{1,2} = \frac{\Delta V_{in1}}{\sqrt{2}}$$

It means that if we try to increase  $\Delta V_{in1}$ , for a given  $I_{SS}$ , we need larger overdrive voltage in each transistor, and this is accomplished by reducing W/L

$$(V_{GS} - V_{TH})_{1,2} = \sqrt{\frac{I_{SS}}{\mu_n C_{ox} \frac{W}{L}}} \qquad (V_{GS} - V_{TH})_{1,2} = \frac{\Delta V_{in1}}{\sqrt{2}}$$

$$\Delta V_{in1} = \sqrt{\frac{2I_{SS}}{\mu_n C_{ox}} \frac{W}{L}}$$

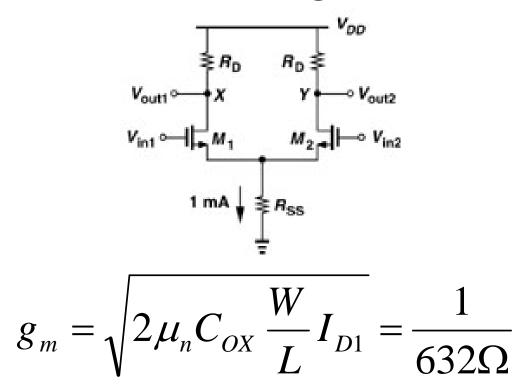

### Small-Signal Differential Voltage Gain

For |ΔV<sub>in</sub>|≈0 (sufficiently small) we have:

$$|A_{V}| = \frac{\Delta V_{out}}{\Delta V_{in}} = G_{m,\max}R_{D} = \sqrt{\mu_{n}C_{ox}\frac{W}{L}I_{SS}}R_{D} = g_{m}R_{D}$$

Where  $g_m$  is that of a NMOS with a current of  $I_{SS}/2$

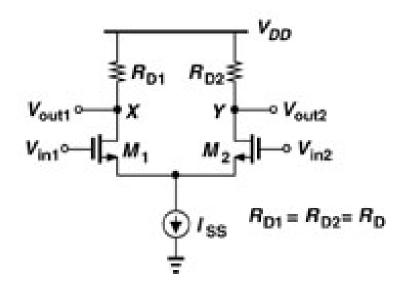

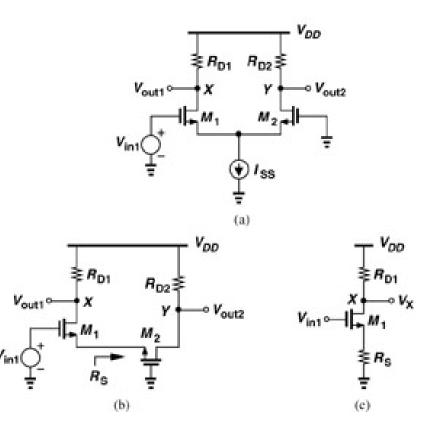

## Differential Gain: What does each input "see"?

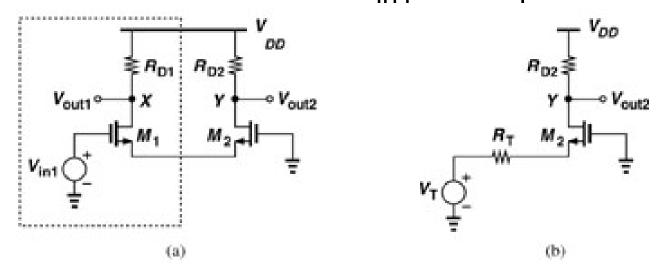

- By superposition let's short V<sub>in2</sub> to ground and see the effect of V<sub>in1</sub>:

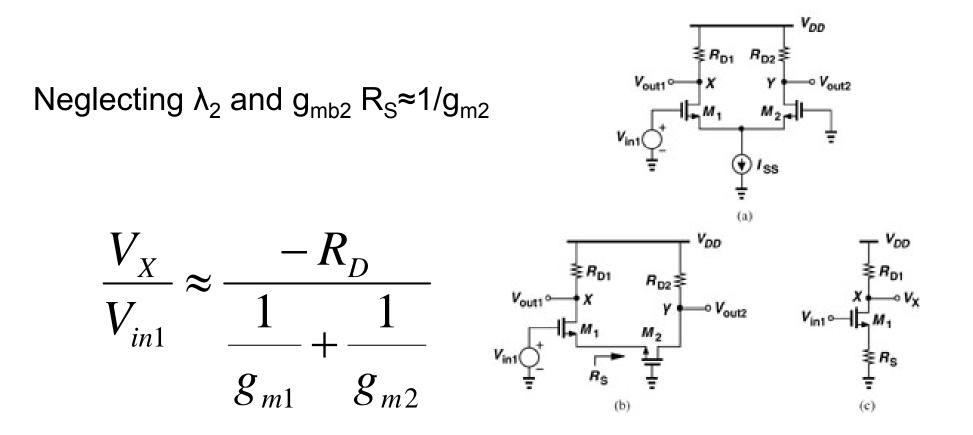

- The effect of  $V_{in1}$  on  $V_X$ is the same as that of a CS amplifier (degenerated by the resistance seen looking into the source of  $M_2$ ) on  $V_D$

#### Differential Gain: Effect of $V_{in1}$ on $V_X$

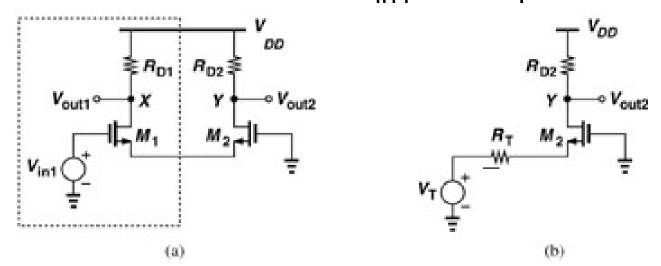

#### Differential Gain: Effect of V<sub>in1</sub> on V<sub>Y</sub>

The effect of  $V_{in1}$  on  $V_Y$  is the same as that of a Source Follower (M<sub>1</sub>) amplifier driving a Common-Gate amplifier (M<sub>2</sub>) V - V

$$V_T = V_{in1}$$

$$R_T = \frac{1}{g_{m1}}$$

#### Differential Gain: Effect of V<sub>in1</sub> on V<sub>Y</sub>

The effect of  $V_{in1}$  on  $V_Y$  is the same as that of a Source Follower (M<sub>1</sub>) amplifier driving a Common-Gate amplifier (M<sub>2</sub>)

#### $V_X-V_Y$ as function of $V_{in1}$ if $V_{in2}=0$

$$(V_X - V_Y)_{due_{to}_{V_{in1}}} = \frac{-2R_D}{\frac{1}{g_{m1}} + \frac{1}{g_{m2}}} V_{in1} = -g_m R_D V_{in1}$$

Because  $g_{m1}=g_{m2}=g_m$

## By Symmetry: $V_X - V_Y$ as function of $V_{in2}$ if $V_{in1} = 0$ $V_{out1} \circ V_{out2}$ $v_{out1} \circ V_{out2}$ $v_{in1} = V_{in1} = V_{out2}$ $v_{in1} = V_{in2} = V_{out2}$

$$(V_X - V_Y)_{due_{to_{V_{in2}}}} = \frac{2R_D}{\frac{1}{g_{m1}} + \frac{1}{g_{m2}}} V_{in2} = g_m R_D V_{in2}$$

#### $V_X$ - $V_Y$ as function of $V_{in2}$ and $V_{in1}$

$$(V_X - V_Y)_{due\_to\_both} = g_m R_D V_{in2} - g_m R_D V_{in1}$$

yielding the gain  $g_m R_D$  regardless where and how the inputs are applied

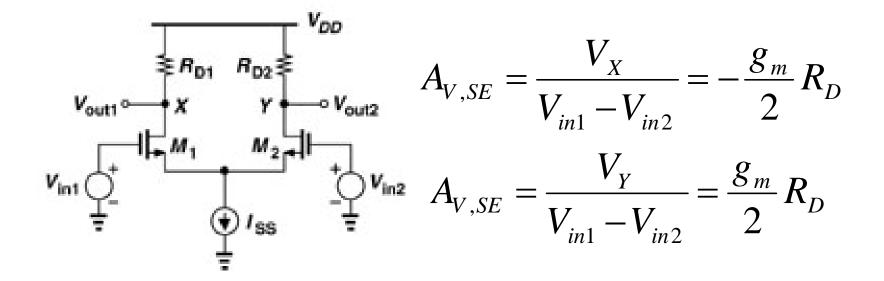

#### Single-ended Differential Voltage Gain

# Comparison: Differential voltage gain of a differential amplifier vs. voltage gain of a CS amplifier

- If the same current source  $I_{SS}$  drives the differential amplifier and the CS, each transistor of the differential amplifier has  $g_m$  which is  $1/\sqrt{2}$  of that of the CS transistor. Differential gain reduces by a factor of  $1/\sqrt{2}$ .

- If both amplifiers have the same W/L in each transistor and the same load, and we want the gain to be the same, then if we use  $I_{SS}$  at CS, we need to use  $2I_{SS}$  at the differential amplifier.

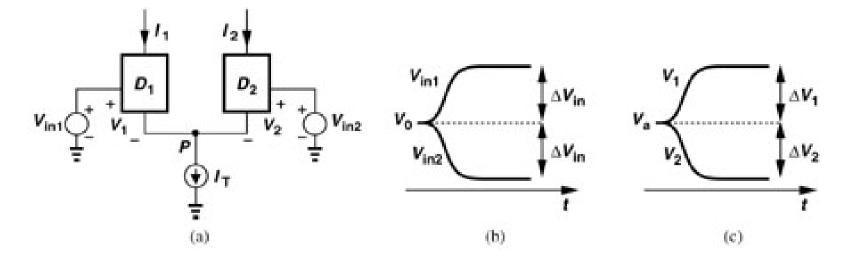

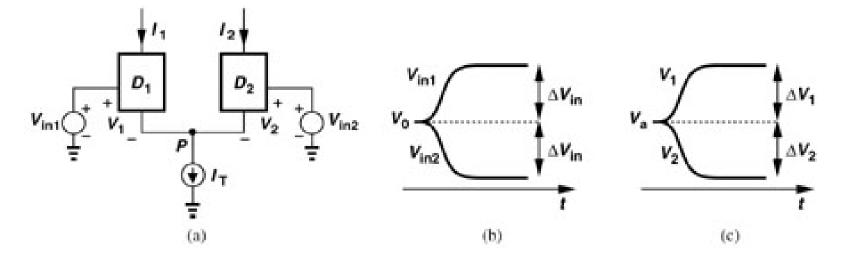

#### The "Virtual Ground" Concept

- In a symmetric device (as above), if inputs change antisymmetrically (one goes up by a certain amount, and the other goes down by the same amount), then V<sub>P</sub> does not change.

- For small-signal analysis point P becomes "virtual ground".

#### The "Virtual Ground" Concept

- Explanation: Consider the complete "Kirchhoff path"  $V_{in1} \rightarrow D_1 \rightarrow D_2 \rightarrow V_{in2}$ .

- By symmetry of the devices, and anti-symmetry of sources, using voltage-division argument, V<sub>P</sub> stays constant.

- See book (pp. 114-115) for 2-3 more explanations.

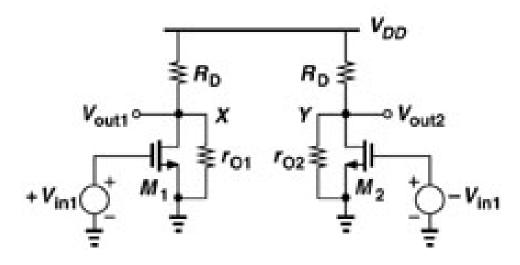

#### The "Half-Circuit" Concept

For small-signal analysis, because point P is "ground" (this is valid only if inputs are antisymmetric and devices are symmetric!), we can analyze each CS "half-circuit" separately.

#### Differential Gain with λ effect

- Based on the half-circuit concept, gain calculation is highly simplified. We get:

- $V_X/V_{in1} = -g_m(R_D||r_o) = V_Y/(-V_{in1})$

- $(V_X V_Y)/2V_{in1} = -g_m(R_D||r_o)$

In general  $V_{in1}$  and  $V_{in2}$  are arbitrary (not necessarily anti-symmetric): What do we do?

(c)

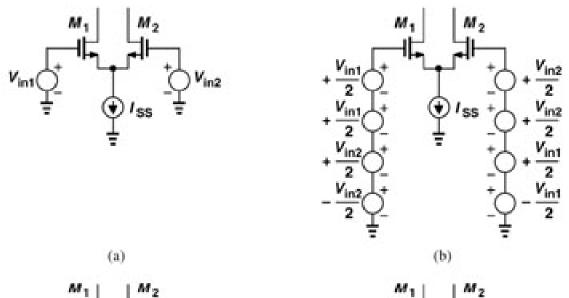

#### Analysis of Differential Amplifiers for arbitrary inputs

- As long as circuit operates more or less linearly, we use superposition of two analyses:

- Differential input analysis, using antisymmetric inputs derived from the difference between the inputs.

- Common-mode analysis, where an input equals to the average of both inputs is applied to both transistors.

#### **CMOS Differential Amplifiers**

Common-Mode Analysis –L17

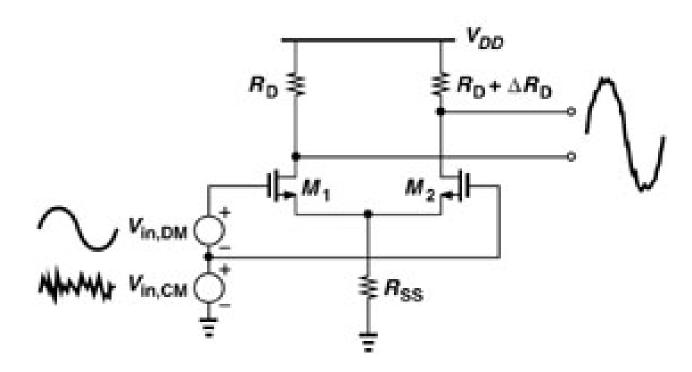

## Goal: No common-mode signal at amplifier's output

- If amplifier is not 100% symmetric, CM signals will not be fully cancelled out.

- If the DC current source (biasing the amplifier) is not ideal (that is, has a finite output resistance) then CM signal appears at each single-ended output.

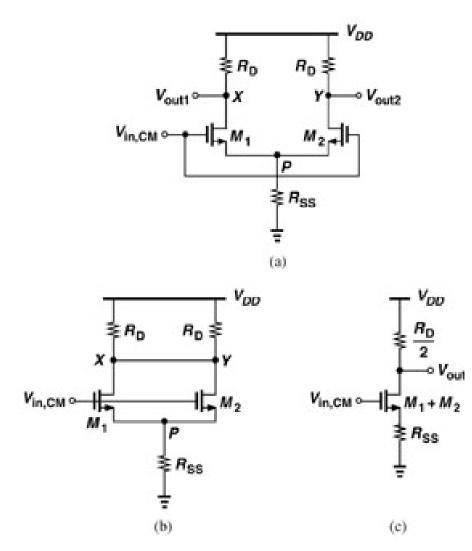

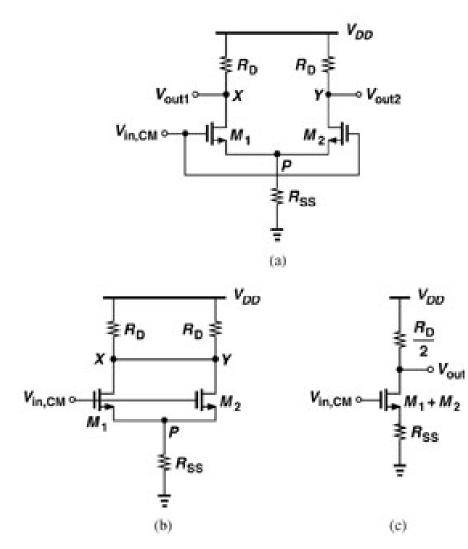

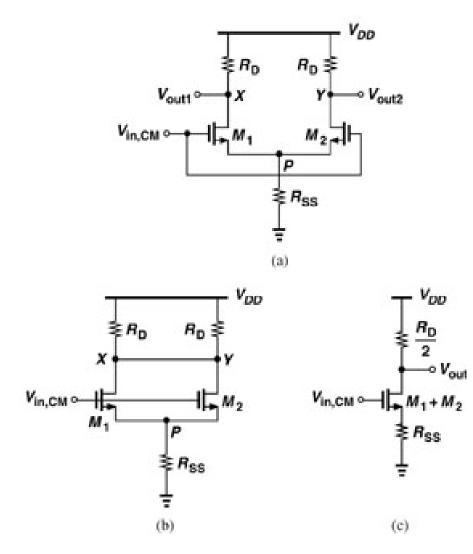

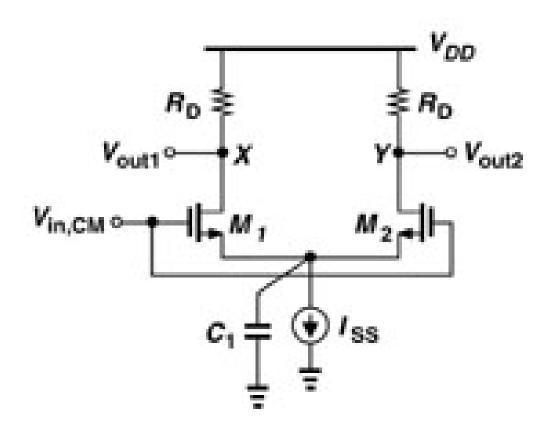

#### Single-ended Common-Mode Response of a symmetric amplifier

Consider a smallsignal analysis for the common-mode signal.

Current source is represented by its output resistance R<sub>SS</sub>

#### Single-ended Common-Mode Response of a symmetric amplifier

As  $V_{in,CM}$  changes so does  $V_{P}$ . As a result,  $I_{D}$  currents change, and  $V_{X}$  and  $V_{Y}$  change.

$V_X$ - $V_Y$  continues to be zero.

#### Single-ended Common-Mode Response of a symmetric amplifier

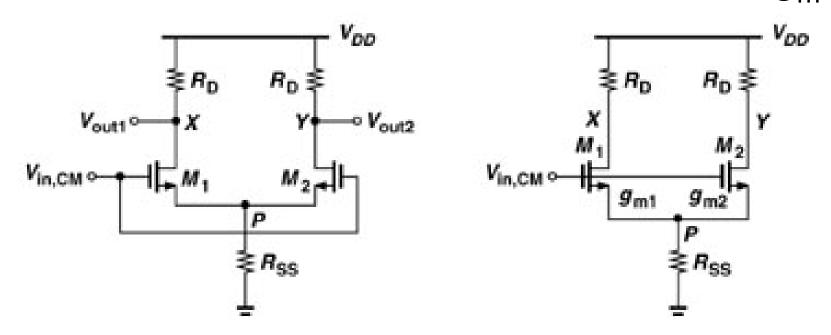

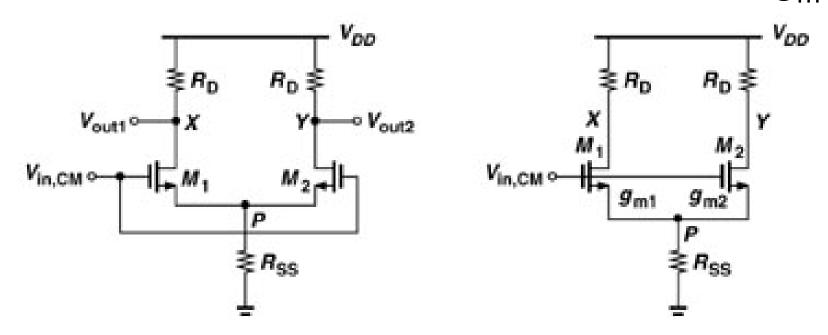

To find  $V_x$  as function of  $V_{in,CM}$  we may do a "half circuit analysis", splitting R<sub>SS</sub> into two parallel  $2R_{SS}$ resistors, or equivalently, connect transistors in parallel (as shown).

Single-ended Common-Mode Gain of a symmetric amplifier assuming  $\lambda$ =0 and  $\gamma$ =0

$$V_{,CM} = \frac{V_{out}}{V_{in,CM}} = \frac{V_X}{V_{in,CM}} = \frac{V_Y}{V_{in,CM}}$$

$$= -\frac{R_D/2}{1/(2g_m) + R_{SS}}$$

$$M_1 + M_2 \text{ has twice the width and bias current,}$$

therefore g<sub>m</sub> is doubled.

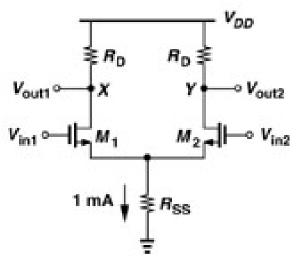

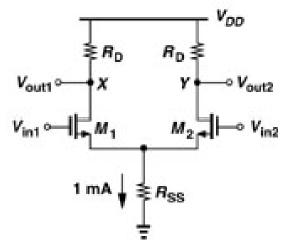

#### Most Primitive Differential Amplifier: Resistor in place of current source

- Example: Let  $V_{DD}=3V$ ,  $(W/L)_1=(W/L)_2=25/0.5$

- $\mu_n C_{OX}$ =50 $\mu$ A/V<sup>2</sup>, V<sub>TH</sub>=0.6V,  $\lambda$ =0,  $\gamma$ =0, R<sub>SS</sub>=500 $\Omega$

- Because  $I_{D1}=I_{D2}=0.5$ mA, we have:

$$V_{GS1} = V_{GS2} = \sqrt{\frac{2I_{D1}}{\mu_n C_{OX} \frac{W}{L}}} + V_{TH} = 1.23V$$

#### "Resistor current source" example

$$V_{GS1} = V_{GS2} = \sqrt{\frac{2I_{D1}}{\mu_n C_{OX} \frac{W}{L}}} + V_{TH} = 1.23V$$

- Also:  $V_S = I_{ss}R_{SS} = 0.5V$

- Bias voltage at gates  $V_{in,CM} = V_{GS1} + V_S = 1.73V$

- This voltage creates the necessary 0.5mA current in each of the transistors.

#### "Resistor current source" example – differential gain design

If  $R_D$ =3.16K $\Omega$  then differential voltage gain =  $g_m R_D$ =5

"Resistor current source" example – with such  $R_D$  are transistors in Saturation?

$$V_{out1} = V_{out2} = V_{DD} - I_D R_D = 1.42V > V_{in,CM} - V_{TH}$$

=1.73 - 0.6 = 1.13V by 290mV (the overdrive)

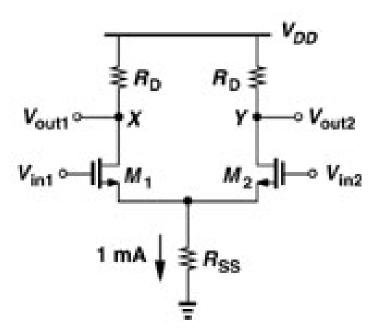

#### "Resistor current source" example – Common-Mode Response

If  $V_{in,CM}$  increases by 50mV, what will happen to each output?

#### "Resistor current source" example – Common-Mode Response

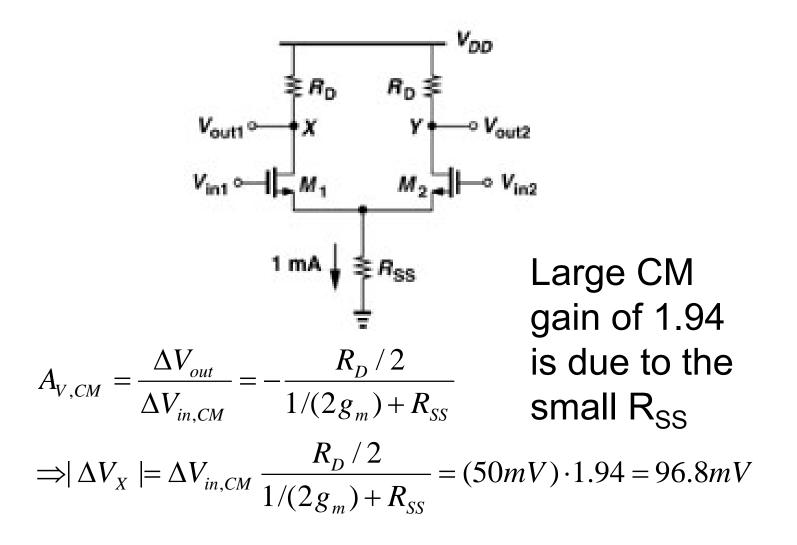

### Common-Mode Response with asymmetric $R_D$ assuming $\lambda=0$

$R_{SS}$  above represents the current source – need large  $R_{SS}$

### Common-Mode Response with asymmetric $R_D$

CM input noise corrupts the amplified differential signal, because of the asymmetry

For high-frequency Common-Mode input need to take into account parasitic capacitance effects, even if  $R_{SS}$  is large.  $C_1$  is contributed by  $M_1, M_2$  and  $I_{SS}$  and contributes to the impedance "seen" by the

CM signal.

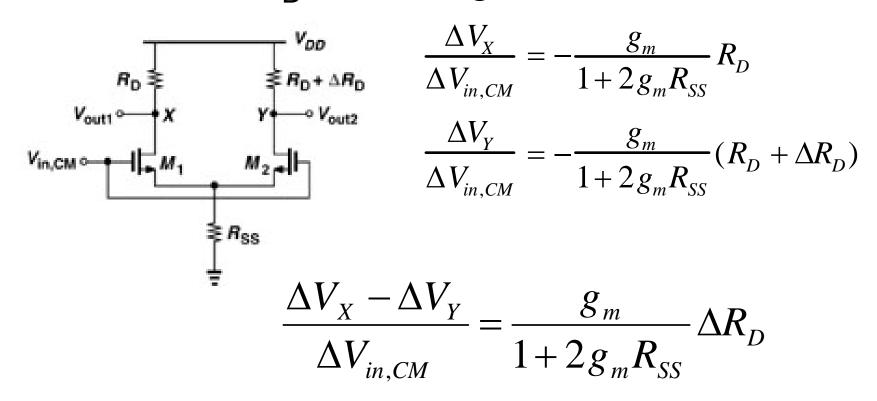

Mismatches in W/L,  $V_{TH}$  and other transistor parameters all translate to mismatches in  $g_m$

$I_{D1} = g_{m1}^{(a)} (V_{in,CM} - V_P)$   $I_{D2} = g_{m2} (V_{in,CM} - V_P)$  analysis  $\Rightarrow (g_{m1} + g_{m2}) (V_{in,CM} - V_P) R_{SS} = V_P$

Mismatches in W/L,  $V_{TH}$  and other transistor parameters all translate to mismatches in  $g_m$

$$(g_{m1} + g_{m2})(V_{in,CM} - V_P)R_{SS} = V_P$$

$$\Rightarrow V_P = \frac{(g_{m1} + g_{m2})R_{SS}}{(g_{m1} + g_{m2})R_{SS} + 1}V_{in,CM}$$

$$V_X = -g_{m1}(V_{in,CM} - V_P)R_D$$

$$V_Y = -g_{m2}(V_{in,CM} - V_P)R_D$$

Mismatches in W/L,  $V_{TH}$  and other transistor parameters all translate to mismatches in  $g_m$

#### **Common-Mode Gains**

- We have seen two types of commonmode gain:

- A<sub>V,CM</sub>: Single-ended output due to CM signal.

- A<sub>V,CM-DM</sub> : Differential output due to CM signal.

$$A_{V,CM} = \frac{V_X}{V_{in,CM}} = \frac{V_Y}{V_{in,CM}}$$

$$A_{V,CM-DM} = \frac{V_X - V_Y}{V_{in,CM}}$$

## Common-Mode Rejection Ratio (CMRR) Definitions

$$CMRR = CMRR_{SE} = \left|\frac{A_{DM}}{A_{CM}}\right|$$

$$CMRR = CMRR_{diff} = \left|\frac{A_{DM}}{A_{CM-DM}}\right|$$

In both cases we want CMRR to be as large as possible, and it translates into small matching errors and  $R_{SS}$  as large as possible

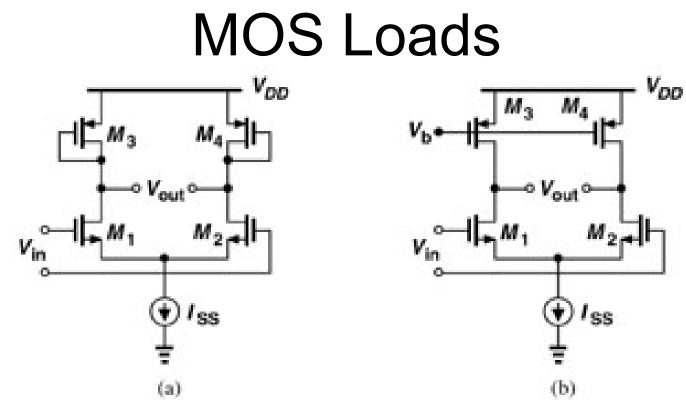

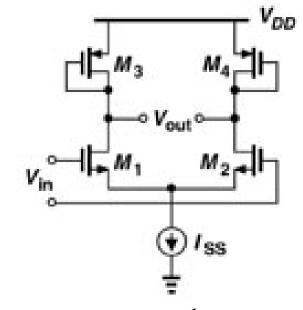

#### **CMOS Differential Amplifiers**

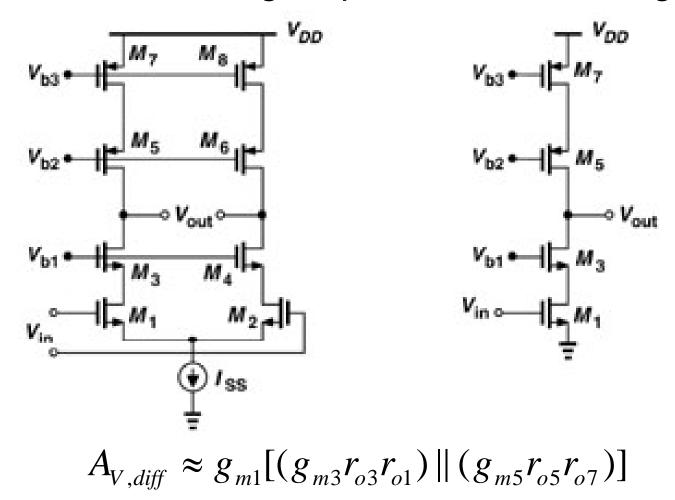

MOS Loads – L18

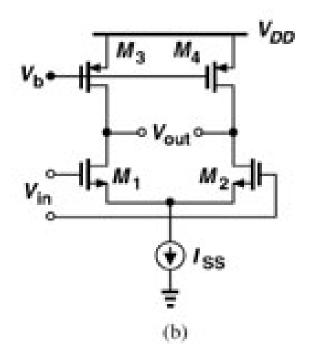

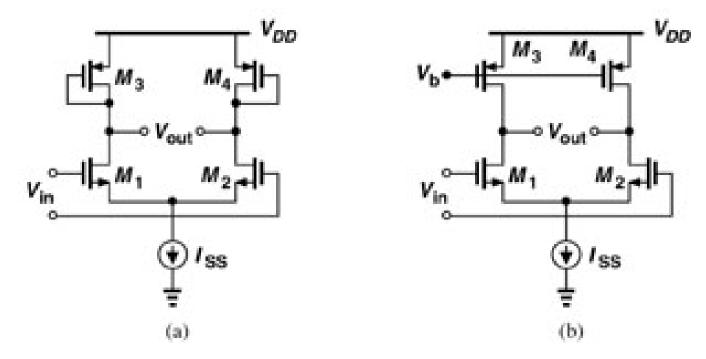

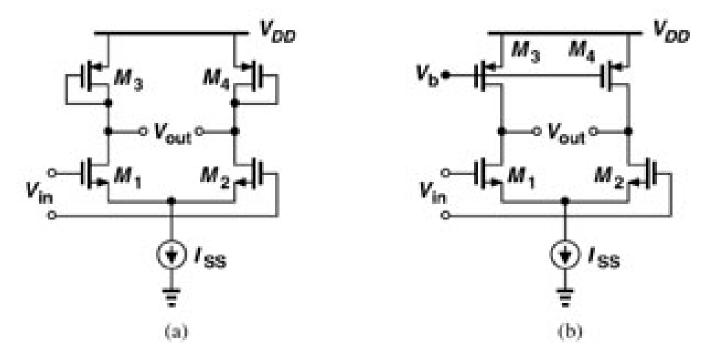

- (a) Diode-connected load

- (b) Current-Source load

#### MOS Loads: Analysis Method

- Differential Analysis: Use half-circuit method, with source node at virtual ground.

- Common-Mode Analysis: Again use half-circuit method, with appropriate accommodation for parallel transistors, and for R<sub>SS.</sub>

#### MOS Loads: Differential Gain Formulas

$$A_{V,diff} = -g_{mN} (g_{mP}^{-1} || r_{oN} || r_{oP})$$

$$\approx -\frac{g_{mN}}{g_{mP}} = -\sqrt{\frac{\mu_n (W/L)_N}{\mu_p (W/L)_P}}$$

$$A_{V,diff} = -g_{mN}(r_{oN} \parallel r_{oP})$$

#### Problems with Diode-connected MOS Loads

- Tradeoff among output voltage swing, voltage gain and CM input range:

- In order to achieve high gain, (W/L)<sub>P</sub> must be decrease, thereby increasing |V<sub>GSP</sub>-V<sub>THP</sub>| and lowering the CM level at nodes X and Y.

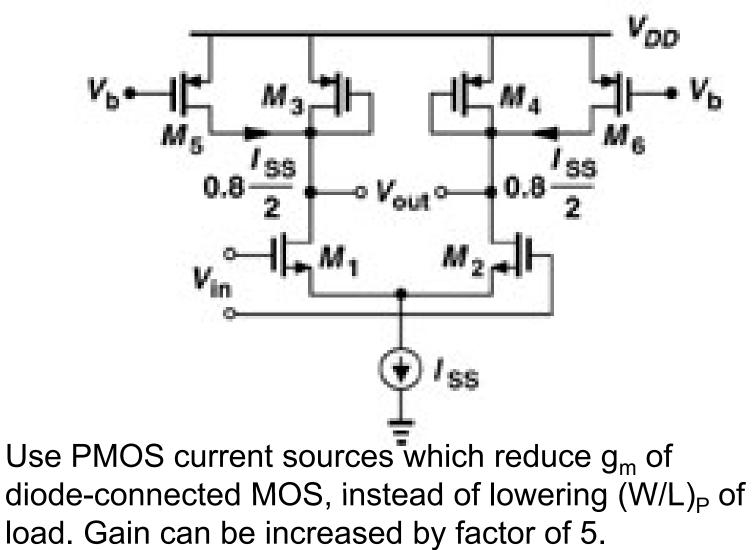

Overcoming Diode-connected Load swing problem for higher gains:

#### Problems with Current-Source MOS Loads

In sub-micron technologies, it's hard to obtain differential gains higher than 10-20.

#### Solution to low-gain problem: Cascoding

### **CMOS Differential Amplifiers**

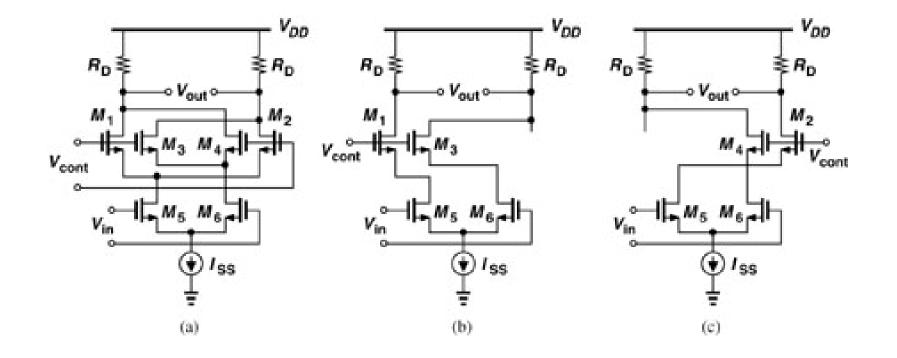

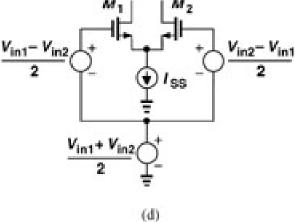

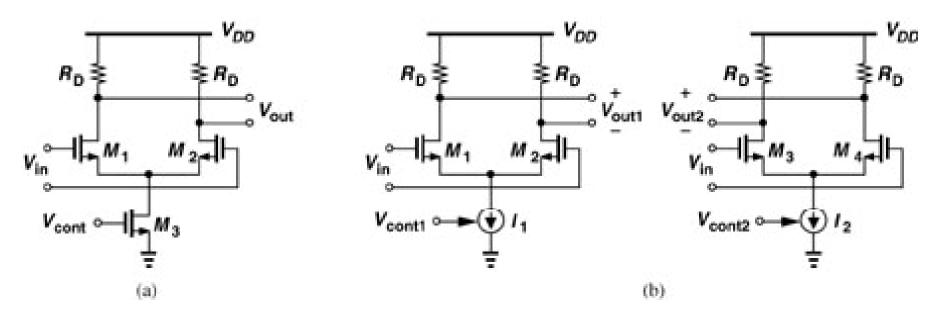

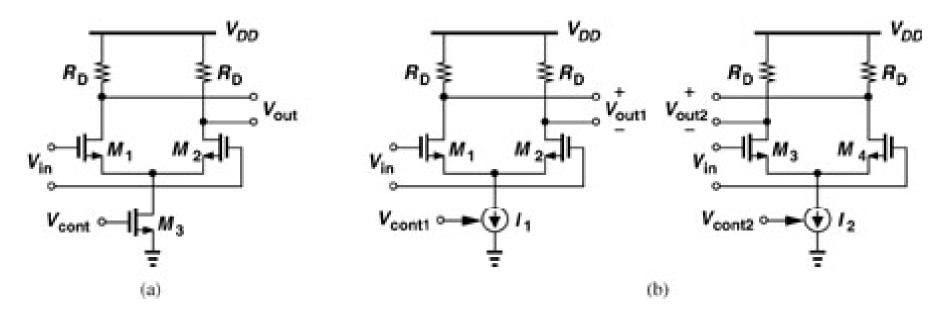

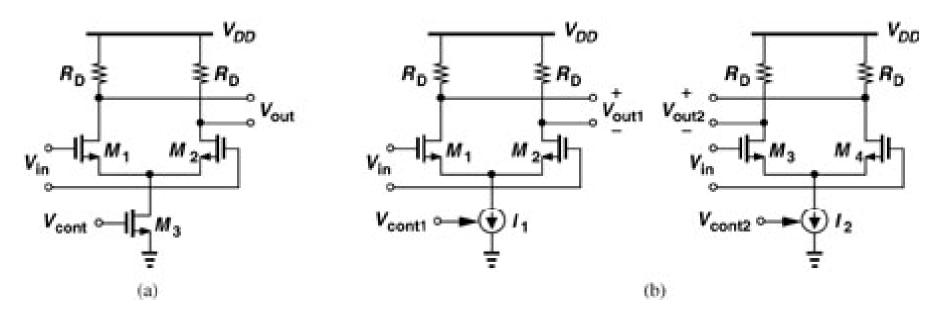

Gilbert Cell-L19

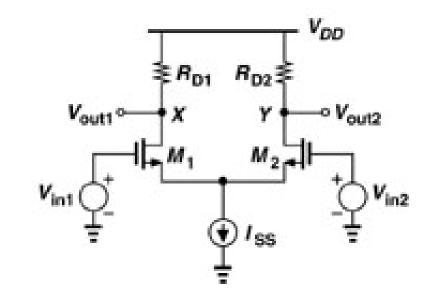

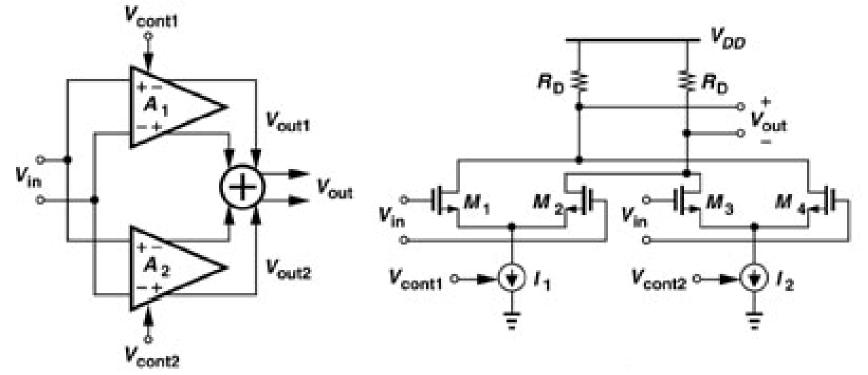

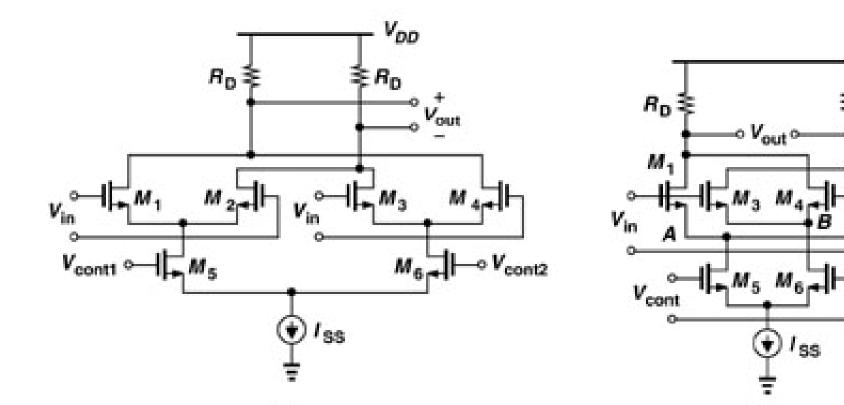

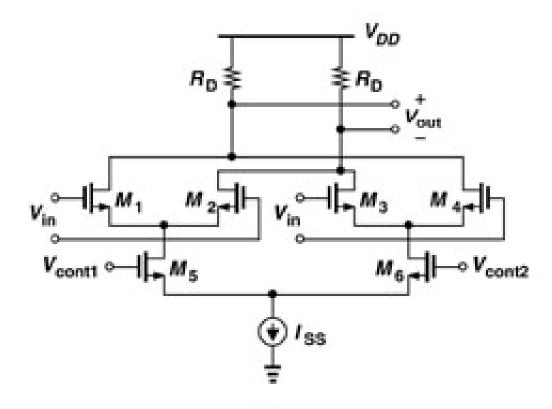

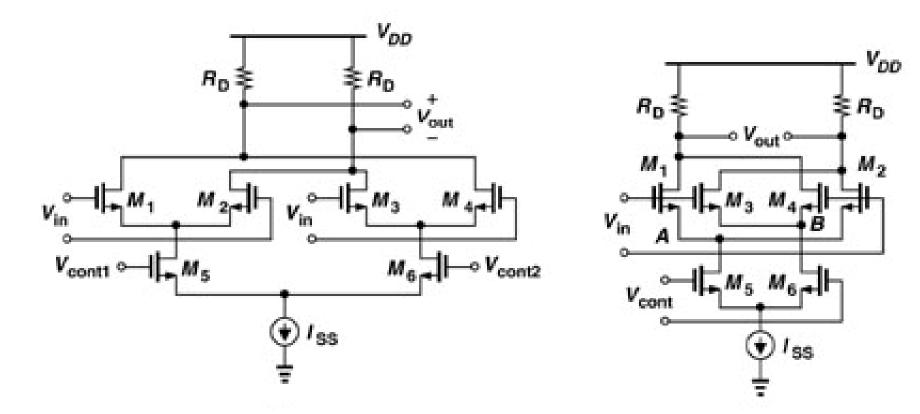

(a)is a VGA (Variable-Gain Amplifier). V<sub>cont</sub> determines I<sub>ss</sub>, which determines the differential gain.

Gain may be varied from 0 to some maximum value.

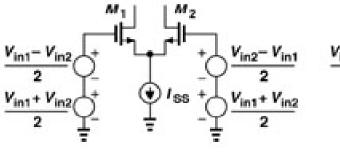

What do we do if we want to vary the gain continuously from some negative value to some positive value?

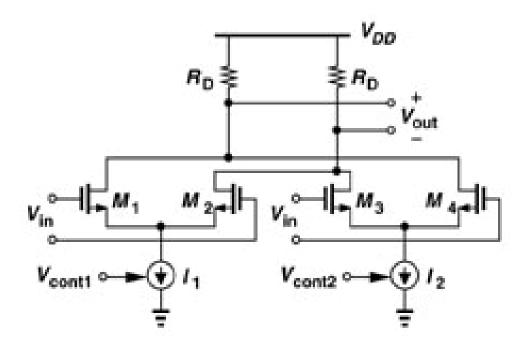

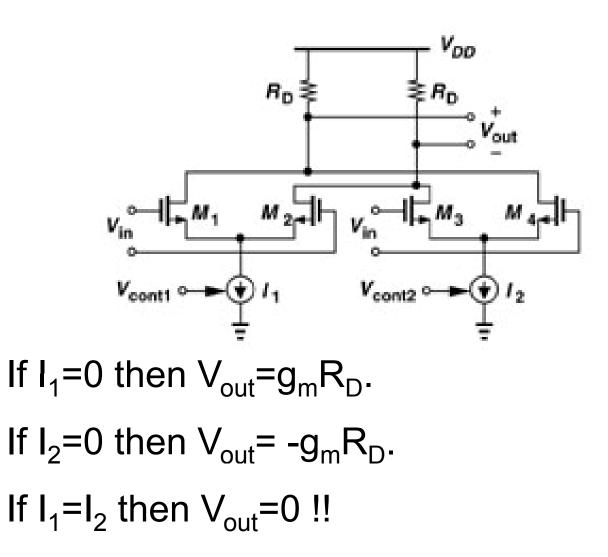

In circuits (b) the two amplifiers have opposite differential gain simply by interchanging the order of output subtraction)

If  $I_1 = I_2$  then  $V_{out,1}/V_{in} = -g_m R_D = -V_{out,2}/V_{in}$

If we vary  $I_1$  and  $I_2$  in opposite directions, the gains will follow along these directions.

How should we combine the two differential outputs?

# How to combine the differential outputs?

On the left, we conceptually see the two voltages ADDED UP.

Gains  $A_1$  and  $A_2$  are voltage controlled.

How to combine the differential outputs? Math will show the implementation method.

Does it work as intended? Can gain be varied positively as well as negatively?

Next phase in the conceptual development: Do we really need two separate control signals??

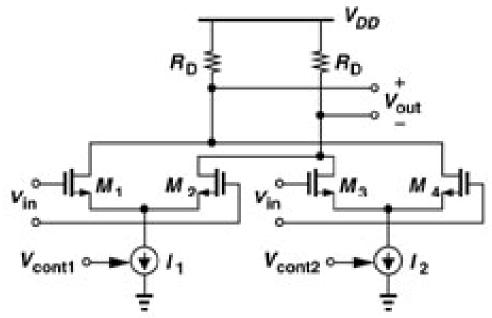

Recall the basic structure of a differential amplifier: The inputs difference cause one of the MOS currents to go up, and at the same time the current of the opposite MOS goes down by the same amount  $\rightarrow$  Let I<sub>1</sub>, I<sub>2</sub> come from diff. amp.

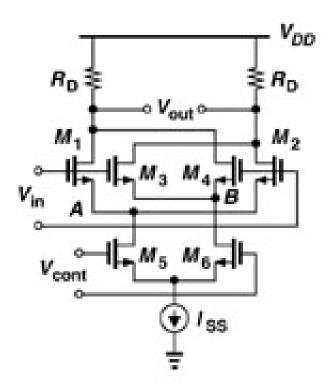

### Gilbert Cell

$V_{DD}$

$R_{\rm D}$

$M_2$

Left: If  $|V_{cont1} - V_{cont2}|$  is large we have "current stealing", and then gain is either most positive or most negative.

### Gilbert Cell

**Right: Actual Implementation**

### **Gilbert Cell**

$V_{OUT} = k V_{in} V_{cont}$

## Applications of Gilbert Cell

- Analog Multiplier

- Mixer

- Phase Detector

- AM Modulation

- VGA: Variable-gain amplifier

- AGC (Automatic Gain Control)

It's a versatile general-purpose tool

# Can switch input and control signals!