#### Lecture 11:

# RIE of Silicon - Poly-silicon and Bulk-silicon-

Dong-il "Dan" Cho

School of Electrical Engineering and Computer Science, Seoul National University Nano/Micro Systems & Controls Laboratory

> Email: dicho@snu.ac.kr URL: http://nml.snu.ac.kr

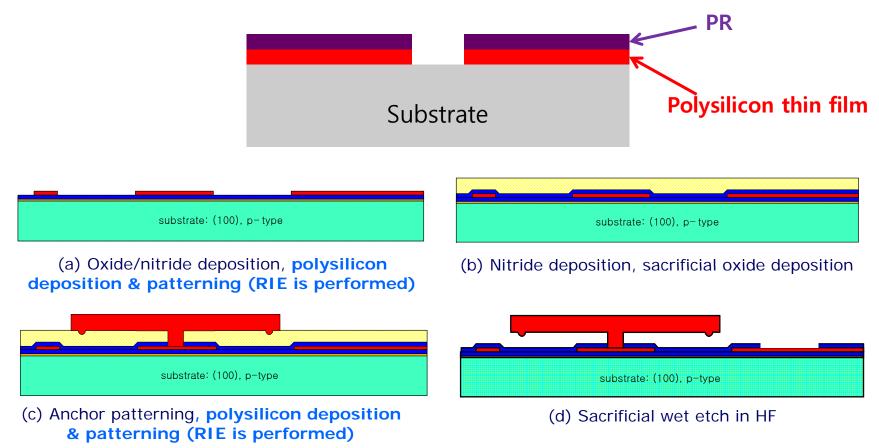

#### **RIE in Thin Film Etching (1)**

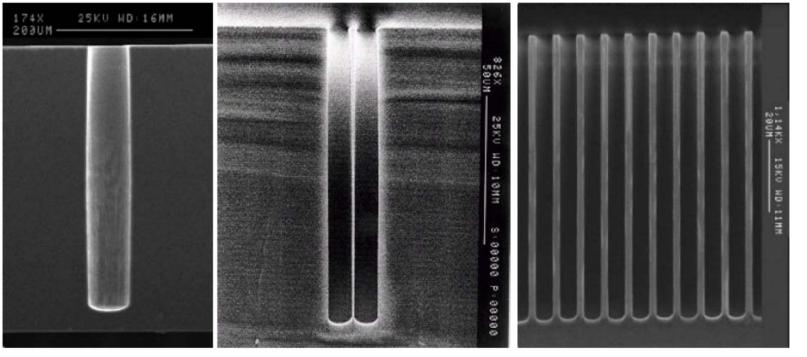

Thin poly silicon etch in surface micromachining

- Usually, photo resist is used for etch mask material

Nano/Micro Systems & Controls Lab.

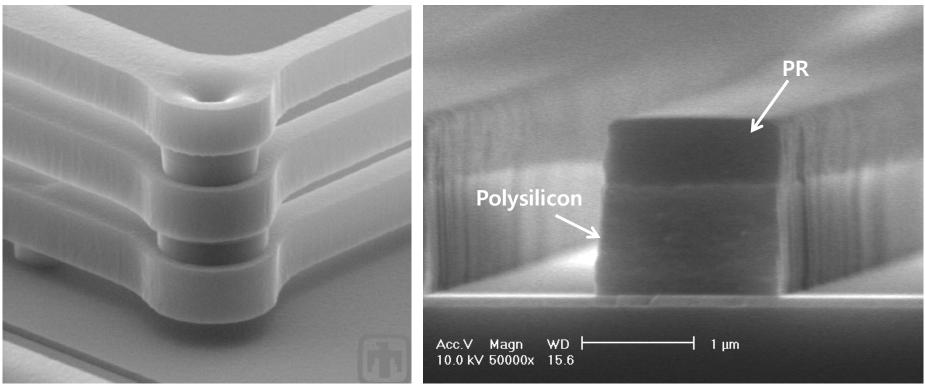

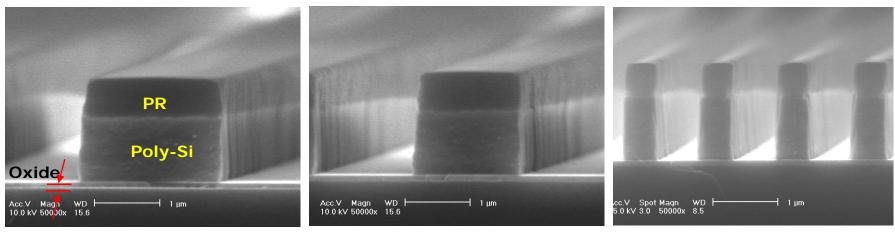

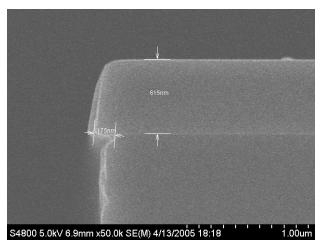

#### **RIE in Thin Film Etching (2)**

Detailed view of the multi-level polysilicon that are a critical part of a microengine

Detailed view of polysilicon beam with PR mask after RIE

Nano/Micro Systems & Controls Lab.

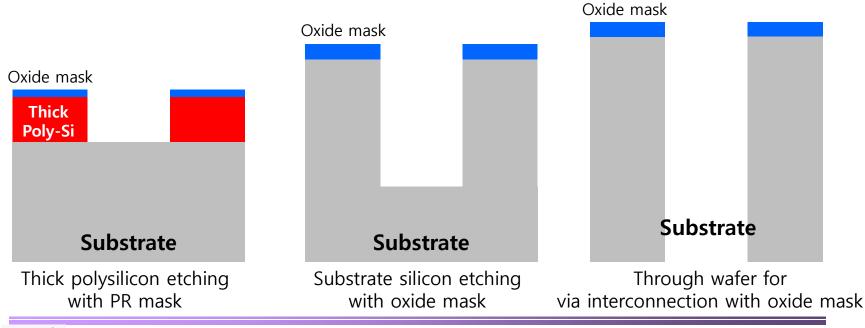

#### **RIE in Bulk Etching (1)**

- Thick polysilicon, epipoly silicon, and bulk silicon etch

- Selectively remove significant amounts of silicon from a substrate

- Maximum etch thickness is several hundred micro meters.

- Usually, oxide hard mask and photo resist are used for etch mask material

(When etch thickness is less then 10  $\mu$ m, photo resist is used)

Dong-il "Dan" Cho

Nano/Micro Systems & Controls Lab.

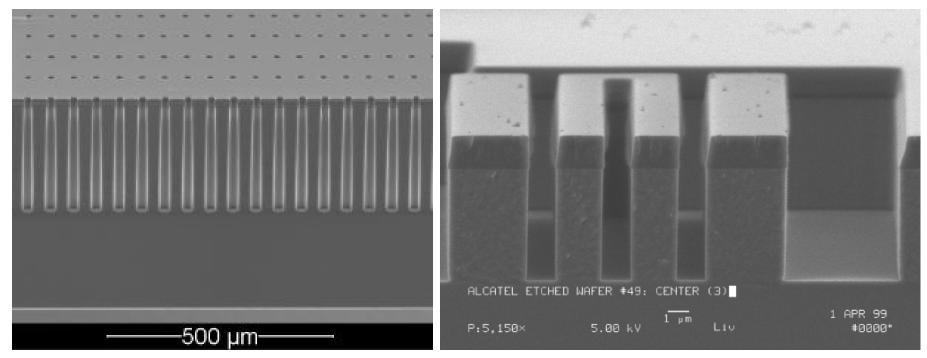

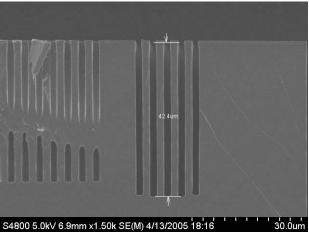

#### **RIE in Bulk Etching(2)**

DRIE for through wafer holes (400 μm deep 50x50 μm<sup>2</sup> holes) 6 µm beam poly etch (before resist strip).

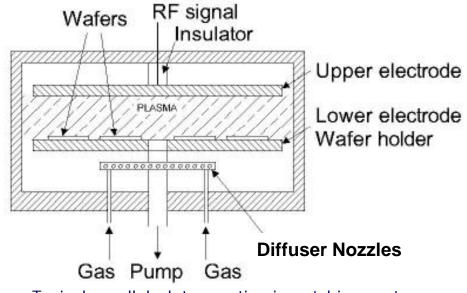

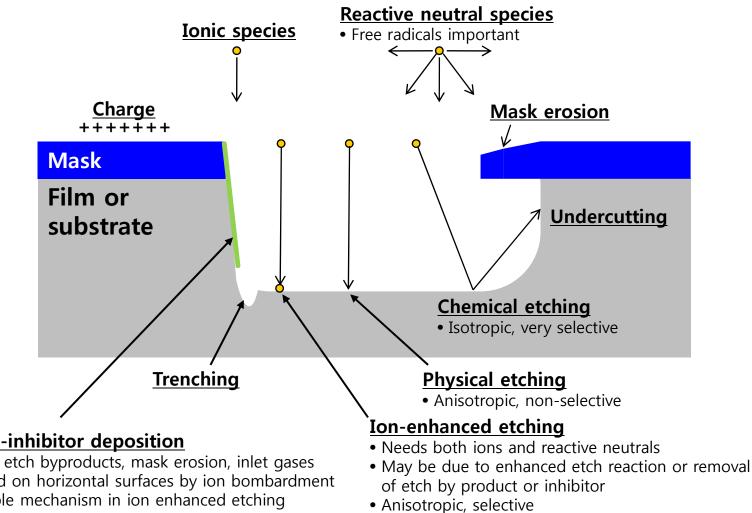

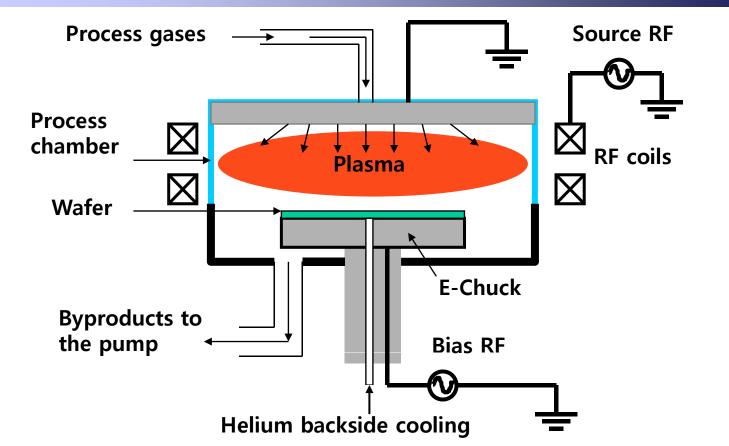

#### **RIE Principles (1)**

- RIE: Reactive Ion Etching

- Process in which chemical etching is accompanied by ionic bombardment

- Combination of physical and chemical etching

- Faster and simpler etching in a few cases

- Anisotropic etching

Typical parallel-plate reactive ion etching system

Nano/Micro Systems & Controls Lab.

#### **RIE Principles (2)**

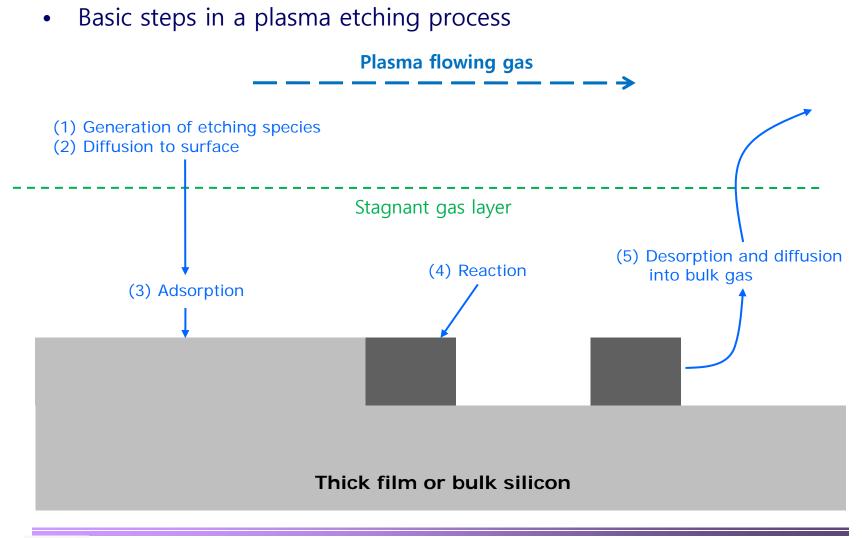

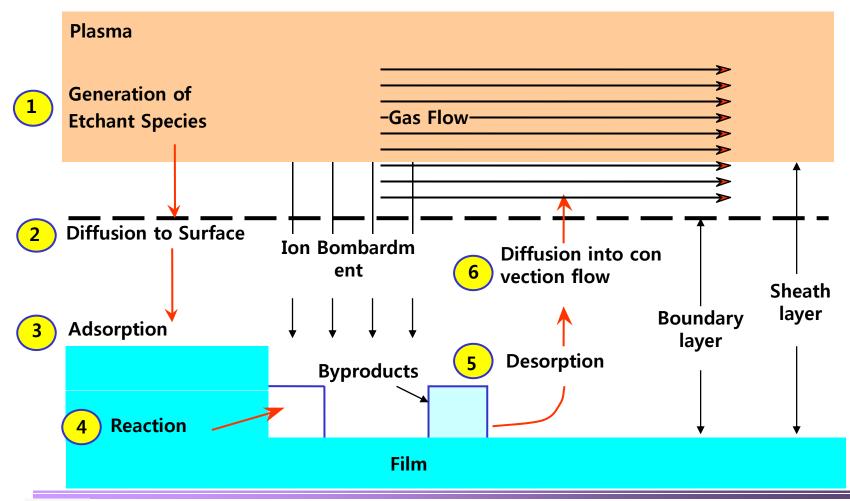

Basic steps in a plasma etching process

Nano/Micro Systems & Controls Lab.

#### **RIE Principles (3)**

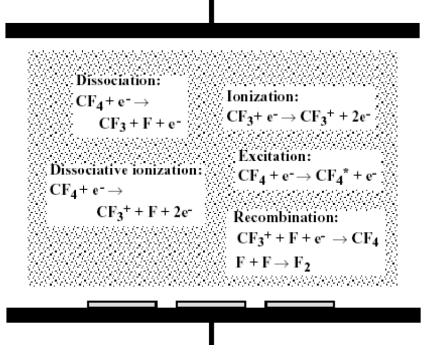

- Typical reactions and species present in a plasma used for plasma etching

- Typically there are about  $10^{15}$  cm<sup>-3</sup> neutral species (1 to 10%of which may be free radicals) and 10<sup>8</sup>- 10<sup>12</sup> cm<sup>-3</sup> ions and electrons.

Nano/Micro Systems & Controls Lab.

#### **RIE Principles (4)**

| $\sim$               | Plasma Etching          |                                       | Reactive Etching                     |                                     | Physical Etching                     |                                |  |

|----------------------|-------------------------|---------------------------------------|--------------------------------------|-------------------------------------|--------------------------------------|--------------------------------|--|

|                      | Barrel Reactor          | Planar Reactor                        | Ion                                  | Ion Beam                            | Sputtering                           | Ion Beam Milling               |  |

| Substrate Location   | Surrounded<br>by plasma | On grounded<br>electrode in<br>Plasma | On powered<br>electrode in<br>plasma | In beam, remote<br>from plasma      | On powered<br>electrode in<br>plasma | In beam, remote<br>from plasma |  |

| Pressure (torr)      | 10 <sup>-1</sup> ~ 1    | 10 <sup>-1</sup> ~ 1                  | 10 <sup>-2</sup> ~ 10 <sup>-1</sup>  | 10 <sup>-4</sup> ~ 10 <sup>-3</sup> | 10 <sup>-5</sup> ~ 10 <sup>-3</sup>  | 10-4                           |  |

| Ion energy(eV)       | 0                       | 1 ~ 100                               | 100 ~ 1000                           | 100 ~ 1000                          | 100 ~ 1000                           | 100 ~ 1000                     |  |

| Active Species       | Atoms.<br>Radicals      | Atoms, radicals, reactive ions        | Radicals, reactive ions              | Reactive ions                       | Ar+ ions                             | Ar+ ions                       |  |

| Products             | Volatile                | Volatile                              | Volatile                             | Volatile                            | Nonvolatile                          | Nonvolatile                    |  |

| Mechanism            | Chemical                | Chemical/<br>Chemical-Physical        | Chemical/<br>Physical                | Chemical/<br>Physical               | Physical                             | Physical                       |  |

| Etch Profile         | Isotropic               | Isotropic/<br>Anisotropic             | Isotropic/<br>Anisotropic            | Anisotropic Anisotropic             |                                      | Anisotropic                    |  |

| Selectivity          | 30 : 1 – 10 : 1         | 10 : 1 – 5 : 1                        | 30 : 1 – 5 : 1                       | 10 : 1 – 3 : 1                      | 1:1                                  | 1:1                            |  |

| Resist Compatibility | Excellent               | Excellent                             | Good                                 | Good                                | Poor                                 | Poor                           |  |

| Device Damage        | Little                  | Little                                | Some<br>possible                     | Some possible                       | Very possible                        | Very possible                  |  |

| Etch Rate (um/min)   | 0.1 ~ 0.5               | 0.1 ~ 0.5                             | 0.05 ~ 0.1                           | 0.05 ~ 0.1                          | 0.02 ~ 0.05                          | 0.02 ~ 0.05                    |  |

| Resolution (um/min)  | 3                       | 2                                     | 1 ~ 2                                | 1 ~ 2                               | 0.5 ~ 1                              | 0.5 ~ 1                        |  |

Ref: J. D. Lee, "Silicon Integrated Circuit microfabrication technology," 2nd edition

Nano/Micro Systems & Controls Lab.

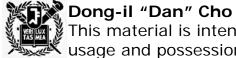

## **Basic Method of RIE (1)**

- Chemical •

- Thermalized neutral radicals chemically combine with substrate material forming volatile products

- Isotropic

- Pure Chemical Reaction

- High Pressure

- Batch Wafer Type

- Less Electrical Damage

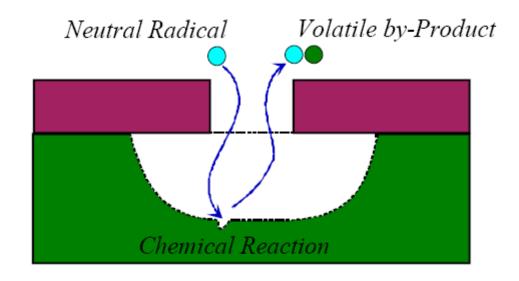

## **Basic Method of RIE (2)**

- Sputtering •

- The ion energy mechanically ejects substrate material —

- Anisotropic

- By Purely Physical Process

- High Directionality

- Low Pressure: long mean free path

- Single Wafer Type

- Low Etch rate

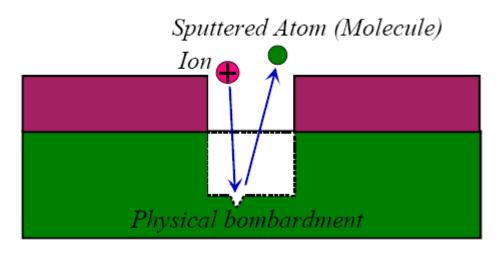

### **Basic Method of RIE (3)**

- Energetic Ion Enhanced

- Ion bombardment enhances or promotes the reaction between an active species and the substrate material

- Damage Enhanced Chemical Reactivity

- Chemical Sputtering

- Chemically Enhanced

- Physical Sputtering

- Ion Reaction

#### **Basic Method of RIE (4)**

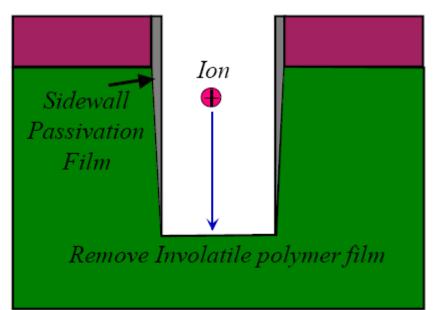

- Protective Ion Enhanced

- An inhibitor film coats the surface forming a protective barrier which excludes the neutral etchant

- Sidewall passivation

- Stopping lateral attack by neutral radical

- Ion directionality

- Involatile polymer film

- Additive film former (N<sub>2</sub>, HBr, BCl<sub>3</sub>, CH<sub>3</sub>F)

#### Summary of RIE Mechanisms and Systems

#### Sidewall-inhibitor deposition

Dong-il "Dan" Cho

- Sources: etch byproducts, mask erosion, inlet gases

- Removed on horizontal surfaces by ion bombardment

- A possible mechanism in ion enhanced etching

#### Nano/Micro Systems & Controls Lab.

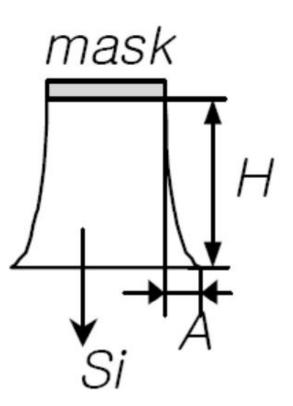

#### **Characterization of RIE Performance**

- Etch performance valuation

- Etch rate

- Anisotropy (define as 1-A/H)

- Selectivity to mask material

- Micro-loading effect (RIE lag)

- Macro-loading effect

(dark field or bright field)

- Etch uniformity

- Surface quality

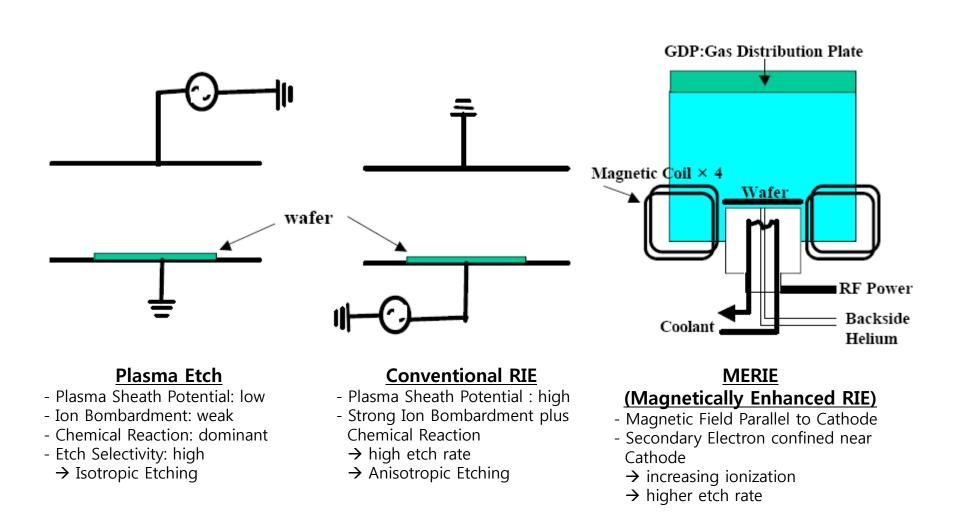

#### Plasma Etch & RIE & MERIE

#### Nano/Micro Systems & Controls Lab.

#### Schematic of ICP(Inductively Coupled Plasma)

- Low pressure(< 5 mTorr) and low temperature(-50°C ~+50°C) etching

- Independent power control and high density plasma (~  $10^{12}$ )

- Improved Plasma Uniformity

Nano/Micro Systems & Controls Lab.

#### Mask Materials for RIE

- Etch mask •

- PR (Photo Resist), Hard mask (SiO<sub>2</sub>, Al) is used

- Selectivity

- = etch rate of etching material / etch rate of mask

- Usually, standard PR (for CMOS) is not adequate for  $O_2$  plasma etch  $\rightarrow$  hard mask required

- Selectivity of silicon:AZ1512

- Cl based etch (physical etch): <2</li>

- F based etch (chemical etch): < 10

(if  $O_2$  gas is inserted the chamber the selectivity would be lower than 10)

Nano/Micro Systems & Controls Lab. This material is intended for students in 4541.844 class in the Spring of 2009. Any other

usage and possession is in violation of copyright laws

#### **Reaction in RIE Process (1)**

- Reactants

- Cl-based ( $Cl_2$ ,  $BCl_3$ )

- Sputtering or ion-enhanced etch mechanism

- High anisotropy

- Low selectivity

- F-based(SF<sub>6</sub>)

- Chemical etch mechanism

- High selectivity

- High etch rate

- Isotropic etching

- Br-based (HBr,  $Br_2$ )

- Good anisotropy

- Sidewall passivation: SiBrx (x<4)

- Good selectivity to oxide

Nano/Micro Systems & Controls Lab.

#### **Reaction in RIE Process (2)**

An example of RIE mechanisms (Cl based)

Ion and electron formation  $e+CI/CI_2 \rightarrow CI^+/CI_2^++2e$

Etchant formation  $e+Cl_2 \rightarrow 2Cl+e$

Adsorption of etchant on the substrate  $CI/CI_2 \rightarrow Si_{surf}-nCI$

Reaction on surface  $Si_{surf}$ -nCl  $\rightarrow$  SiCl<sub>x(ads)</sub>

Product desorption  $SiCl_{x(ads)} \xrightarrow{(ions)} SiCl_{x(gas)}$

#### **Reaction in RIE Process (3)**

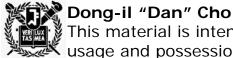

An example of RIE mechanisms (F based Si etch) ٠

#### **Reaction in RIE Process (4)**

An example of RIE mechanisms (Br based Si etch)

## HBr $\rightarrow$ H + Br $Br + Si \rightarrow SiBr_4$

- Small amount  $O_2$  for sidewall passivation

- A little NF<sub>3</sub> for preventing black silicon

- Endpoint by time

## CCP: BCl<sub>3</sub> Recipe and Example (1)

- System: Drytek DRIE-284

- Process parameter

|                 |                  | Step 1      | Step 2   | Step 3   |  |

|-----------------|------------------|-------------|----------|----------|--|

| Power           |                  | 200 W       | 300 W    | 475 W    |  |

| Pressure        |                  | 20 mTorr    | 20 mTorr | 40 mTorr |  |

| Tin             | ne               | 1 min 1 min |          | 10 min   |  |

| Cl <sub>2</sub> |                  | 0 sccm      | 2 sccm   | 50 sccm  |  |

|                 | BCI <sub>3</sub> | 14 sccm     | 14 sccm  | 5 sccm   |  |

|                 | $N_2$            | 7 sccm      | 7 sccm   | 0 sccm   |  |

- Etch rate: 850 nm/min

- Selectivity: 8.5:1 for oxide hard mask ٠

#### **CCP: BCl<sub>3</sub> Recipe and Example (2)**

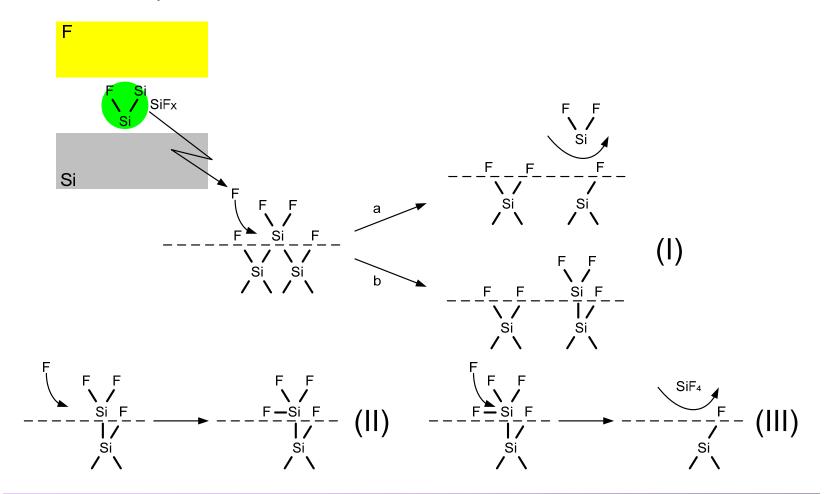

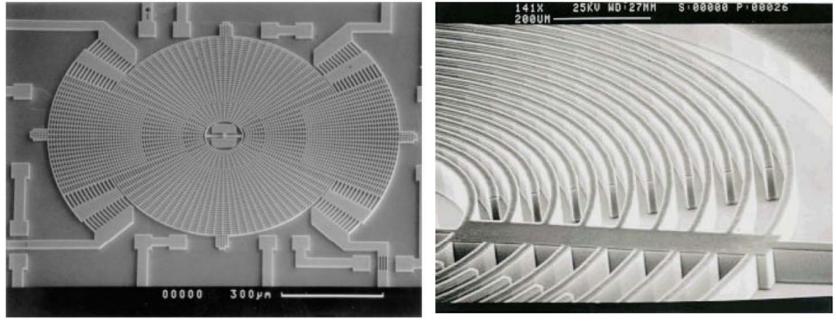

• Fabrication example (proportional amplifier)

#### CCP: SF<sub>6</sub> Recipe and Example (1)

- System: Drytek DRIE-284

- Process parameter

| Power           | 150 W     |  |  |

|-----------------|-----------|--|--|

| Pressure        | 150 mTorr |  |  |

| SF <sub>6</sub> | 30 sccm   |  |  |

| O <sub>2</sub>  | 10 sccm   |  |  |

- Etch rate: 4.2 um/min

- Selectivity: 14.2:1 for oxide hard mask

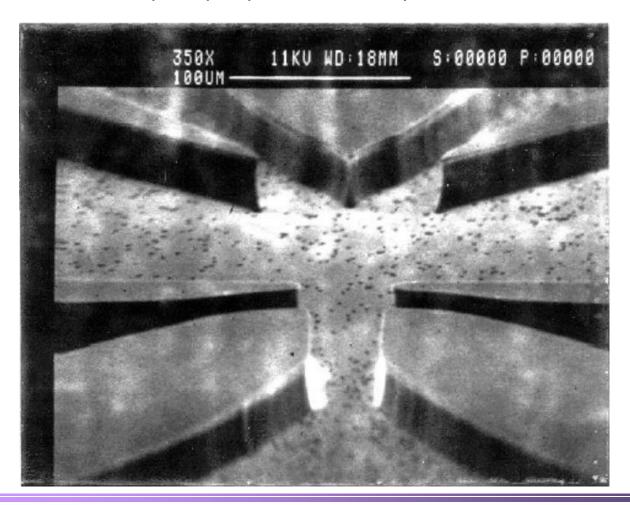

#### CCP: SF<sub>6</sub> Recipe and Example (2)

Fabrication example (vortex amplifier) •

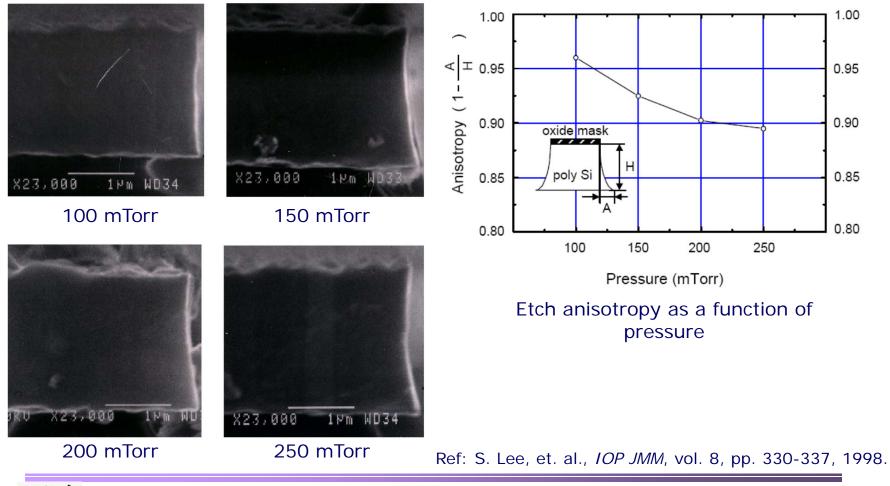

#### CCP: Poly-Si Etch Test (1)

- System: Drytek DRIE-284 •

- Process parameter ۲

| Power           | 300 W        |  |  |

|-----------------|--------------|--|--|

| Pressure        | 75~250 mTorr |  |  |

| Cl <sub>2</sub> | 58 sccm      |  |  |

| He <sub>2</sub> | 100 sccm     |  |  |

#### CCP: Poly-Si Etch Test (2)

Test results •

Dong-il "Dan" Cho

Nano/Micro Systems & Controls Lab.

#### ICP: Poly-Si Etch Recipe of ISRC (1)

- System: STS ICP poly Etcher

- Process parameter (Br based etch) ۲

|             |                 | Step 1<br>(native oxide etch) | Step 2<br>(poly-Si etch) |  |  |

|-------------|-----------------|-------------------------------|--------------------------|--|--|

| Power       | Coil            | 600 W                         | 900 W                    |  |  |

|             | Platen          | 100 W                         | 50 W                     |  |  |

| Pressure    |                 | 2 mTorr                       | 2 mTorr                  |  |  |

| Time        |                 | 15 sec                        | 60 sec                   |  |  |

| Temperature |                 | 20 <sup>o</sup> C             | 20 <sup>o</sup> C        |  |  |

|             | Cl <sub>2</sub> | 20 sccm                       | 0 sccm                   |  |  |

| Gas         | HBr             | 0 sccm                        | 20 sccm                  |  |  |

|             | 0 <sub>2</sub>  | 0 sccm                        | 1 sccm                   |  |  |

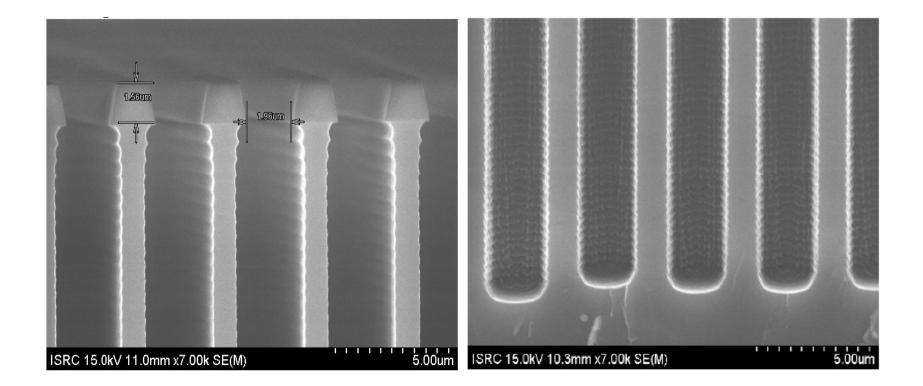

#### ICP: Poly-Si Etch Recipe of ISRC (2)

Line width: 2 um

Line width: 1.5 um

Line width: 0.55 um

- Etch rate of poly-Si: 0.3 um/min ٠

- Selectivity to PR: 3:1 •

- Selectivity to oxide: 100:1 •

- Etch profile: 88  $^{\circ}$  to 90  $^{\circ}$ •

#### **ICP RIE System in ISRC (1)**

- STS ICP poly Etcher (in CMOS area)

- Plasma source type: ICP (inductively coupled plasma)

- Main feed gas :HBr, Cl<sub>2</sub>, Ar, SF<sub>6</sub>, O<sub>2</sub>, He<sub>4</sub>

- Main power: 13.56 MHz 1000 W

- Bias power: 13.56 MHz 30/300 W

#### **ICP RIE System in ISRC (2)**

- STS ICP poly etcher for MEMS

- Plasma source type: ICP (inductively coupled plasma)

- Pump

- Dry pump : Edwards iH80 800 l/m

- Turbo pump Leybold MAG 1500 CT 1000 l/sec

- RF generator

- ENI ACG-10B 1000 W, 13.56 MHz

- ENI ACG-3B 300 W, 13.56 MHz

- Gas

- HBr 50 sccm

- Cl2 20 sccm

- O2 20 sccm

- Ar 50 sccm

#### Various Gas for Poly-Si Etching

| Gas                                     | Reactor            | Pressure | Etch Rate         | Etch Selectivity                                     |                  | Commonte                     |  |

|-----------------------------------------|--------------------|----------|-------------------|------------------------------------------------------|------------------|------------------------------|--|

| Gas                                     | Туре               | (torr)   | (μm/min)          |                                                      | nty              | Comments                     |  |

| CCl <sub>4</sub> /Argon                 | Planar             | .4       | .02(Undoped)      | Poly Si : SiO <sub>2</sub>                           | 15:1             | -                            |  |

| SiF <sub>4</sub> (50%)/                 | Diaman             | 2        | .4(Undoped)       | Poly Si : SiO <sub>2</sub>                           | 25.1             | -                            |  |

| Argon(50%)                              | Planar             | .2       |                   |                                                      | 25:1             |                              |  |

| CF <sub>4</sub> /O <sub>2</sub>         | Barrel             | .2       | .05 ~ .1(Undoped) | Poly Si:Si <sub>3</sub> N <sub>4</sub> :<br>25:2.5:1 | SiO <sub>2</sub> | -                            |  |

| CF <sub>4</sub> /O <sub>2</sub> (4%)    | Planar             | .4       | .057(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 10:1             | -                            |  |

| $C_2 CIF_3$                             | Planar             | .225     | .05(Phos doped)   | Poly Si : SiO <sub>2</sub>                           | 3.5 :1           | -                            |  |

| CF <sub>4</sub> (92%)/O <sub>2</sub> (8 | $F_4(92\%)/O_2(8)$ | 25       | .115(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 10:1             | le e tue u le                |  |

| %)                                      | Planar             | .35      | .105(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 9:1              | Isotropic                    |  |

| C <sub>2</sub> F <sub>4</sub> (50%)/    | Diapar             | Λ        | .159(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 8:1              | lectronic                    |  |

| CF <sub>3</sub> CI(50%)                 | Planar             | .4       | .098(Undoped)     | Poly Si : SiO <sub>2</sub>                           | 5:1              | Isotropic                    |  |

| C <sub>2</sub> F <sub>4</sub> (81%)/    | Planar             | Λ        | .082(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 5:1              |                              |  |

| CF₃CI(19%)                              | Planal             | . 4      | .070(Undoped)     | Poly Si : SiO <sub>2</sub>                           | 4:1              | Anisotropic                  |  |

| C <sub>2</sub> F <sub>4</sub> (92%)/    | Planar             | 25       | .057(Phos doped)  | Poly Si : SiO <sub>2</sub>                           | 6:1              | Anisotropic                  |  |

| Cl <sub>2</sub> (8%)                    | Planal             | .35      | .050(Undoped)     | Poly Si : SiO <sub>2</sub>                           | 5:1              |                              |  |

| CF <sub>3</sub> CI                      | Planar .35         | 35       | .08(Phos doped)   | Poly Si : SiO <sub>2</sub>                           | 13:1             | Intermediate<br>between      |  |

|                                         |                    |          | .03(Undoped)      | Poly Si : SiO <sub>2</sub>                           | 6:1              | Isotropic and<br>Anisotropic |  |

Ref: J. D. Lee, "Silicon Integrated Circuit microfabrication technology," 2nd edition

Nano/Micro Systems & Controls Lab.

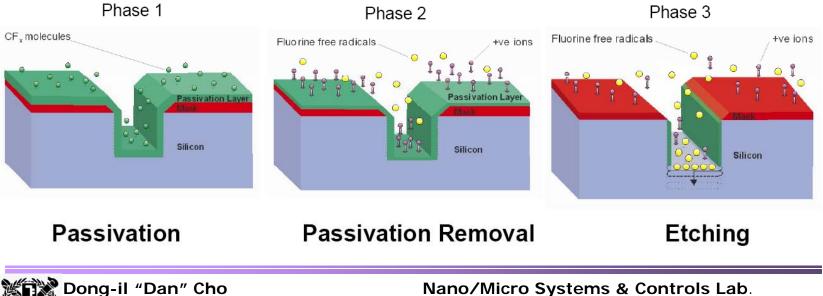

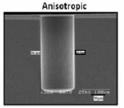

#### **Deep Reactive Ion Etching (1)**

- Uses high density plasma to alternatively etch silicon and deposit etch resistant polymer on sidewall

- Unconstrained geometry 90<sup>o</sup> side walls

- High aspect ratio 1:30

- Easily masked (PR, SiO<sub>2</sub>)

- Bosch process: sidewall passivation  $\rightarrow$  etch  $\rightarrow$  sidewall passivation  $\rightarrow$  etch ...

Nano/Micro Systems & Controls Lab.

#### **Deep Reactive Ion Etching (2)**

- Characteristics of the Deep RIE process •

- SF<sub>6</sub> flow: 30 ~ 150 sccm

- $C_4 F_8$  flow: 20 ~ 100 sccm

- Etch cycle: 5 ~ 15 sec

- Deposition cycle: 5 ~ 12 sec

- Pressure: 0.25 ~ 10 Pa

- Temperature: 20  $\sim$  80 <sup>o</sup>C

- Etch rate: 1.5 ~ 4 um/min

- Selectivity to resist mask: more than 75:1

- Selectivity to oxide mask: more than 150:1

- Sidewall angle:  $90^{\circ} \pm 2$

- Etch depth capability: up to 500 um

Nano/Micro Systems & Controls Lab.

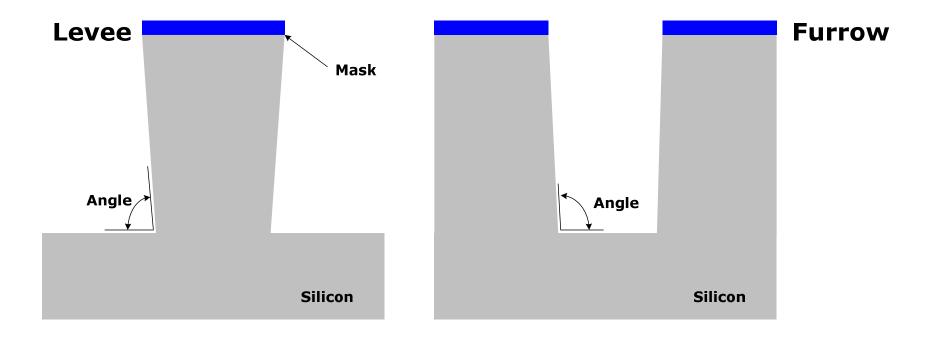

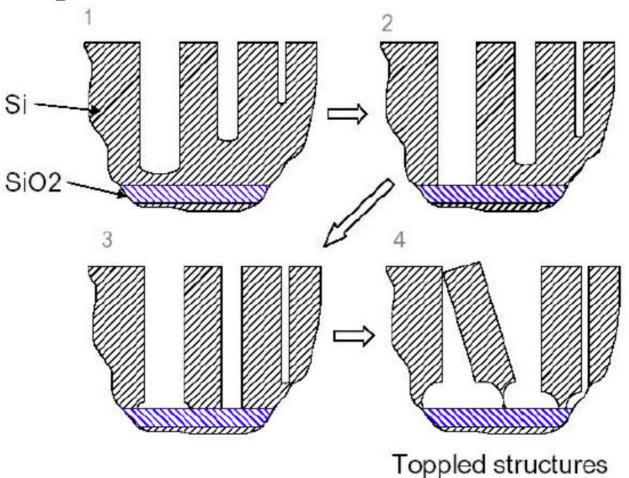

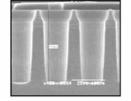

#### **Deep Reactive Ion Etching (3)**

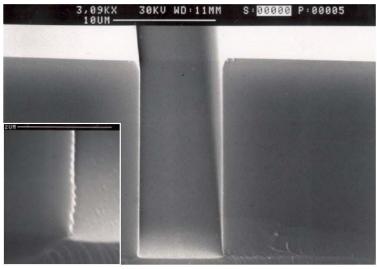

• Fence (levee) structure and trench (furrow) structure have different etch side wall profile

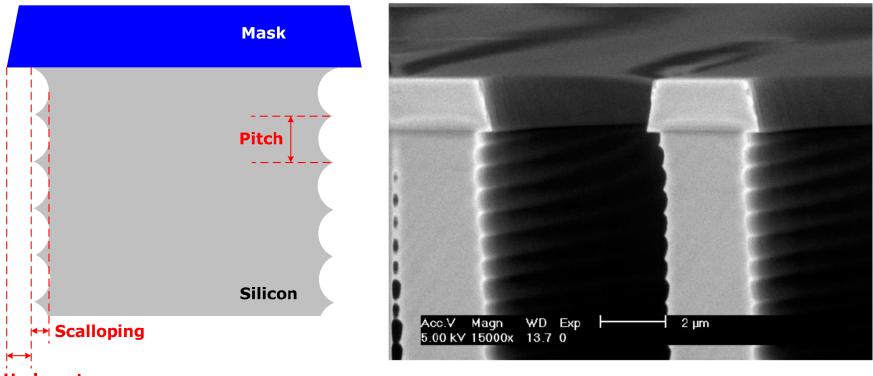

## **Deep Reactive Ion Etching (4)**

- Characteristics of Bosch process •

- Scalloping

- Under cut

#### Undercut

Nano/Micro Systems & Controls Lab.

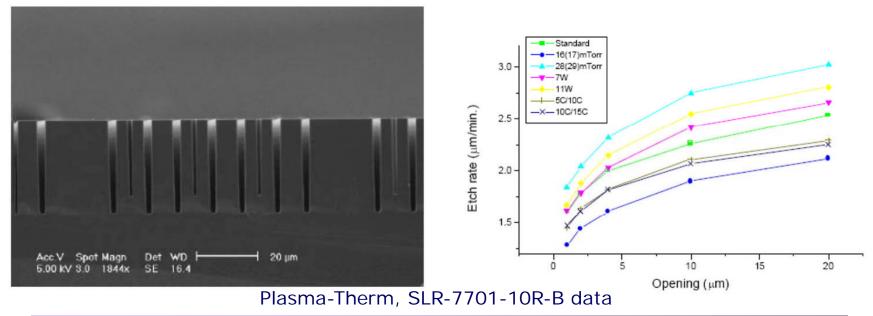

### **Deep RIE Example (1)**

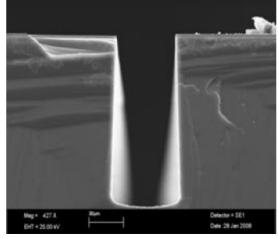

Fabrication example (deep trench) ٠

350µm-depth

100µm-depth

80/m-depth, 4.5 m space width, 2 m line width

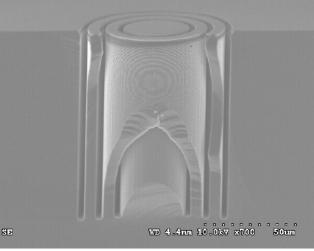

## **Deep RIE Example (2)**

Fabrication example (IMU device) •

Gyroscope

Accelerometer (170<sup>µm</sup>-depth)

## **RIE Lag in Deep RIE Process**

- RIE lag (microloading effect) •

- Etch rate of a wafer with a larger open area is different from the wafer w ith a smaller open area

- Smaller hole has a lower etch rate than the larger holes

- Etchants are more difficult to pass through the smaller hole

- Etch byproducts are harder to diffuse out

- Lower pressure can minimize the effect.

Nano/Micro Systems & Controls Lab.

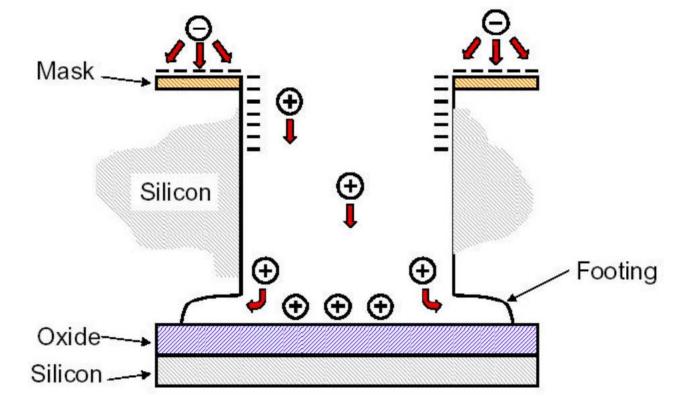

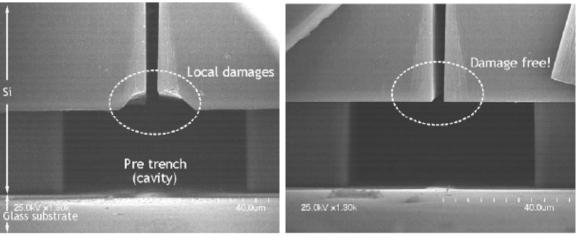

## Footing in Deep RIE Process (1)

Footing •

Nano/Micro Systems & Controls Lab.

## Footing in Deep RIE Process (2)

- Footing formation •

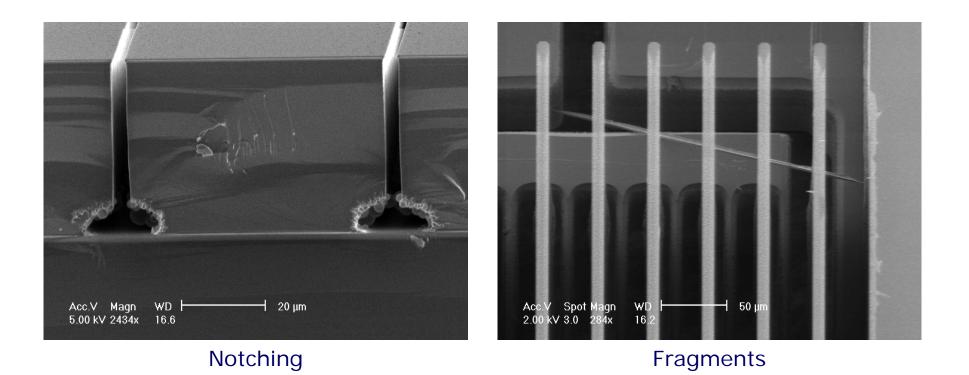

- There is notching at the foot of the silicon trench in a conventional deep RIE of SOI substrate due to charge accumulation at the base of the trench.

Nano/Micro Systems & Controls Lab.

## Footing in Deep RIE Process (3)

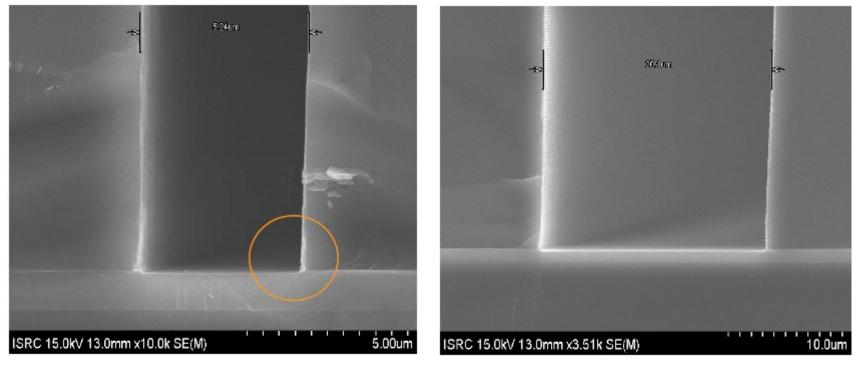

Footing SEM pictures ٠

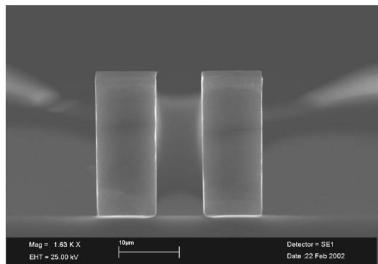

## **Reducing Footing Phenomenon in SOI Process**

- Deep RIE with SOI kit (Surface Technology Systems, STS)

- A conventional approach to reduce footing (notching) is to increase the passivation during the overetch

- This increase process time and is only practical for similare feature sizes with short overetch time

- The SOI kit on the system controls the charging and hence broadens the process window significantly with out increased passivation

Deep etched trench in 20 um SOI layer with good profile and notch control (8 um gap)

Isolated 10 um line features deep etched in a 20 um SOI layer with notch control (8 um gap centre, 500 um gap either side)

Dong-il "Dan" Cho

#### Nano/Micro Systems & Controls Lab.

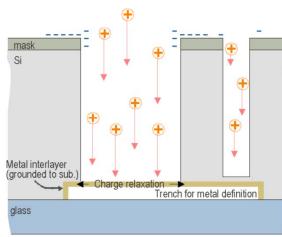

## **Reducing Footing Phenomenon in SOG Process**

- Prevention method of a notching caused by surface charging

- To prevent silicon from a notching in deep RIE process by introducing a self-aligned metal interlayer to a silicon/glass bonded fixture.

- A metal interlayer prevents a charge buildup at the bottom of a silicon trench, therefore silicon structures do not suffer from charge-induced local damage.

An automatically aligned metal interlayer prevents silicon from notching by fast charge relaxation. Test result for a simple trench: a 5 µm width silicon trench processed (Left picture) without a self-aligned metal interlayer (Right picture) with a self-aligned metal interlayer.

Dong-il "Dan" Cho

### Nano/Micro Systems & Controls Lab.

## Latest Deep RIE in ALCATEL

- AMS 4200 for volume production cluster platform

- Each process module is fitted with an Alcatel patented high-density ICP type plasma source.

- The source is fixed on top of a diffusion chamber surrounded by a number of permanent magnets.

- Achievements of the DRIF:

- Profile control

- High mask selectivity: >300:1

- Super High Aspect Ratio: >100:1 Isotropic

+ a range of combinations

A wide variety of basic profiles

I I

Alcatel patented SHARP (Super High Aspect Ratio Process) allows an increase of the aspect ratio up to 110

Nano/Micro Systems & Controls Lab.

This material is intended for students in 4541.844 class in the Spring of 2009. Any other usage and possession is in violation of copyright laws

#### 46

## Latest Deep RIE in STS

- STS' Pegasus Systems

- The Power Handling capability is improved

- Improved Etch Rates

- The plasma generation area is larger

- Improved Etch Rates

- Enhanced Etch Uniformity

- Produces a neutral high radical density in the centre of the wafer and a uniform ion density across the whole wafer surface

- Enhanced Etch Depth Uniformity

- Improved Feature profile control

- The STS Pegasus system offer full compatibility with CMOS fabs and foundries

- No Electrostatic Damage

- Excellent Particle Control

- Low Ionic / Metal Contamination

ER 9.91µm/min Profile 91.65 deg Selectivity:PR 117:1

Nano/Micro Systems & Controls Lab.

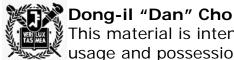

## Deep RIE I in ISRC (1)

- ICP deep silicon RIE (in MEMS area, for 4 inch wafer)

- Plasma-Therm, SLR-7701-10R-B

- Plasma source type: ICP (inductively coupled plasma)

- High aspect ratio up to 20~30

- Feature

- 2 kW, ICP source and 500W bias power

- gas line:  $C_4F_{8'}$  SF<sub>6'</sub> Ar, O<sub>2</sub>, NF<sub>3'</sub> C<sub>2</sub>F<sub>6</sub>)

|                  |                               | Deposition | Etch A | Etch B |

|------------------|-------------------------------|------------|--------|--------|

| Time (sec)       |                               | 5          | 3      | 5      |

| Gas (sccm)       | C <sub>4</sub> F <sub>8</sub> | 100        | 0.5    | 0.5    |

|                  | SF <sub>6</sub>               | 0.5        | 50     | 100    |

|                  | Ar                            | 30         | 30     | 30     |

| Power (W)        | RF1 (bias)                    | 1          | 13     | 13     |

|                  | RF2 (source)                  | 825        | 825    | 825    |

| Pressure (mTorr) |                               | 22         | 23     | 23     |

# Deep RIE I in ISRC (2)

- Etch rate: 2.35 um/min (at 500 um opening)

- Under cut at the top of 4 um line & space: 0.4 um

- RIE lag (2 um/4 um): 24 % etch rate difference ٠

- Selectivity to resist mask: 75:1

- Selectivity to oxide mask: 199:1

- Sidewall profile (levee): 88.5 °

- Sidewall profile (furrow): 90 °

- Etch depth capability: up to 500 um

## Deep RIE I in ISRC (3)

Nano/Micro Systems & Controls Lab.

## Deep RIE II in ISRC (1)

- ICP deep silicon RIE II (in MEMS area, for 6 inch wafer)

- OERLIKON, Versaline

- Plasma source type: ICP (inductively coupled plasma)

- High aspect ratio up to 20~30

- Pump

- Dry pump : Alcatel ADP122P 1,500ℓ/min

- Turbo pump : Edwards STP-A1303CV 900l/sec

- RF generator

- PM, Coil : 2500W 2MHz)

- Electrode : 600W, 13.56MHZ

|                  |                               | Deposition | Etch A | Etch B |

|------------------|-------------------------------|------------|--------|--------|

| Time (sec)       |                               | 2          | 1.5    | 1      |

| Gas (sccm)       | C <sub>4</sub> F <sub>8</sub> | 150        | 0      | 0      |

|                  | SF <sub>6</sub>               | 0          | 250    | 250    |

|                  | Ar                            | 30         | 30     | 30     |

| Power (W)        | RF1 (ICP)                     | 2000       | 2000   | 2500   |

|                  | RF2 (source)                  | 10         | 150    | 10     |

| Pressure (mTorr) |                               | 25         | 40     | 70     |

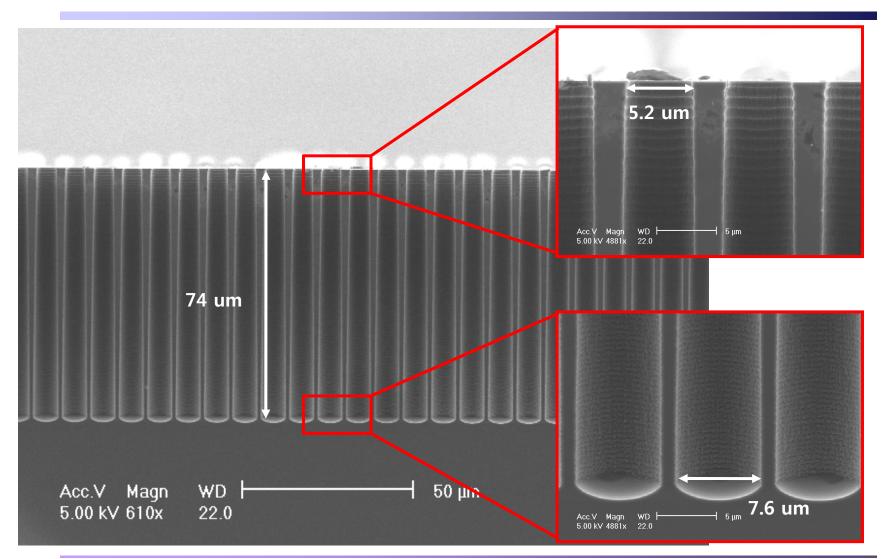

## Deep RIE II in ISRC (2)

- Process parameter of High Rate 2 um recipe •

- Etch rate: 4 um/min

- Aspect ratio: 25

- Selectivity to resist mask: > 100:1

- Selectivity to oxide mask: > 200:1

- Uniformity: 1.2%

- Verticality: 90°±1

- Undercut: 150 nm

- Scallop pitch: 160 nm

- Scallop depth: 50 nm

### Deep RIE II in ISRC (3)

Process results using 'SNU High Etch Rate 2 um' recipe ٠

## Deep RIE II in ISRC (4)

- Process results using 'SNU SOI' recipe •

- Anti-footing recipe for SOI process

5 um line width

20 um line width

### Reference

- 1. K.A. Shaw, Z.L. Zhang, and N.C. MacDonald, "SCREAM I: a single mask, single-crystal silicon, reactive ion etching process for microelectromechanical systems," Sensors and Actuators A, vol. 40, pp. 63-70, 1994

- 2. T. Kim, C. Cho, and D. Cho, "A Three-dimensionally siliconmicromachined fluidic device," IOP J. of Micromechanics and Microengineering, vol. 8, no. 1, pp. 7-16, March 1998.

- 3. C. Cho, J. Kim, and D. Cho, "A Large-force fluidic device micromachined in silicon," IOP J. of Micromechanics and Microengineering, vol. 8, no. 3, pp.195-199, Sept. 1998.

- 4. J.K. Bhadwaj and H. Ashraf, "Advanced silicon etching using high density plasmas," Proc. SPIE Micromachining and Microfabrication Process' Technology, Oct. 1995, Austin, Texas, vol. 2639, pp. 224-229.

- 5. Matt Wasilik, "Low Frequency Deep Reactive Ion Etching For SOI Processing," Berkeley Sensor & Acutator Center

- 6. Lee, S., Cho, C., Kim, J., Park, S., Yi, S., Kim, J., and Cho, D., "The Effects of Post-deposition Processes on Polysilicon Young's Modulus", IOP Journal of Micromechanics and Microengineering, vol. 8, no. 4, pp. 330-337, Dec. 1998

## Reference

- 7. S. Park, "Plasma-Therm Deep Silicon Etcher 공정개발 결과," Nov. 1999

- 8. Marc J. Madou, "Fundamentals of MICROFABICATION," 2nd edition

- 9. J. D. Lee, "Silicon Integrated Circuit microfabrication technology," 2nd edition

## **RIE Principles (2)**