# Embedded System Application 4190.303C 2010 Spring Semester

#### History of Microprocessors for Embedded Systems

Naehyuck Chang Dept. of EECS/CSE Seoul National University naehyuck@snu.ac.kr

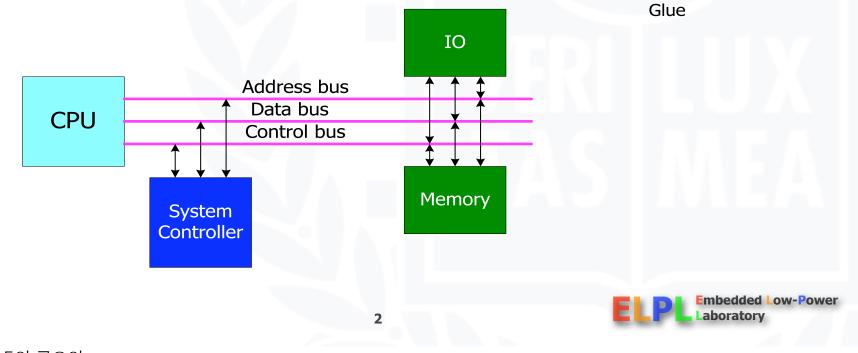

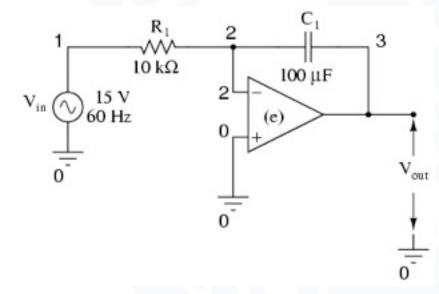

## **Computer System Architecture**

- Conceptual configuration

- Central processing unit

- Memory

- Inputs and outputs

- System controller

- Wrapper or glue

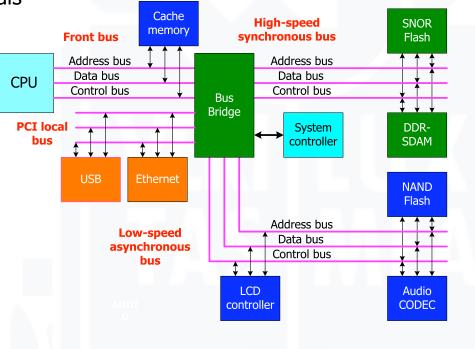

# **Computer Architecture**

- Practical configuration

- Multiprocessors or coprocessors

- Memory hierarchy

- Bus hierarchy

- Types of memory devices: RAM, ROM, etc.

- High-speed and low-speed peripherals

Embedded Low-Power

## **Embedded System Architecture**

- Embedded (computer) systems are computers

- Have all the necessary components

- ♀ CPU, memory, IO, etc.

- Embedded systems have specific dedicated applications

- May have imbalanced architecture

- Small RAM and big ROM

- Slow CPU but fast memory

- 8 bit CPU but with a 32 bit graphics accelerator

- May have special peripherals

- A/D converters

- Special sensors

- Special communication adapters

- Special hardware support

- Embedded systems are optimized

- May not have peripherals for development

- ♀ No keyboard, no mouse, no display, etc.

- ♀ Not enough memory for compliers, etc.

mbedded Low-Power

# **Rule of Thumb**

- Better embedded system architecture design

- Need to understand computer system architecture

- Need to understand system software

- Need to understand application

- Domain knowledge

- Need to understand hardware to application

- Vertical optimization

- Need to understand technology

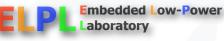

# **Analog Computers**

☑ Integration

$$V_{out} = \int_0^t 15\sin(2\pi \times 60t)dt$$

2010년 3월 5일 금요일

Embedded Low-Power

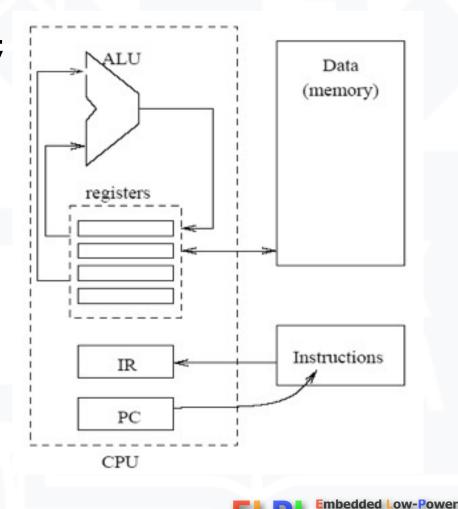

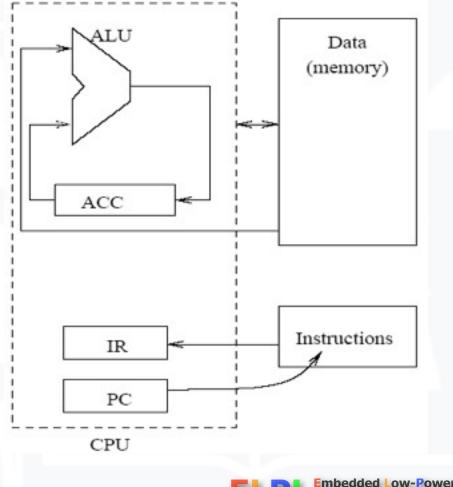

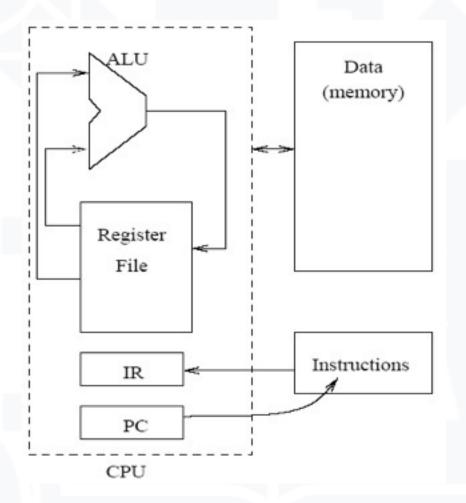

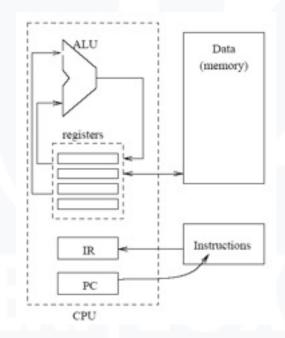

## **Stored Program Control by Von Neumann**

- Register

- A memory location in the CPU

- PC

- Program counter that holds the memory address of the next instruction

- ♀ IR

- Instruction register that holds the current instruction

- Acc

- Accumulator that holds the result of an operation performed by the ALU

- Register File

- A collection of several registers

#### **Hardwired Logic versus Microprocessor**

- Hardwired logic

- Parallel architecture for the next state forming and the output forming logic

- Fast but complicated

- Not good scalability

- Microprocessor

- Sequential execution for the next state forming and the output forming logic

- Slow but simple structure

- Good scalability with an expense of speed

mbedded Low-Power

#### **Stored Program Control by Von Neumann**

pc= 0;

#### do {

instruction = memory[pc++]; decode( instruction ); fetch( operands ); execute; store( results ); } while( instruction != halt );

## **Accumulator Architecture**

- Has a special register, called an accumulator

- Combined with another operand as input to the ALU, with the result of the operation replacing the contents of the accumulator

- Operation

- Place one of the numbers into the accumulator (load operand)

- Execute the add instruction

- Store the contents of the accumulator back into memory (store operand)

# Load/store (Register) Architecture

- Registers

- Faster access but are expensive

- For frequently accessed data

- Memory

- Slower but less expensive

- Principle of "locality"

- At a given time, a program typically accesses a small number of variables much more frequently than others

- Loads and stores the registers from memory

- Arithmetic and logic instructions operate with registers, not main memory, for the location of operands

Embedded Low-Power

# **Before Microprocessors (Prehistory)**

- Central processing unit is composed of discrete components

- Vacuum tubes

- Transistors

- General Systems are too expensive to be embedded in a system

- Central processing unit is composed of MSI (medium scale integrated circuits)

- Westinghouse 2500 computer

- One to four 19" lacks compose of a CPU

- Magnetic core main memory

- Power plant control

- Equipped with most user interface components

- Imbalanced architecture

- - Thousands of sensors and actuators

- Many monitors

- Special hardware support for SOE (sequence of event)

- Special software feature

- Real-time operating system

mbedded Low-Power

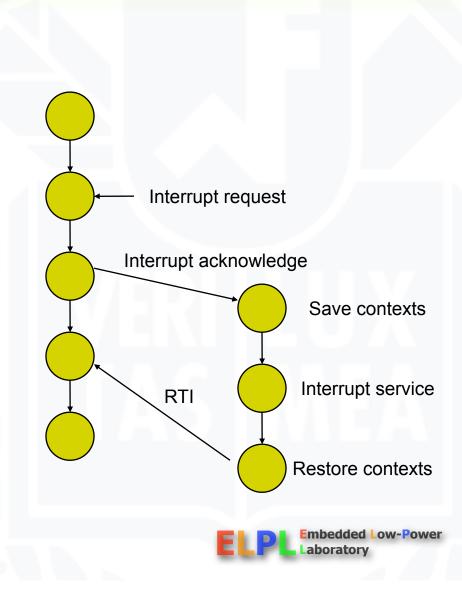

#### **Exception and Interrupt Processing**

13

- Program is for sequential execution

- Types of exception and interrupts

- Reset

- Hardware interrupt

- Software interrupt

- Exception

- Overflow

- Divide by zero

#### **Exception and Interrupt Processing**

- Sessential for handling of errors and asynchronous events

- Polling and interrupt

- Context

- Microprocessor has long-term memory problem

- Problematic long-term memory: relies on external storage

- Remember only short-term memory contents

- Precision interrupt for embedded systems

- ☑ All the microprocessors are for embedded systems

- No peripherals, no memory

- Intel 4004 was a 4-bit CPU designed for usage in calculators

- Clocked at 740 KHz

- Perfect fit for calculators but not very suitable for microcomputer use due to limited architecture

- No interrupt support

- 3-level deep stack

- Complicated method of accessing the RAM

2010년 3월 5일 금요일

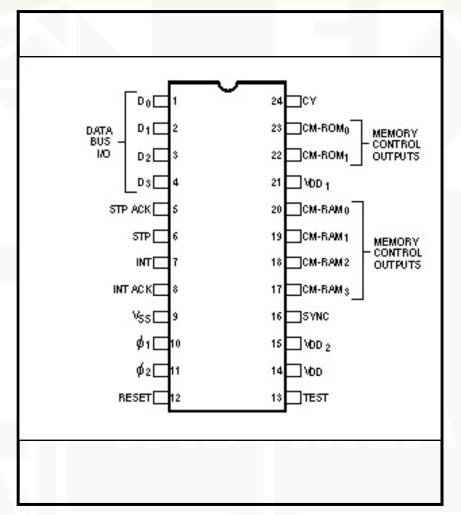

Intel D4040: a practical successor of i4004

| Features       | 4004               | 4040                                                |  |  |

|----------------|--------------------|-----------------------------------------------------|--|--|

| Program memory | 4 KB               | 8 KB (two 4 KB banks)                               |  |  |

| Stack memory   | 3 levels           | 7 levels                                            |  |  |

| Registers      | 16 index registers | 24 index registers (two banks - 16 and 8 registers) |  |  |

|                |                    | 16 additional instructions (see below)              |  |  |

|                |                    | AND and OR logical instructions                     |  |  |

| Instructions   |                    | Interrupt-related instructions                      |  |  |

|                |                    | ROM and index bank selection instructions           |  |  |

|                |                    | Two new load accumulator instructions               |  |  |

| Interrupts     | None               | Program can be interrupted by external signal       |  |  |

|                |                    | STP - switch processor to STOP mode                 |  |  |

|                |                    | STP ACK - processor is in STOP mode                 |  |  |

| Pins/signals   |                    | INT - interrupt input                               |  |  |

|                |                    | INT ACK - interrupt acknowledge                     |  |  |

|                |                    | CM-ROM <sub>1</sub> - ROM bank selection output     |  |  |

| Other features |                    | Single step operation                               |  |  |

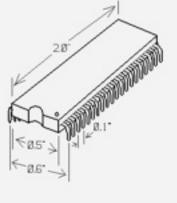

| Package        | 16-pin DIP         | 24-pin DIP                                          |  |  |

2010년 3월 5일 금요일

Embedded Low-Power

| 4008/4009 | standard memory and I/O interface set                                 |  |  |  |

|-----------|-----------------------------------------------------------------------|--|--|--|

| 4040      | 4-bit Central Processor Unit with 60 instructions                     |  |  |  |

| 4101      | 256 x 4 RAM                                                           |  |  |  |

| 4201      | clock generator                                                       |  |  |  |

| 4265      | programmable general purpose I/O device                               |  |  |  |

| 4269      | programmable keyboard display device                                  |  |  |  |

| 4289      | standard memory interface                                             |  |  |  |

| 4308      | 1024-bit mask programmable ROM and four 4-bit I/O Ports               |  |  |  |

| 4316/2316 | 2048-bit ROM                                                          |  |  |  |

| 4702/1702 | 2048-bit Erasable and Electrically Reprogrammable MOS ROM<br>(Static) |  |  |  |

- Intel 4040 microarchitecture

- 8 KB program memory

- Two 4 KB banks

- Jump to any address within currently selected bank

- 640 B data memory

- A SRC instruction specify address

- WRM or RDM writes or reads accumulator data to memory

- Data memory is separate from program memory

- Stack is 7-level deep 0

- Separate from program memory and data memory 9

- Interrupts

- One maskable interrupt can be enabled or disabled by DIN and EIN instructions 9

| 3 0          | 3 0 3                 | 0                            | 3 0                   | 3 0              |

|--------------|-----------------------|------------------------------|-----------------------|------------------|

| Acc.         |                       | 181                          | IRO                   | IR1              |

| Accumulator  | IR2                   | IR3                          | IR2                   | IR3              |

|              | IR4                   | IR5                          | IR4                   | IR5              |

| C Carry flag | IR6                   | IR7                          | IR6                   | IR7              |

|              | Index Register Bank 1 |                              | Index Register Bank 0 |                  |

| 11           | PC                    | <u> </u>                     | IR8                   | IR9              |

|              | _                     | IR10                         | IR11                  |                  |

| Stac         | _                     | IR12                         | IR13                  |                  |

| Stac         | _                     | IR14                         | IR15                  |                  |

| Stac         | Toda                  | Index and Scratch pad Regist |                       |                  |

| Stac         | k Level 4             | mule                         | 7                     | pau Registers    |

| Stac         |                       | SRC register                 |                       |                  |

| Stat         |                       |                              |                       |                  |

| Stap         | k Level 7             |                              | CL                    | CM-ROM<br>CM-RAM |

| Program co   | C                     | Command Line Reg.            |                       |                  |

- Intel 4040 microarchitecture

- 4-bit accumulator

- Arithmetic and logic operations, reading and writing data from/to RAM and I/O ports

- 24 4-bit Index registers

- Lower 8 registers can be selected from bank 0 or 1 using SB0 and SB1 instructions

- Memory access is not convenient due to short bit width

- - Data moving instructions

- Arithmetic add, subtract, increment and decrement

- Logic rotate, AND and OR

- Control transfer conditional (limited to current ROM), unconditional, call subroutine and return from subroutine

- Input/Output instructions

- Interrupt-related instructions halt, enable, disable, and return from subroutine

- Instruction length can be one or two bytes

#### 8 bit microprocessors

- Beginning of microprocessor-based system era

- CPU core only and dedicated peripherals

- ♀ Serial communication ports, parallel IO ports, timers and interrupts controllers

- Assembly programming and later C programming

- No memory and bus hierarchies

- Representative processors

- Motorola 6800 series

- MOS Technology 6502

#### Architecture

- Accumulator, Register and memory

- Arithmetic and logical operation

- ADD (\$1000), (\$1001)

- Addressing mode

- CPU was not faster than memory

- Both accumulator and register architectures were feasible

- LD D0, (\$1000

ADD D1, D0

Embedded Low-Power

- CISC type

- Complex instructions are added

- Non-pipelined

- Block transfer, etc.

- 1 to 8MHz operation

- Usually SRAM is used for embedded applications

- CPU is capable of 64KB addressing

- ♀ Commonly 1 to 16KB memory

Embedded Low-Power

#### Motorola 6800 series

- Accumulator architecture

- Accumulator A (ACCA) and Accumulator B (ACCB)

- 8-bit register used for arithmetic and logic operations

- Memory devices are faster than CPUs

- Index (IX) register

- 6-bit register for temporary storage or as an index when indexed addressing is used

ss

- 16-bit Stack pointer (SP)

- Condition code register

- Half carry (H) set if there was a carry from bit 3 to bit 4 of the result when the result was calculated

- Interrupt mask (I) set if the IRQ interrupt is disabled

- Negative (N) set if the most significant bit of the result is set

- Zero (Z) set if the result is zero

- ♀ Overflow (V) set if there was an overflow during last result calculation

- Garry (C) set if there was a carry from the bit 7 during last result calculation

mbedded Low-Powe

#### Addressing mode

- Implied

- Data value/data address is implicitly associated with the instruction

- Accumulator the instruction implies that the data is one of the accumulator registers

- Immediate

- 8-bit or 16-bit data is provided in the instruction

- Direct

- One-byte operand provided in the instruction specifies the memory address in page zero (0000h 00FFh) where data is located

- Extended

- Two-byte operand provided in the instruction specifies the memory address where data is located

- Relative

- One byte offset is added to the address of the next instruction (the contents of the program counter register + 2)

- General Section Se

- Indexed

- One byte operand is added to the contents of the IX register

- The resulting 16-bit value is a pointer to memory where data is located

#### Exception processing

- ☑ IRQ

- Maskable interrupt

- Program counter, index register, accumulators and condition code registers are stored in the stack

- Further interrupts are disabled

- Processor jumps to memory location address of which is stored in memory FFF8h FFF9h

- Return from the interrupt the processing routine with RTI instruction

#### MMI

- Non-maskable interrupt that cannot be disabled

- Program counter, index register, accumulators and condition code registers are stored in the stack

- Further interrupts are disabled

- Processor jumps to memory location address of which is stored in memory FFFCh FFFDh

- Return from the interrupt the processing routine with RTI instruction

- ♀ SWI

- Software interrupt

- Invoked from the program

- Program counter, index register, accumulators and condition code registers are stored in the stack

- Disables the further interrupts

- Jumps to memory location address of which is stored in memory FFFAh FFFBh

- Return from the interrupt the processing routine should use RTI instruction

- This interrupt can not be disabled.

Embedded Low-Power

- MOS Technology 6502

- Apple Computer

- ♀ Competitor MOS Technology cloned and upgraded the 6800 with its 6502

- 8-bit accumulator register (A)

- 8-bit status register (SR)

- 8-bit stack pointer (SP)

- 16-bit program counter (PC)

- Zero page

- Subroutine call/scratchpad stack's address space is hardwired to memory page \$01 (\$0100-\$01FF)

- Scratchpad memory

- LDA \$00 ; zero page

LDA \$0000 ; non-zero page

#### Intel 8080

- Combination of accumulator and register architecture

- Accumulator and six 8 bit registers

- Pairs BC, DE and HL could be combined as 16 bit registers

- Data moving instructions

- 16 bit stack pointer

- ♀ 8 level internal stack of the 8008

- 6 bit program counter

- Register addressing

- Register references the data in a register or in a register pair

- Register indirect instruction specifies register pair containing address, where the data is located

- ☑ I/O mapped I/O

- No zero page

- processor always uses 16-bit addresses for data access

- Zero page is reserved for vectors and RST instructions

mbedded Low-Powe

- ☑ Zilog Z80

- Eight real improvements over the 8080:

- An enhanced instruction set including new IX and IY index registers and instructions for them

- Two separate register files, which could be quickly switched, to speed up response to interrupts

- Block move, block I/O, and byte search instructions

- Bit manipulation instructions

- A built-in DRAM refresh address counter that would otherwise have to be provided by external circuitry

- Single 5 Volt power supply

- Fewer outboard support chips required for clock generation and interface to memory and I/O

- A much lower price

| -        |                           |                 | 1.0.0         |  |

|----------|---------------------------|-----------------|---------------|--|

| 27       | H1                        | - AØ            | 31            |  |

| 19 22 21 | MREO<br>I ORO<br>MR<br>RD | A A A A         | 8488 8488     |  |

| 28,      | REFSH                     | A6<br>A7        | 畜             |  |

|          | HALT                      | A8<br>A9<br>A18 | 39<br>48      |  |

|          | MAIT                      | A11<br>A12      | 1             |  |

| 16       | INT<br>NMI                | A13<br>A14      | 3 4 5         |  |

| 26       | RESET                     | A15             | 14            |  |

| 25       | BUSRO<br>BUSAK            | DE 12/2         | 15<br>12<br>8 |  |

| 6        | ark                       | D4              | 7             |  |

|          | Z8Ø                       | D5<br>D6<br>D7  | 18            |  |

Embedded Low-Power

aboratory

2010년 3월 5일 금요일

- Higher integration thanks to CMOS

- Embedded controllers

- Peripherals are embedded

- Dedicated peripherals disappeared

- Bus hierarchy

- ESA bus

- S-bus

- C programming

- Protection

- User mode and supervisory mode

- 24MB addressing

- Dynamic memory is used

2010년 3월 5일 금요일

#### Motorola 68000 (68K)

- Complete register architecture CISC

- 8 general-purpose data registers (D0-D7)

- 8 address registers (A0-A7)

- A7 is the stack pointer

- Arithmetic and logical operations are done by registers

- Memory accesses are done by data move instructions between registers and memory

- 16 bit data and 32 bit addressing

- No page or segment registers

- Orthogonal instruction set architecture

- Almost all address modes are available for almost all instructions

- Motorola 68000 (68K)

- Privilege levels

- Two levels of privilege: user and supervisor modes

- - 8 levels, strictly prioritized

- Fully programmable exception table at fixed location permitting 256 vectors

- ♀ CPU is getting faster than memory

- No more accumulator architecture and zero page

- Big-endian processor

- Higher order bytes first

- No backward compatibility with 8 bit 6800 series

- ♀ Continue to 68020, 68030 and 68040 before PowerPC

#### Intel 8086

- Source code compatible with i8080

- Segment register for 24 bit addressing

- 16 bit general purpose registers

- General of the second stress of the s

- Poor hardware architecture but better chance for software

- Mathematical floating point coprocessor: i8087

- Major change occurred in i80286

- Continue to 80386, 80486 and Pentium

## 32 bit and 64 bit Microprocessors

- Distinct different between general purpose microprocessor and embedded processor

- Operation speed

- Memory hierarchy

- Embedded peripherals

- Bus hierarchy

- Operating systems

- Networking

- Development environment

#### 32 bit and 64 bit Microprocessors

- Many powerful processors

- ☑ Intel 80386 and 80486

- Motorola PowerPC

- Intel XScale

- MIPS RISC series

- This course covers ARM9 architecture with Motorola Dragonball

#### **Current Embedded Processors**

- Embedded processors rather than embedded controllers

- Containing more general purpose peripherals

- Market division

- Powerful 32 bit RISC cores

- Low-cost small size RISC/CISC cores

- Reconfigurable CPU cores

- Soft-microprocessors

- Cache and high-speed main memory (266 DDR SDRAM)

- PCI or equivalent local bus expansion

#### Homework (due: One week later)

- Survey and summarize the following terms:

- Accumulator architecture

- Register architecture

- Zero page

- Addressing modes

- Software interrupt

- ☑ I/O mapped I/O vs. memory mapped I/O

- Little and Big endians

- Segment registers

- Orthogonal instructions vs. implicit addressing

- Register allocation