# **MODERN FET STRUCTURES**

Sung June Kim <u>kimsj@snu.ac.kr</u> http://helios.snu.ac.kr

# CONTENTS

- Small-Dimension Effects

- Select Structure Survey

## Small-Dimension Effects

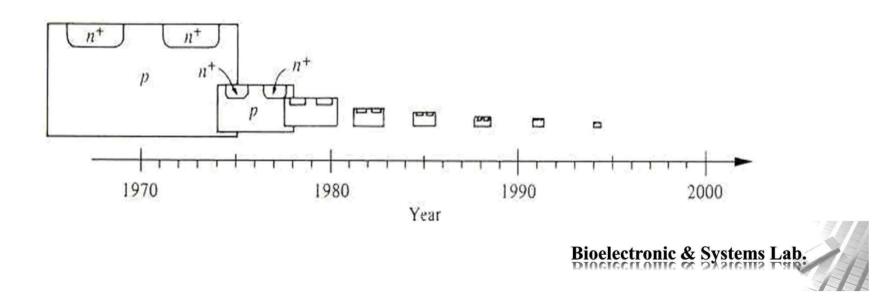

• To achieve higher speeds and increased packing densities, FET device structures have become smaller and smaller.

- Departure from long-channel behavior

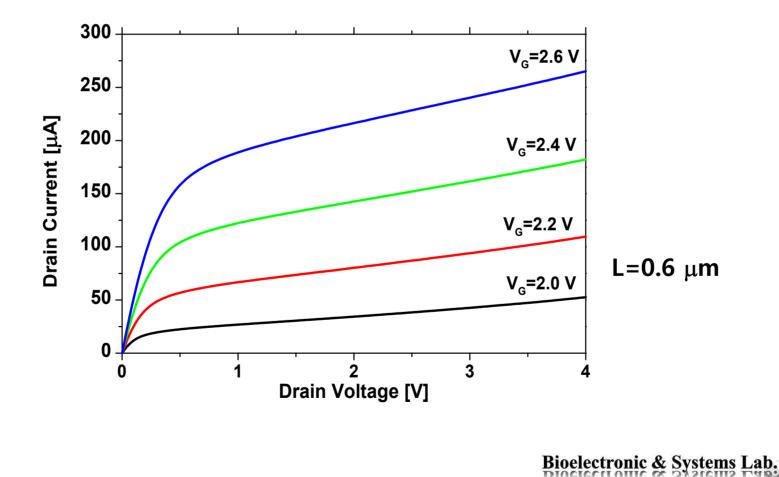

- Significant upward slant in the post pinch-off portions of the  $I_D V_D$

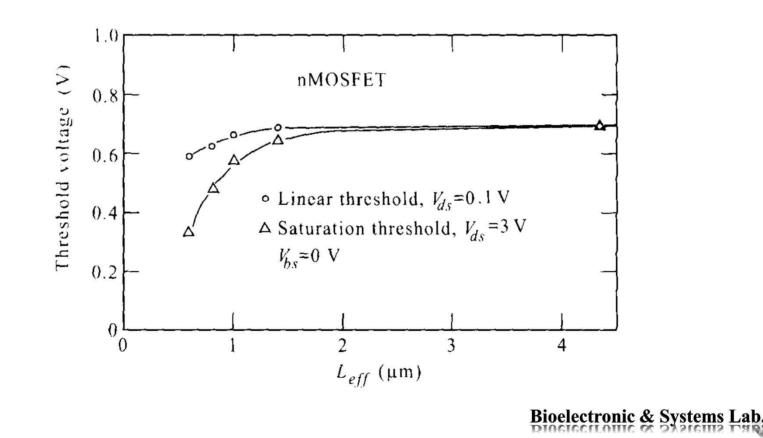

• In short-channel devices,  $V_T$  becomes a function of the gate dimension and the applied biases.

#### Threshold Voltage Modification

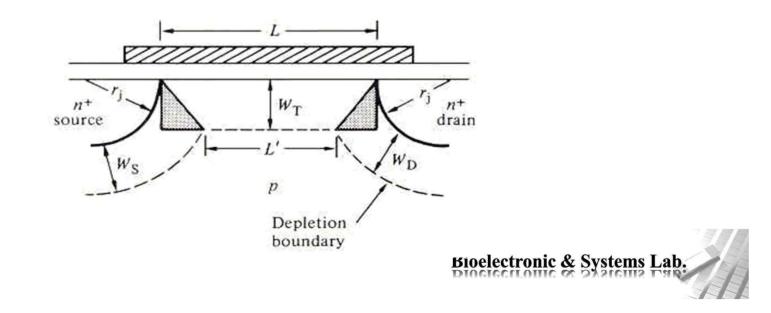

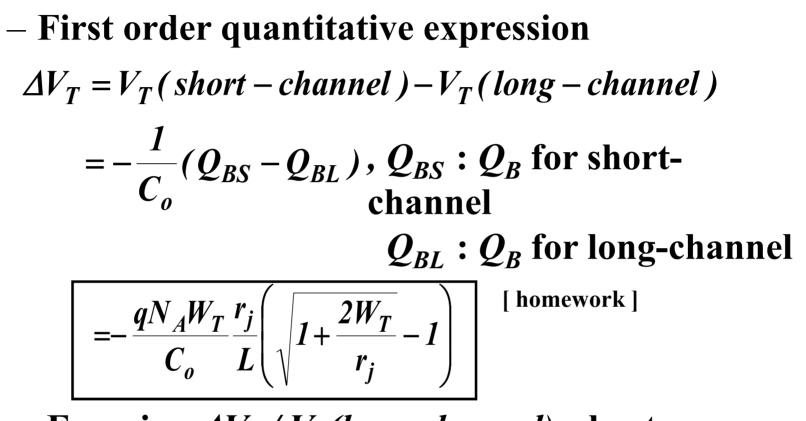

## • Short-channel

- $|V_T|$  monotonically decreases with decreasing L.

- The source and drain assist in depleting the region under the gate.  $\bigotimes$  less gate charge for inversion  $\bigotimes V_T \downarrow$

- Examing  $\Delta V_T / V_T$  (long channel), shortchannel effects are decreased by reducing  $x_{o,}$ reducing  $r_{j,}$  and increasing  $N_A$ .

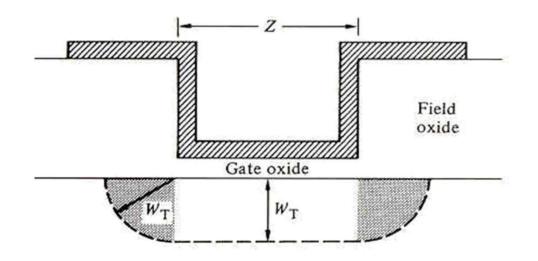

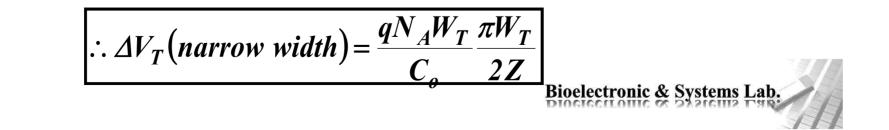

# • Narrow channel (skip)

- $|V_T|$  monotonically increases with decreasing Z. (Opposite to the L-dependence)

- The gate-controlled depletion region extends to the side, lying in part outside the Z-width of the gate; that is, the effective charge  $/\text{cm}^2$  being balanced by the gate charge  $\uparrow \bigotimes V_T \downarrow$

• If the lateral regions are assumed to be quartercylinders of radius  $W_T = qN_A \left( ZLW_T + \frac{\pi}{2} W_T^2 L \right)$  $Q_R(narrow width) = -$

$$W what n = -\frac{ZL}{ZL}$$

$$= -q N_A W_T \left( 1 + \frac{\pi}{2} \frac{W_T}{Z} \right)$$

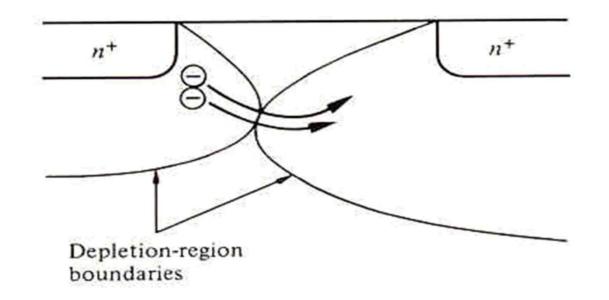

#### Parasitic BJT Action

- MOSFET bears a physical resemblance to a lateral BJT

- Punch-through

- The depletion regions around the source and drain to touch.

- The gate loses control of the subgate region and the  $I_D$  flows beneath the surface through the touching depletion regions.

- Punch-through can be suppressed by increasing N<sub>A</sub> and decreasing the depletion widths.

- ষ্ট্র increasing parasitic capacitances.

- **A** perform a deep-ion implantation to selectively

increase the doping of the subgate region.

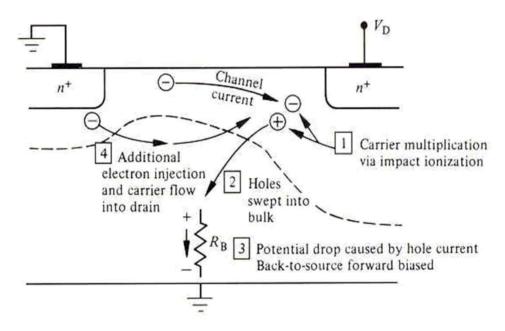

- Carrier multiplication and regenerative feedback

- In short-channel devices, the carrier multiplication coupled with regenerative feedback can dramatically increase  $I_D$ and places a reduced limit on the maximum  $V_D$ .

The added electrons drift into the drain. The source PN junction is forward biased.

#### Hot-Carrier Effects

- Oxide charging ( charge injection and trapping in the oxide )

- In the vicinity of the drain, some of carriers gain a sufficient amount of energy to surmount the Si-SiO<sub>2</sub> barrier.→ A charge build-up within the oxide

- A larger percentage of the gated region is affected in the smaller devices.

- Significant changes in  $V_T$  and  $g_m$ .

- Oxide charging limits the useful "life" of a device.

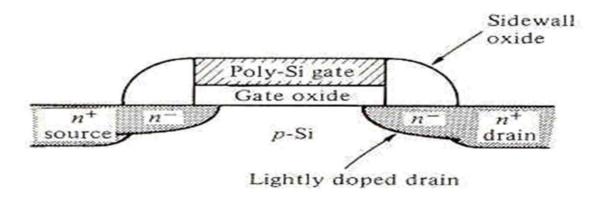

- To minimize hot-carrier effects, the LDD ( Lightly Doped Drain ) structure is used.

- Velocity saturation

- The carrier drift velocities inside Si at T=300K approach a maximum value of  $v_{dsat} \cong 10^7 \text{ cm} / \text{sec}$  when the electric fields are large.

- $-I_{Dsat}$  is significantly reduced. Approximately,

$$I_{Dsat} \cong ZC_o(V_G - V_T)v_{dsat}$$

$$I_{Dsat} \propto (V_G - V_T); \text{ short - channel}$$

$$I_{Dsat} \propto (V_G - V_T)^2; \text{ long - channel}$$

#### Ballistic Transport

- If very small dimension structures have L<l (the average distance between scattering events), a large percentage of the carriers travel from the source to the drain without experiencing a single scattering event.</li>

- It can lead to super-fast devices.

: the average velocity of carriers >  $v_{dsat}$

# **Select Structure Survey**

- LDD (Lightly Doped Drain) Transistors

- The reduced dimension devices are more susceptible to hot-carrier effects.

- Lightly doped drain region (n<sup>-</sup> region) between the end of the channel and the drain

- Electric field  $\leftarrow$  The voltage drop in the n<sup>-</sup> region lowers the maximum

- $\rightarrow$ Carrier injection into the oxide

- →Oxide charging

Ch19 A Moder For scales dony. P692 Table 19.1. Short chaml Effet Jp & -Vi fuch y EL Lit (VIII ( Kumi S-D aunt - deplety gave rgm (ess chige is required for amount) 50 avaateritating 1 short chal min short had effect short chal effect S Twy (s) replus you at thresheld SVJ=VJ[shat-ch)-VJ(ly-ch)  $= -\frac{1}{6}\left(\frac{q_{RS}}{Q_{RS}} - \frac{Q_{RL}}{Q_{RL}}\right) = -\frac{8N_{B}W_{T}}{6}\frac{r_{s}}{L}\left(\frac{1+2w_{T}}{r_{s}} - 1\right)$ Lepter Depter Stry days the chart tog-chal  $= -\frac{r_{j}}{L}\left(\int_{H}\frac{2w_{T}}{r_{j}}-1\right)$ AND ANT VT To reduce, rj, wy needs to be reduced in drauh tory which effects preur. GNAWT Smalder & Jeger NA CO Also by express relation 2)<sup>1/3</sup> Lmin = 0.4 [r; Xo (Wist WD)<sup>2</sup>)<sup>1/3</sup> - Smiller Xo

haven charlàce Za 2 cry zm Witm Navor chal Mawor A 14/ Tax ZJ VT 212. depletion de NG is washed (?) in regins out of gave. Et ZI Mare chape repul to achine balan 1417. OVT = g NAWT. TIWT y 2 ~ WT, the publication

punch-thru (pich oper's simma) nt Sight meet! Runch-three current (gave loses correl) Ip & Vps Solut : NAT - WBWS, WD2 Valso inner C7 annel State almon inplating (File Undergate)