| Final Exam.                 | Subject            | Professor   | Student ID#                                                                   | Student Name | Score |

|-----------------------------|--------------------|-------------|-------------------------------------------------------------------------------|--------------|-------|

| Date: 2009.12.09            | Microelectronics 2 | Jong-Ho Lee |                                                                               |              |       |

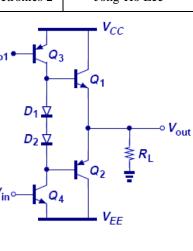

| 3. Following figure depicts |                    |             | (c) Using the result obtained in (b), determine the voltage gain if the stage |              |       |

improved push-pull stage reduce to crossover distortion. Turn-on voltages of  $Q_1$  and  $Q_2$  are  $V_{\rm BE1}$  and  $V_{\rm BE2}$ , respectively. Neglect the incremental resistance of  $D_1$  and  $D_2$ . Answer for the following questions. (22) (a) Two diodes  $(D_1 \text{ and } D_2)$ are used to avoid thermal runway in above power amplifier stage. How can we solve the thermal runaway problem? Briefly explain the principle. (7)

Answer)

1)If the diodes experience the same temperature change as the output transistors, Thus  $V_{D1}+V_{D2}$  will decrease at the same rate as  $V_{BE1}+V_{BE2}$ , with the result that the bias current remain constant.

(If the collector current is held constant, a rise in temperature in transistor results in a decrease in its  $V_{BE} \approx -2mV/^{\circ}C$

Alternately, if V<sub>BE</sub> is held constant and the temperature increases, the collector current increases.)

2)Using diode biasing prevents thermal runaway since the currents in  $Q_1$  and  $Q_2$  will track those of  $D_1$  and  $D_2$  as long as there  $I_s$ 's track with temperature.

Following equations show this accurately.

$V_{D1} + V_{D2} = V_T \ln \frac{I_{D1}I_{D2}}{I_{S,D1}I_{S,D2}}$  $V_{BE1} + V_{BE2} = V_T \ln \frac{I_{C1}I_{C2}}{I_{S,Q1}I_{S,Q2}}$  $\therefore \frac{I_{D1}I_{D2}}{I_{S,D1}I_{S,D2}} = \frac{I_{C1}I_{C2}}{I_{S,01}I_{S,02}} (I_{D1} \approx I_{D2}, I_{C1} \approx I_{C2})$

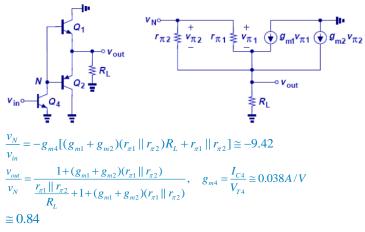

(b) Above push-pull stage employs a bias current of 1 mA in Q<sub>3</sub> and Q<sub>4</sub> and 10 mA in  $Q_1$  and  $Q_2$ . If  $Q_3$  and  $Q_4$  suffer from the Early effect and V<sub>A3</sub>=10 V and V<sub>A4</sub>=15 V, calculate the small-signal output impedance of the circuit if  $\beta_1$ =40 and  $\beta_2$ =20. (8) Answer)

Assuming

$$2r_{p} \text{ is small}$$

$$q_{m1} = g_{m2} = \frac{I_{c1,2}}{V_{T}} = 0.385A/V, \quad r_{\pi 1} = \frac{\beta_{1}}{g_{m1}} = \frac{40}{0.385} = 103.9\Omega$$

$$r_{\pi 2} = \frac{\beta_{2}}{g_{m2}} = \frac{20}{0.385} = 51.95\Omega, \quad r_{o3} = \frac{V_{A3}}{I_{c3}} = \frac{10}{0.001} = 10k\Omega$$

$$r_{o4} = \frac{V_{A4}}{I_{c4}} = \frac{15}{0.001} = 15k\Omega$$

$$R_{out} = \frac{v_{X}}{i_{X}} = \frac{r_{\pi 1} || r_{\pi 2} + r_{o3} || r_{o4}}{1 + (g_{m1} + g_{m2})(r_{\pi 1} || r_{\pi 2})} = \frac{6 \times 10^{3} + 34.63}{27.67} \cong 218.1\Omega$$

drives a load resistance of 8  $\Omega$ . (7) Answer)

$\frac{v_{out}}{v_{in}} = \frac{v_N}{v_{in}} \cdot \frac{v_{out}}{v_N} \cong -7.91$

4. We wish to design a Butterworth filter with a roll-off of 0.5dB at  $\omega = 0.8\omega_0$ . Determine the required order. (7)

$$|H(j\omega)| = \frac{1}{\sqrt{1 + \left(\frac{\omega}{\omega_o}\right)^{2n}}}$$

Answer)

$H(j0.8w_o) \cong 0.94(-0.5dB), \quad \frac{1}{1 + 0.8^{2n}} = 0.94^2, \quad n \cong 4.57$

$$H(j0.8w_o) \cong 0.94$$

∴n=5

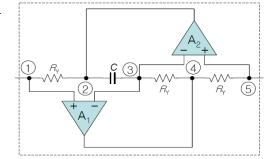

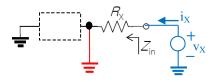

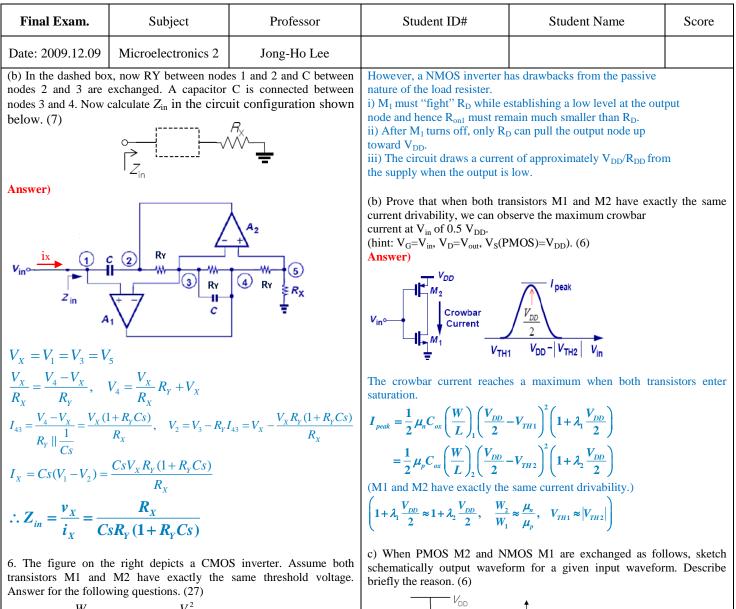

5. Following figure depicts main part of general impedance converter (GIC). Assume all op amps are ideal. Answer for the following questions. (14) (a) Using the circuit in the dashed box above, now we

implement following circuit. Calculate the  $Z_{in}$ . (7)

Answer)

$$Z_{in} = \frac{v_X}{i_Y} = R_X$$

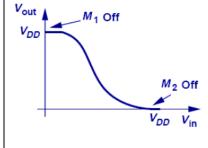

(a) Briefly describe the advantage of a CMOS inverter compared to an NMOS inverter which is composed of NMOS FET and a load resistance. (5)

Answer)

A CMOS inverter has following advantages.

i) The output low level is exactly equal to zero because  $V_{in}=V_{DD}$  ensures that  $M_2$  remains off.

ii) The circuit consumes zero static power for both high and low output levels.

Answer)

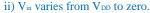

$i) V_{\text{in}} \text{ varies from zero to } V_{\text{DD}}$

| Final Exam.      | Subject            | Professor   | Student ID# | Student Name | Score |

|------------------|--------------------|-------------|-------------|--------------|-------|

| Date: 2009.12.09 | Microelectronics 2 | Jong-Ho Lee |             |              |       |

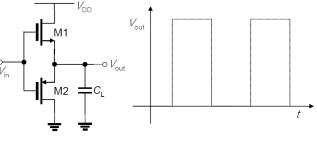

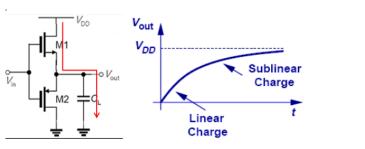

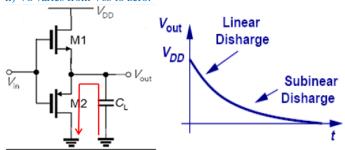

$V_{\rm in}$  jumps from 0 to  $V_{\rm DD}$  at t=t1 and  $V_{\rm out}$  begins to from 0. Transistor M1 turns on in saturation and M2 turns off, charging  $C_L$  toward VDD-V  $_{\rm TH1}$ . With the relatively constant current provided by M1,  $V_{\rm out}$  rises linearly until M1 enters the triode region and hence supplies a smaller current. The output voltage continues to rise, almost as if M1 acts as a resister, eventually approaching  $V_{\rm DD}\text{-}V_{\rm TH1}$  and forcing the drain current of M1 to zero.

M1 turns off and M2 turns on beginning to discharge C<sub>L</sub> from V<sub>DD</sub>-V<sub>TH1</sub> toward -V<sub>TH2</sub>. Transistor M2 operates in saturation until V<sub>DD</sub> falls by - V<sub>TH2</sub> above the gate voltage(=0), upon which I<sub>D2</sub> begins to decrease, slowing down the discharge. V<sub>out</sub> then gradually approaches -V<sub>TH2</sub>.

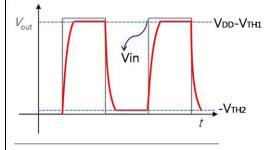

(d) For a given input waveform (square wave, t(logic 1) / t(logic 0) = 1), following output waveform (t(logic 1) / t(logic 0) < 1) is observed. Estimate what the cause is. (5)

## Answer)

For example, when NMOS and PMOS have the same current drivability, as  $(W/L)_1$  increases, the current drive of M1 increase. The circuit will exhibit then faster falling transition. As s result, the circuit will show t<sub>out0</sub> longer than t<sub>out1</sub>. As an another case, when  $(W/L)_2$  decreases, the current drive of M2 decrease. The circuit will exhibit then slower rising transition. Consequently, the circuit will also show t<sub>out0</sub> longer than t<sub>out1</sub>.

Thus, by varying  $(W/L)_1$  and  $(W/L)_2$ , the current drivability of M1 and M2 can be changed and the transition time will be changed as well.

Of course, The Ron difference between NMOS and PMOS will show a rising and falling time(TPLH, TPLH) difference and then  $t_{out0}$  and  $t_{out1}$  are different.

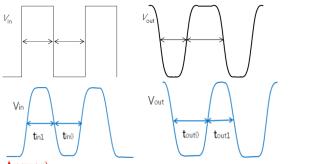

(e) We normally use NAND gate more frequently than NOR gate when we design a logic function. Why? (5) **Answer**)

(a)Three-input NAND gate

(b)Three-input NOR gate

The low mobility of holes requires a proportionally wider PMOS transistor to obtain a symmetric VTC and, more importantly, equal rise and fall time. Viewing the transistors in a three input NOR gate as resisters, we observe that the PMOS section suffers from three times the resistance of each PMOS device, quite larger than that of NAND gate because of the PMOS resistance NAND gate connected in parallel. Therefore, it creates a slower transition at the output that of NAND gate. On the other hand, to compare capacitance in the case of (a) with that of (b), (b) presents a capacitance of about  $7WLC_{ox}$  at each input, smaller than that of (a)( $5WLC_{ox}$ ). If wider PMOS transistors are employed to reduce Ron, then their gate capacitance increases and the situation even worsen. Consequently, the NAND gate less suffers from speed limitation.