# Silicon as a Mechanical Material

# KURT E. PETERSEN, MEMBER, IEEE

Abstract-Single-crystal silicon is being increasingly employed in a variety of new commercial products not because of its well-established electronic properties, but rather because of its excellent mechanical properties. In addition, recent trends in the engineering literature indicate a growing interest in the use of silicon as a mechanical material with the ultimate goal of developing a broad range of inexpensive, batch-fabricated, high-performance sensors and transducers which are easily interfaced with the rapidly proliferating microprocessor. This review describes the advantages of employing silicon as a mechanical material, the relevant mechanical characteristics of silicon, and the processing techniques which are specific to micromechanical structures. Finally, the potentials of this new technology are illustrated by numerous detailed examples from the literature. It is clear that silicon will continue to be aggressively exploited in a wide variety of mechanical applications complementary to its traditional role as an electronic material. Furthermore, these multidisciplinary uses of silicon will significantly alter the way we think about all types of miniature mechanical devices and components.

## I. INTRODUCTION

N THE SAME WAY that silicon has already revolutionized the way we think about electronics, this versatile material is  $\mathbf{I}$  now in the process of altering conventional perceptions of miniature mechanical devices and components [1]. At least eight firms now manufacture and/or market silicon-based pressure transducers [2] (first manufactured commercially over 10 years ago), some with active devices or entire circuits integrated on the same silicon chip and some rated up to 10 000 psi. Texas Instruments has been marketing a thermal point head [3] in several computer terminal and plotter products in which the active printing element abrasively contacting the paper is a silicon integrated circuit chip. The crucial detector component of a high-bandwidth frequency synthesizer sold by Hewlett-Packard is a silicon chip [4] from which cantilever beams have been etched to provide thermally isolated regions for the diode detectors. High-precision alignment and coupling assemblies for fiber-optic communications systems are produced by Western Electric from anisotropically etched silicon chips simply because this is the only technique capable of the high accuracies required. Within IBM, ink jet nozzle arrays and charge plate assemblies etched into silicon wafers [5] have been demonstrated, again because of the high precision capabilities of silicon IC technology. These examples of silicon micromechanics are not laboratory curiosities. Most are wellestablished, commercial developments conceived within about the last 10 years.

The basis of micromechanics is that silicon, in conjunction with its conventional role as an electronic material, and taking advantage of an already advanced microfabrication technology, can also be exploited as a high-precision high-strength highreliability mechanical material, especially applicable wherever miniaturized mechanical devices and components must be integrated or interfaced with electronics such as the examples given above.

The continuing development of silicon micromechanical applications is only one aspect of the current technical drive toward miniaturization which is being pursued over a wide front in many diverse engineering disciplines. Certainly silicon microelectronics continues to be the most obvious success in the ongoing pursuit of miniaturization. Four factors have played crucial roles in this phenomenal success story: 1) the active material, silicon, is abundant, inexpensive, and can now be produced and processed controllably to unparalleled standards of purity and perfection; 2) silicon processing itself is based on very thin deposited films which are highly amenable to miniaturization; 3) definition and reproduction of the device shapes and patterns are performed using photographic techniques which have also, historically, been capable of high precision and amenable to miniaturization; finally, and most important of all from a commercial and practical point of view, 4) silicon microelectronic circuits are batch-fabricated. The unit of production for integrated circuits-the wafer-is not one individual saleable item, but contains hundreds of identical chips. If this were not the case, we could certainly never afford to install microprocessors in watches or microwave ovens.

It is becoming clear that these same four factors which have been responsible for the rise of the silicon microelectronics industry can be exploited in the design and manufacture of a wide spectrum of miniature mechanical devices and components. The high purity and crystalline perfection of available silicon is expected to optimize the mechanical properties of devices made from silicon in the same way that electronic properties have been optimized to increase the performance. reliability, and reproducibility of device characteristics. Thinfilm and photolithographic fabrication procedures make it possible to realize a great variety of extremely small, highprecision mechanical structures using the same processes that have been developed for electronic circuits. High-volume batch-fabrication techniques can be utilized in the manufacture of complex, miniaturized mechanical components which may not be possible by any other methods. And, finally, new concepts in hybrid device design and broad new areas of application, such as integrated sensors [6], [7] and silicon heads (for printing and data storage), are now feasible as a result of the unique and intimate integration of mechanical and electronic devices which is readily accomplished with the fabrication methods we will be discussing here.

While the applications are diverse, with significant potential impact in several areas, the broad multidisciplinary aspects of silicon micromechanics also cause problems. On the one hand, the materials, processes, and fabrication technologies are all taken from the semiconductor industry. On the other hand, the applications are primarily in the areas of mechanical en-

Manuscript received December 2, 1981; revised March 11, 1982. The submission of this paper was encouraged after the review of an advance proposal.

The author was with IBM Research Laboratory, San Jose, CA 95193. He is now with Transensory Devices, Fremont, CA 94539.

| T. | AB | ٢L | Ε | I |

|----|----|----|---|---|

|----|----|----|---|---|

|                                 | Yield<br>Strength<br>(10 <sup>10</sup> dyne/cm <sup>2</sup> ) | Knoop<br>Hardness<br>(kg/mm <sup>2</sup> ) | Young's<br>Modulus<br>(10 <sup>12</sup> dyne/cm <sup>2</sup> ) | Density<br>(gr/cm <sup>3</sup> ) | Thermal<br>Conductivity<br>(W/cm°C) | Thermal<br>Expansion<br>(10 <sup>-6</sup> /°C) |

|---------------------------------|---------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|----------------------------------|-------------------------------------|------------------------------------------------|

| *Diamond                        | 53                                                            | 7000                                       | 10.35                                                          | 3.5                              | 20                                  | 1.0                                            |

| *SiC                            | 21                                                            | 2480                                       | 7.0                                                            | 3.2                              | 3.5                                 | 3.3                                            |

| *TiC                            | 20                                                            | 2470                                       | 4.97                                                           | 4.9                              | 3.3                                 | 6.4                                            |

| *Al <sub>2</sub> O <sub>3</sub> | 15.4                                                          | 2100                                       | 5.3                                                            | 4.0                              | 0.5                                 | 5.4                                            |

| *Si <sub>3</sub> N <sub>4</sub> | 14                                                            | 3486                                       | 3.85                                                           | 3.1                              | 0.19                                | 0.8                                            |

| *Iron                           | 12.6                                                          | 400                                        | 1.96                                                           | 7.8                              | 0.803                               | 12                                             |

| SiO <sub>2</sub> (fibers)       | 8.4                                                           | 820                                        | 0.73                                                           | 2.5                              | 0.014                               | 0.55                                           |

| *Si                             | 7.0                                                           | 850                                        | 1.9                                                            | 2.3                              | 1.57                                | 2.33                                           |

| Steel (max. strength)           | 4.2                                                           | 1500                                       | 2.1                                                            | 7.9                              | 0.97                                | 12                                             |

| W                               | 4.0                                                           | 485                                        | 4.1                                                            | 19.3                             | 1.78                                | 4.5                                            |

| Stainless Steel                 | 2.1                                                           | 660                                        | 2.0                                                            | 7.9                              | 0.329                               | 17.3                                           |

| Mo                              | 2.1                                                           | 275                                        | 3.43                                                           | 10.3                             | 1.38                                | 5.0                                            |

| AJ                              | 0.17                                                          | 130                                        | 0.70                                                           | 2.7                              | 2.36                                | 25                                             |

\*Single crystal. See Refs. 8, 9, 10, 11, 141, 163, 166.

gineering and design. Although these two technical fields are now widely divergent with limited opportunities for communication and technical interaction, widespread, practical exploitation of the new micromechanics technology in the coming years will necessitate an intimate collaboration between workers in *both* mechanical *and* integrated circuit engineering disciplines. The purpose of this paper, then, is to expand the lines of communication by reviewing the area of silicon micromechanics and exposing a large spectrum of the electrical engineering community to its capabilities.

In the following section, some of the relevant mechanical aspects of silicon will be discussed and compared to other more typical mechanical engineering materials. Section III describes the major "micromachining" techniques which have been developed to form the silicon "chips" into a wide variety of mechanical structures with IC-compatible processes amenable to conventional batch-fabrication. The next four sections comprise an extensive list of both commercial and experimental devices which rely crucially on the ability to construct miniature, high-precision, high-reliability, mechanical structures on silicon. This list was compiled with the primary purpose of illustrating the wide range of demonstrated applications. Finally, a discussion of present and future trends will wrap things up in Section VIII. The underlying message is that silicon micromechanics is not a diverging, unrelated, or independent extension of silicon microelectronics, but rather a natural, inevitable continuation of the trend toward more complex, varied, and useful integration of devices on silicon.

#### II. MECHANICAL CHARACTERISTICS OF SILICON

Any consideration of mechanical devices made from silicon must certainly take into account the mechanical behavior and properties of single-crystal silicon (SCS). Table I presents a comparative list of its mechanical characteristics. Although SCS is a brittle material, yielding catastrophically (not unlike most oxide-based glasses) rather than deforming plastically (like most metals), it certainly is not as fragile as is often believed. The Young's modulus of silicon  $(1.9 \times 10^{12} \text{ dyne/} \text{ cm}^2 \text{ or } 27 \times 10^6 \text{ psi})$  [8], for example, has a value approaching that of stainless steel, nickel, and well above that of quartz and most other borosilicate, soda-lime, and lead-alkali silicate glasses [9]. The Knoop hardness of silicon (850) is close to quartz, just below chromium (935), and almost twice as high as nickel (557), iron, and most common glasses (530) [10]. Silicon single crystals have a tensile yield strength (6.9  $\times 10^{10}$

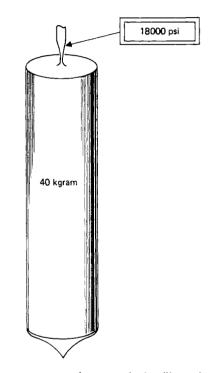

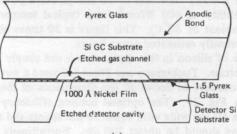

Fig. 1. Stresses encountered commonly in silicon single crystals are very high during the growth of large boules. Seed crystals, typically 0.20 cm in diameter and supporting 40-kg boules, experience stresses over  $1.25 \times 10^8$  Pa or about 18 000 psi in tension.

dyne/cm<sup>2</sup> or  $10^6$  psi) which is at least 3 times higher than stainless-steel wire [8], [11]. In practice, tensile stresses routinely encountered in seed crystals during the growth of large SCS boules, for example, can be over 18 000 psi (40-kg boule hanging from a 2-mm-diameter seed crystal, as illustrated in Fig. 1). The primary difference is that silicon will yield by fracturing (at room temperature) while metals usually yield by deforming inelastically.

Despite this quantitative evidence, we might have trouble intuitively justifying the conclusion that silicon is a strong mechanical material when compared with everyday laboratory and manufacturing experience. Wafers do break-sometimes without apparent provocation; silicon wafers and parts of wafers may also easily chip. These occurrences are due to several factors which have contributed to the misconception that silicon is mechanically fragile. First, single-crystal silicon is normally obtained in large (5-13-cm-diameter) wafers, typically only 10-20 mils (250 to 500  $\mu$ m) thick. Even stainless steel of these dimensions is very easy to deform inelastically. Silicon chips with dimensions on the order of  $0.6 \text{ cm} \times 0.6$ cm, on the other hand, are relatively rugged under normal handling conditions unless scribed. Second, as a single-crystal material, silicon has a tendency to cleave along crystallographic planes, especially if edge, surface, or bulk imperfections cause stresses to concentrate and orient along cleavage planes. Slip lines and other flaws at the edges of wafers, in fact, are usually responsible for wafer breakage. In recent years, however, the semiconductor industry has attacked this yield problem by contouring the edges of wafers and by regularly using wafer edge inspection instruments, specifically designed to detect mechanical damage on wafer edges and also to assure that edges are properly contoured to avoid the effects of stress concentration. As a result of these quality control improvements, wafer breakage has been greatly reduced and the intrinsic strength of silicon is closer to being realized in practice during wafer handling. Third, chipping is also a potential problem with brittle materials such as SCS. On whole wafers, chipping occurs for the same qualitative reasons as breaking and the solutions are identical. Individual die, however, are subject to chipping as a result of saw- or scribe-induced edge damage and defects. In extreme cases, or during rough handling, such damage can also cause breakage of or cracks in individual die. Finally, the high-temperature processing and multiple thin-film depositions commonly encountered in the fabrication of IC devices unavoidably result in internal stresses which, when coupled with edge, surface, or bulk imperfections, can cause concentrated stresses and eventual fracture along cleavage planes.

These factors make it clear that although high-quality SCS is intrinsically strong, the apparent strength of a particular mechanical component or device will depend on its crystallographic orientation and geometry, the number and size of surface, edge, and bulk imperfections, and the stresses induced and accumulated during growth, polishing, and subsequent processing. When these considerations have been properly accounted for, we can hope to obtain mechanical components with strengths exceeding that of the highest strength alloy steels.

General rules to be observed in this regard, which will be restated and emphasized in the following sections, can be formulated as follows:

1) The silicon material should have the lowest possible bulk, surface, and edge crystallographic defect density to minimize potential regions of stress concentration.

2) Components which might be subjected to severe friction, abrasion, or stress should be as small as possible to minimize the total number of crystallographic defects in the mechanical structure. Those devices which are never significantly stressed or worn could be quite large; even then, however, thin silicon wafers should be mechanically supported by some techniquesuch as anodic bonding to glass-to suppress the shock effects encountered in normal handling and transport.

3) All mechanical processing such as sawing, grinding, scribing, and polishing should be minimized or eliminated. These operations cause edge and surface imperfections which could result in the chipping of edges, and/or internal strains subsequently leading to breakage. Many micromechanical components should preferably be separated from the wafer, for example, by etching rather than by cutting.

4) If conventional sawing, grinding, or other mechanical operations are necessary, the affected surfaces and edges should be etched afterwards to remove the highly damaged regions.

5) Since many of the structures presented below employ anisotropic etching, it often happens that sharp edges and corners are formed. These features can also cause accumulation and concentration of stress damage in certain geometries. The structure may require a subsequent isotropic etch or other smoothing methods to round such corners.

6) Tough, hard, corrosion-resistant, thin-film coatings such as CVD SiC [12] or  $Si_3N_4$  should be applied to prevent direct mechanical contact to the silicon itself, especially in applications involving high stress and/or abrasion.

7) Low-temperature processing techniques such as highpressure and plasma-assisted oxide growth and CVD depositions, while developed primarily for VLSI fabrication, will be just as important in applications of silicon micromechanics. High-temperature cycling invariably results in high stresses within the wafer due to the differing thermal coefficients of expansion of the various doped and deposited layers. Lowtemperature processing will alleviate these thermal mismatch stresses which otherwise might lead to breakage or chipping under severe mechanical conditions.

As suggested by 6) above, many of the structural or mechanical disadvantages of SCS can be alleviated by the deposition of passivating thin films. This aspect of micromechanics imparts a great versatility to the technology. Sputtered quartz, for example, is utilized routinely by industry to passivate IC chips against airborne impurities and mild atmospheric corrosion effects. Recent advances in the CVD deposition (hightemperature pyrolytic and low-temperature RF-enhanced) of SiC [12] have produced thin films of extreme hardness, essentially zero porosity, very high chemical corrosion resistance, and superior wear resistance. Similar films are already used, for example, to protect pump and valve parts for handling corrosive liquids. As seen in Table I, Si<sub>3</sub>N<sub>4</sub>, an insulator which is routinely employed in IC structures, has a hardness second only to diamond and is sometimes even employed as a high-speed, rolling-contact bearing material [13], [14]. Thin films of silicon nitride will also find important uses in silicon micromechanical applications.

On the other end of the thin-film passivation spectrum, the gas-condensation technique marketed by Union Carbide for depositing the polymer parylene has been shown to produce virtually pinhole-free, low-porosity, passivating films in a high polymer form which has exceptional point, edge, and hole coverage capability [15]. Parylene has been used, for example, to coat and passivate implantable biomedical sensors and electronic instrumentation. Other techniques have been developed for the deposition of polyimide films which are already used routinely within the semiconductor industry [16] and which also exhibit superior passivating characteristics.

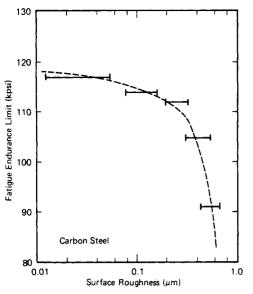

One excellent example of the unique qualities of silicon in the realization of high-reliability mechanical components can be found in the analysis of mechanical fatigue in SCS structures. Since the initiation of fatigue cracks occurs almost exclusively at the surfaces of stressed members, the rate of fatigue depends strongly on surface preparation, morphology, and defect density. In particular, structural components with highly polished surfaces have higher fatigue strengths than those with rough surface finishes as shown in Fig. 2 [17]. Passivated surfaces of polycrystalline metal alloys (to prevent intergrain diffusion of  $H_2O$  exhibit higher fatigue strengths than unpassivated surfaces, and, for the same reasons, high water vapor content in the atmosphere during fatigue testing will significantly decrease fatigue strength. The mechanism of fatigue, as these effects illustrate, are ultimately dependent on a surface-defect-initiation process. In polycrystalline ma-

Fig. 2. Generally, mechanical qualities such as fatigue and yield strength improve dramatically with surface roughness and defect density. In the case of silicon, it is well known that the electronic and mechanical perfection of SCS surfaces has been an indispensable part of integrated circuit technology. Adapted from Van Vlack [17].

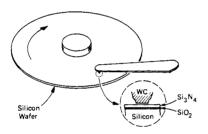

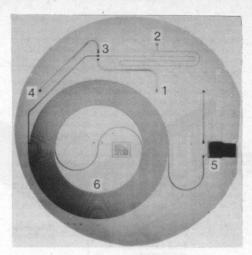

Fig. 3. A rotating MNOS disk storage device demonstrated by Iwamura *et al.* [21]. The tungsten-carbide probe is in direct contact with the nitride-coated silicon wafer as the wafer rotates at 3600 r/min. Signals have been recorded and played back on such a system at video rates. Wear of the WC probe was a more serious problem than wear of the silicon disk.

terials, these surface defects can be inclusions, grain boundaries, or surface irregularities which concentrate local stresses. It is clear that the high crystalline perfection of SCS together with the extreme smoothness and surface perfection attainable by chemical etching of silicon should yield mechanical structures with intrinsically high fatigue strengths [18]. Even greater strengths of brittle materials can be expected with additional surface treatments [9]. Since hydrostatic pressure has been shown to increase fatigue strengths [19], any film which places the silicon surface under compression should decrease the initiation probability of fatigue cracks. Si<sub>3</sub>N<sub>4</sub> films, for example, tend to be under tension [20] and therefore impart a compressive stress on the underlying silicon surface. Such films may be employed to increase the fatigue strength of SCS mechanical components. In addition, the smoothness, uniformity, and high yield strength of these thin-film amorphous materials should enhance overall component reliability.

A new rotating disk storage technology which has recently been demonstrated by Iwamura *et al.* [21] not only illustrates some of the unique advantages derived from the use of silicon as a mechanical material but also indicates how well silicon, combined with wear-resistant  $Si_3N_4$  films, can perform in demanding mechanical applications. As indicated in Fig. 3, data storage was accomplished by an MNOS charge-storage process in which a tungsten carbide probe is placed in direct contact with a 3-in-diameter silicon wafer, rotating at 3600 r/min. The wafer is coated with 2-nm  $SiO_2$  and 49-nm  $Si_3N_4$ , while the carbide probe serves as the top metal electrode. Positive voltage pulses applied to the metal probe as the silicon passes beneath will cause electrons to tunnel through the thin  $SiO_2$  and become trapped in the  $Si_3N_4$  layer. The trapped charge can be detected as a change in capacitance through the same metal probe, thereby allowing the signal to be read. Iwamura et al. wrote and read back video signals with this device over 10<sup>6</sup> times with little signal degradation, at data densities as high as  $2 \times 10^6$  bits/cm<sup>2</sup>. The key problems encountered during this experiment were associated with wear of the tungsten carbide probe, not of the silicon substrate or the thin nitride layer itself. Sharply pointed probes, after scraping over the Si<sub>3</sub>N<sub>4</sub> surface for a short time, were worn down to a 10- $\mu$ m by 10- $\mu$ m area, thereby increasing the active recording surface per bit and decreasing the achievable bit density. After extended operation, the probe continued to wear while a barely resolvable 1-nm roughness was generated in the hard silicon nitride film. Potential storage densities of 10<sup>9</sup> bits/cm<sup>2</sup> were projected if appropriate recording probes were available. Contrary to initial impressions, the rapidly rotating, harshly abraided silicon disk is not a major source of problems even in such a severely demanding mechanical application.

#### III. MICROMECHANICAL PROCESSING TECHNIQUES

# Etching

Even though new techniques—and novel applications of old techniques—are continually being developed for use in micromechanical structures, the most powerful and versatile processing tool continues to be etching. Chemical etchants for silicon are numerous. They can be isotropic or anisotropic, dopant dependent or not, and have varying degrees of selectivity to silicon, which determines the appropriate masking material(s). Table II gives a brief summary of the characteristics of a number of common wet silicon etches. We will not discuss plasma, reactive-ion, or sputter etching here, although these techniques may also have a substantial impact on future silicon micromechanical devices.

Three etchant systems are of particular interest due to their versatility: ethylene diamine, pyrocatechol, and water (EDP) [22]; KOH and water [23]; and HF, HNO<sub>3</sub>, and acetic acid CH<sub>3</sub>OOH (HNA) [24], [25]. EDP has three properties which make it indispensable for micromachining: 1) it is anisotropic, making it possible to realize unique geometries not otherwise feasible; 2) it is highly selective and can be masked by a variety of materials, e.g., SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Cr, and Au; 3) it is dopant dependent, exhibiting near zero etch rates on silicon which has been highly doped with boron [26], [27].

KOH and water is also orientation dependent and, in fact, exhibits much higher (110)-to-(111) etch rate ratios than EDP. For this reason, it is especially useful for groove etching on (110) wafers since the large differential etch ratio permits deep, high aspect ratio grooves with minimal undercutting of the masks. A disadvantage of KOH is that  $SiO_2$  is etched at a rate which precludes its use as a mask in many applications. In structures requiring long etching times,  $Si_3N_4$  is the preferred masking material for KOH.

HNA is a very complex etch system with highly variable etch rates and etching characteristics dependent on the silicon dopant concentration [28], the mix ratios of the three etch

| Etchant<br>(Diluent)                                         | Typical<br>Compo-<br>sitions | Temp<br>°C | Etch<br>Rate<br>(µm/min) | Anisotropic<br>(100)/(111<br>Etch Rate<br>Ratio |                                                                                    | Masking Films<br>(etch rate of mask)                                 | References               |

|--------------------------------------------------------------|------------------------------|------------|--------------------------|-------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------|

| HF<br>HNO3<br>(water,                                        | 10 m.l<br>30 m.l<br>80 m.l   | 22         | 0.7-3.0                  | 1:1                                             | $\leq 10^{17}$ cm <sup>-3</sup> n or p<br>reduces etch rate<br>by about 150        | SiO <sub>2</sub> (300Å/min)                                          | 24,25,28,30              |

| <u>CH3COOH)</u>                                              | 25 mi<br>50 mi<br>25 mi      | 22         | 40                       | 1:1                                             | no dependence                                                                      | Si <sub>3</sub> N4                                                   |                          |

|                                                              | 9 mai<br>75 mai<br>30 mai    | 22         | 7.0                      | 1:1                                             |                                                                                    | SiO <sub>2</sub> (700Å/min)                                          |                          |

| Ethylene diamine<br>Pyrocatechol<br>(water)                  | 750 mai<br>120 gr<br>100 mai | 115        | 0.75                     | 35:1                                            | ≥7 x 10 <sup>19</sup> cm <sup>-3</sup> boron<br>reduces etch rate                  | SiO <sub>2</sub> (2Å/min)<br>Si <sub>3</sub> N <sub>4</sub> (1Å/min) | 20,26,27,35,             |

|                                                              | 750 mli<br>120 gr<br>240 mli | 115        | 1.25                     | 35:1                                            | by about 50                                                                        | Mu,Cr,Ag,Cu,Ta                                                       | •3,••                    |

| KOH<br>( <u>water</u> , isopropyl)                           | 44 gr<br>100 ml              | 85         | 1.4                      | <b>400</b> :1                                   | ≥10 <sup>20</sup> cm <sup>-3</sup> boron<br>reduces etch rate                      | Si <sub>3</sub> N <sub>4</sub><br>SiO <sub>2</sub> (14Å/min)         | 23,32,33,36,<br>37,38,42 |

|                                                              | 50 gr<br>100 mai             | 50         | 1.0                      | 400:1                                           | by about 20                                                                        | - ,                                                                  |                          |

| H <sub>2</sub> N <sub>4</sub><br>( <u>water</u> , isopropyl) | 100 ml<br>100 ml             | 100        | 2.0                      |                                                 | no dependence                                                                      | SiO <sub>2</sub><br>Al                                               | 40,41                    |

| NaOH<br>(water)                                              | 10 gr<br>100 mai             | 65         | 0.25-1.0                 |                                                 | $\geq 3 \times 10^{20}$ cm <sup>-3</sup> boron<br>reduces etch rate<br>by about 10 | Si <sub>3</sub> N <sub>4</sub><br>SiO <sub>2</sub> (7Å/min)          | 34                       |

TABLE II

components, and even the degree of etchant agitation, as shown in Fig. 4 and Table II. Unfortunately, these mixtures can be difficult to mask, since  $SiO_2$  is etched somewhat for all mix ratios. Although  $SiO_2$  can be used for relatively short etching times and  $Si_3N_4$  or Au can be used for longer times, the masking characteristics are not as desirable as EDP in micromechanical structures where very deep patterns (and therefore highly resistant masks) are required.

As described in detail by several authors, SCS etching takes place in four basic steps [30], [31]: 1) injection of holes into the semiconductor to raise the silicon to a higher oxidation state Si<sup>+</sup>, 2) the attachment of hydroxyl groups OH<sup>-</sup> to the positively charged Si, 3) the reaction of the hydrated silicon with the complexing agent in the solution, and 4) the dissolution of the reacted products into the etchant solution. This process implies that any etching solution must provide a source of holes as well as hydroxyl groups, and must also contain a complexing agent whose reacted species is soluble in the etchant solution. In the HNA system, both the holes and the hydroxyl groups are effectively supplied by the strong oxidizing agent HNO<sub>3</sub>, while the flourine from the HF forms the soluble species H<sub>2</sub>SiF<sub>6</sub>. The overall reaction is autocatalytic since the HNO<sub>3</sub> plus trace impurities of HNO<sub>2</sub> combine to form additional HNO<sub>2</sub> molecules.

$$HNO_2 + HNO_3 + H_2O \rightarrow 2HNO_2 + 2OH^- + 2h^+$$

.

This reaction also generates holes needed to raise the oxidation state of the silicon as well as the additional OH<sup>-</sup> groups necessary to oxidize the silicon. In the EDP system, ethylene diamine and H<sub>2</sub>O combine to generate the holes and the hydroxyl groups, while pyrocatechol forms the soluble species  $Si(C_6H_4O_2)_3$ . Mixtures of ethylene diamine and pyrocatechol

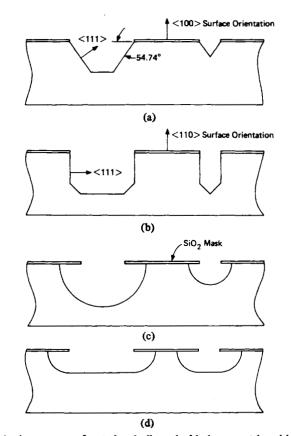

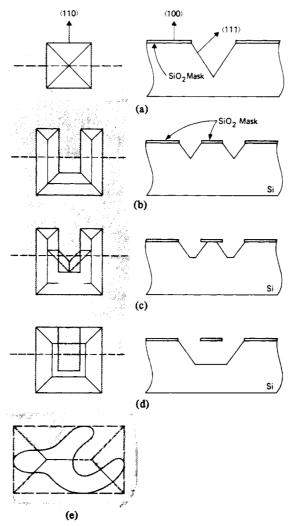

Fig. 4. A summary of wet chemically etched hole geometries which are commonly used in micromechanical devices. (a) Anisotropic etching on (100) surfaces. (b) Anisotropic etching on (110) surfaces. (c) Isotropic etching with agitation. (d) Isotropic etching without agitation. Adapted from S. Terry [29].

without water will not etch silcon. Other common silicon etchants can be analyzed in the same manner.

Since the etching process is fundamentally a charge-transfer mechanism, it is not surprising that etch rates might be dependent on dopant type and concentration. In particular, highly doped material in general might be expected to exhibit higher etch rates than lightly doped silicon simply because of the greater availability of mobile carriers. Indeed, this has been shown to occur in the HNA system (1:3:8) [28], where typical etch rates are 1-3  $\mu$ m/min at p or n concentrations >10<sup>18</sup> cm<sup>-3</sup> and essentially zero at concentrations <10<sup>17</sup> cm<sup>-3</sup>.

Anisotropic etchants, such as EDP [26], [27] and KOH [32], on the other hand, exhibit a different preferential etching behavior which has not yet been adequately explained. Etching decreases effectively to zero in samples heavily doped with boron ( $\sim 10^{20}$  cm<sup>-3</sup>). The atomic concentrations at these dopant levels correspond to an average separation between boron atoms of 20-25 Å, which is also near the solid solubility limit  $(5 \times 10^{19} \text{ cm}^{-3})$  for boron substitutionally introduced into the silicon lattice. Silicon doped with boron is placed under tension as the smaller boron atom enters the lattice substitutionally, thereby creating a local tensile stress field. At high boron concentrations, the tensile forces became so large that it is more energetically favorable for the excess boron (above  $5 \times 10^{19}$  cm<sup>-3</sup>) to enter interstitial sites. Presumably, the strong B-Si bond tends to bind the lattice more rigidly, increasing the energy required to remove a silicon .... high enough to stop etching altogether. Alternatively, since this etch-stop mechanism is not observed in the HNA system (in which the HF component can readily dissolve  $B_2O_3$ ), perhaps the boron oxides and hydroxides initially generated on the silicon surface are not soluble in the KOH and EDP etchants. In this case, high enough surface concentrations of boron, converted to boron oxides and hydroxides in an intermediate chemical reaction, would passivate the surface and prevent further dissolution of the silicon. The fact that KOH is not stopped as effectively as EDP by p<sup>+</sup> regions is a further indication that this may be the case since EDP etches oxides at a much slower rate than KOH. Additional experimental work along these lines will be required to fully understand the etchstopping behavior of boron-doped silicon.

The precise mechanisms underlying the nature of chemical anisotropic (or orientation-dependent) etches are not well understood either. The principal feature of such etching behavior in silicon is that (111) surfaces are attacked at a much slower rate than all other crystallographic planes (etchrate ratios as high as 1000 have been reported). Since (111) silicon surfaces exhibit the highest density of atoms per square centimeter, it has been inferred that this density variation is responsible for anisotropic etching behavior. In particular, the screening action of attached H<sub>2</sub>O molecules (which is more effective at high densities, i.e., on (111) surfaces) decreases the interaction of the surface with the active molecules. This screening effect has also been used to explain the slower oxidation rate of (111) silicon wafers over (100). Another factor involved in the etch-rate differential of anisotropic etches is the energy needed to remove an atom from the surface. Since (100) surface atoms each have two dangling bonds, while (111) surfaces have only one dangling bond, (111) surfaces are again expected to etch more slowly. On the other hand, the differences in bond densities and the energies required to remove surface atoms do not differ by much more than a factor of two among the various planes, so it is difficult to use

Fig. 5. (a) Typical pyramidal pit, bounded by the (111) planes, etched into (100) silicon with an anisotropic etch through a square hole in an oxide mask. (b) Type of pit which is expected from an anisotropic etch with a slow convex undercut rate. (c) The same mask pattern can result in a substantial degree of undercutting using an etchant with a fast convex undercut rate such as EDP. (d) Further etching of (c) produces a cantilever beam suspended over the pit. (e) Illustration of the general rule for anisotropic etch undercutting assuming a "sufficiently long" etching time.

these factors alone to explain etch rate differentials in the range of several hundred or more [33] which is maintained over a relatively large temperature range. This implies that some screening effects must also play a role. It seems likely that the full explanation of anisotropic etching behavior is a combination of all these factors.

Since anisotropic etching will be a particularly useful tool in the micromachining of structures described below, some detailed descriptions of the practical engineering aspects of this complex subject are deserved.

Consider a (100) oriented silicon wafer covered with  $SiO_2$ . A simple rectangular hole etched in the  $SiO_2$  (and oriented on the surface in the (110) directions) will result in the familiar pyramidal-shaped pit shown in Fig. 5(a) when the silicon is etched with an anisotropic etchant. The pit is bounded by (111) crystallographic surfaces, which are invariably the slowest etching planes in silicon. Note that this mask pattern consists only of "concave" corners and very little undercutting of the mask will occur if it is oriented properly. Undercutting due to mask misalignment has been discussed by several workers including Kendall [33], Pugacz-Muraszkiewicz [34], and Bassous [35]. The more complicated mask geometry shown in Fig. 5(b) includes two convex corners. Convex corners, in general, will be undercut by anisotropic etches at a rate determined by the magnitude of the maximum etch rate, by the etch rate ratios for various crystallographic planes, and by the amount of local surface area being actively attacked. Since the openings in the mask can only support a certain flux of reactants, the net undercut etch rate can be reduced, for example, by using a mask with very narrow openings. On the other hand, the undercut etch rate can be increased by incorporating a vertical etch stop layer (such as a heavily boron-doped buried layer which will limit further downward etching); in this case, the reactant flux from the bottom of the etched pit is eventually reduced to near zero when the etch-stopping layer is exposed, so the total flux through the mask opening is maintained by an increased etch rate in the horizontal direction, i.e., an increased undercut rate.

In Fig. 5(b), the convex undercut etch rate is assumed to be slow, while in Fig. 5(c) it is assumed to be fast. Total etching time is also a factor, of course. Convex corners will continue to be undercut until, if the silicon is etched long enough, the pit eventually becomes pyramidal, bounded again by the slow etching (111) surfaces, with the undercut portions of the mask (a cantilever beam in this case) suspended over it, as shown in Fig. 5(d). As an obvious extension of these considerations [34], a general rule can be formulated which is shown graphically in Fig. 5(e). If the silicon is etched long enough, any arbitrarily shaped closed pattern in a suitable mask will result in a rectangular pit in the silicon, bounded by the (111) surfaces, oriented in the (110) directions, with dimensions such that the pattern is perfectly inscribed in the resulting rectangle.

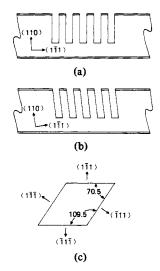

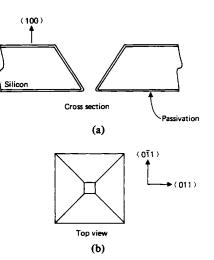

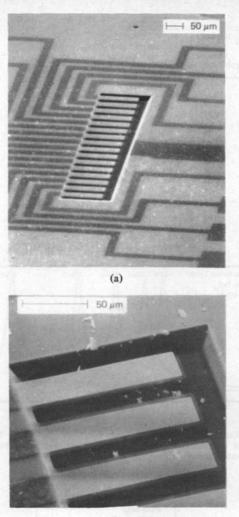

As expected, different geometries are possible on other crystallographic orientations of silicon [35]-[38]. Fig. 4 illustrates several contours of etched holes observed with isotropic etchants as well as anisotropic etchants acting on various orientations of silicon. In particular, (110) oriented wafers will produce vertical etched surfaces with essentially no undercut when lines are properly aligned on the surface. Again, the (111) planes are the exposed vertical surfaces which resist the attack of the etchant. Long, deep, closely spaced grooves have been etched in (110) wafers as shown in Fig. 6(a). Even wafers not exactly oriented in the (110) direction will exhibit this effect. Fig. 6(b) shows grooves etched into a surface which is 10° off the (110) direction-the grooves are simply oriented 10° off normal [36]. Note also that the four vertical (111) planes on a (110) wafer are not oriented 90° with respect to each other, as shown in the plan view of Fig. 6(c).

Crystallographic facet definition can also be observed after etching (111) wafers, even though long times are required due to the slow etch rate of (111) surfaces. The periphery of a hole etched through a round mask, for example, is hexagonal, bounded on the bottom, obviously, by the (111) surface [39]. The six sidewall facets are defined by the other (111) surfaces; three slope inward toward the center of the hole and the other three slope outward. The six inward and outward sloping surfaces alternate as shown in Fig. 7.

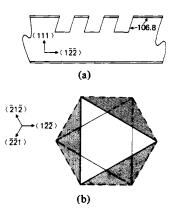

#### Electrochemical Etching

While electrochemical etching (ECE) of silicon has been studied and basically understood for a number of years [45]-[47], practical applications of the technique have not yet been fully realized. At least part of the reason ECE is not now a popular etching procedure is due to the fact that previous

Fig. 6. Anisotropic etching of (110) wafers. (a) Closely spaced grooves on normally oriented (110) surface. (b) Closely spaced grooves on misoriented wafer. (c) These are the orientations of the (111) planes looking down on a (110) wafer.

Fig. 7. Anisotropic etching of (111) silicon surfaces. (a) Wafer cross section with the steep sidewalls which would be found from grooves aligned along the (122) direction. (b) Top view of a hole etched in the (111) surface with three inward sloping and three undercut sidewalls, all (111) crystallographic planes.

Fig. 8. Uniform electrochemical etching of wafer surfaces has been practiced in the past by making electrical contact either to the back (a) or to the front (b) of the wafer (with suitable protection for the current carrying leads). A positive voltage applied to the silicon causes an accumulation of holes at the silicon/solution interface and etching occurs. A negatively biased platinum electrode in the HFbased solution completes the circuit.

implementations of ECE offered no real advantage over the conventional, isotropic, dopant-dependent formulations discussed in the preceding section. As shown by Fig. 8(a) and (b), in typical ECE experiments electrical contact is made to the front or back of the wafer (the contacted region suitably protected from the etching solution, e.g., with wax or a special holding fixture) and the wafer is either totally immersed or is slowly lowered into the solution while a constant current flows between the positively biased silicon electrode and the negative platinum electrode. Since etching is still, principally, a matter of charge transfer, the fundamental steps are the same as discussed above. The etchants employed, however, are typically HF/H<sub>2</sub>O solutions. Since H<sub>2</sub>O is not as strong an oxidizing agent as HNO<sub>3</sub>, very little silicon etching occurs (<1 Å/min) when the current flow is zero. Oxidation, then, is promoted by applying a positive voltage to the silicon which causes an accumulation of holes in the silicon at the Si/solution interface resulting in an accumulation of OH<sup>-</sup> in the solution at the interface. Under these conditions, oxidation of the silicon surface proceeds very rapidly while the oxide is readily dissolved by the HF. Holes, which are transported to the negative platinum electrode (cathode) as H<sup>+</sup> ions, are released there in the form of hydrogen gas bubbles. In addition, excess holeelectron pairs can be created at the silicon surface by optical excitation, thereby increasing the etch rate.

Since the oxidation rate is controlled by current flow and optical effects, it is again clear that the etching characteristics will depend not only on dopant type and resistivity but also on the arrangement of p and n layers in the wafer interior. In particular, ECE has been employed successfully to remove heavily doped substrates (through which large currents are easily conducted) leaving behind more lightly doped epi-layer membranes (which conduct smaller currents, thereby etching more slowly) in all possible dopant configurations (p on p<sup>+</sup>, p on n<sup>+</sup>, n on p<sup>+</sup>, n on n<sup>+</sup>) [48], [49].

Localized electrochemical jet etching has been used to generate small holes or thinned regions in silicon wafers. A narrow stream of etchant is incident on one side of a wafer while a potential is applied between the wafer and the liquid stream. Extremely rapid etching occurs at the point of contact due to the thorough agitation of the solution, the continual arrival of fresh solution at the interface, and the rapid removal of reacted products.

A more useful electrochemical procedure using an anisotropic etchant has been developed by Waggener [50] for KOH and more recently by Jackson *et al.* [51] for EDP. Instead of relying on the electric current flowing through the solution to actively etch the silicon, a voltage bias on an n-type epitaxial layer is employed to stop the dissolution of the p-type silicon substrate at the n-type epitaxial layer. This technique has the advantage of retaining all the anisotropic etching characteristics of KOH and EDP without the need for a buried  $p^+$  layer. Such  $p^+$  films, while serving as simple and effective etch-stop layers, can also introduce undesirable mechanical strains in the remaining membrane which would not be present in the electrochemically stopped, uniformly doped membrane.

When ECE is performed at very low current densities, or in etchant solutions highly deficient in OH<sup>-</sup> (such as concentrated 48-percent HF), the silicon is not fully oxidized during etching and a brownish film is formed. In early ECE work, the brownish film was etched off later in a conventional HNA slow silicon etch, or the ECE solution was modified with H<sub>2</sub>SO<sub>4</sub> to minimize its formation [47]. This film has since been identified as single-crystal silicon permeated with a dense network of very fine holes or channels, from much less than 1  $\mu$ m to several micrometers in diameter, preferentially oriented in the direction of current flow [52], [53]. The thickness of the layer can be anywhere from micrometers up to many mils. Porous silicon, as it is called, has a number of interesting properties. Its average density decreases with increasing applied current

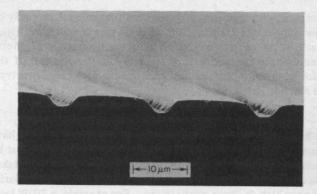

Fig. 9. SEM profile of laser-etched grooves [56]. The horizontal bar indicates 10  $\mu$ m. Conditions were 100 torr Cl<sub>2</sub>, 5.5-W multiline argonion laser, f/10 focusing, single scan at 90  $\mu$ m/s. Photo courtesy of D. Ehrlich.

density to as low as 10 percent of normal silicon. Since it is so porous, gases readily diffuse into the structure so that the high-temperature oxidation, for example, of a relatively thick  $(\sim 4-\mu m)$  porous silicon layer can be completed in a very short time (30 min at 1100°C) [52]. Several studies have been undertaken to determine the feasibility of using such deeply oxidized porous silicon regions as a planarizing, deep IC isolation technique [54]. The porous regions are defined by using Si<sub>3</sub>N<sub>4</sub> masking films which are attacked relatively slowly by the concentrated HF ECE solution. Problems, however, encountered in the control and elimination of impurities trapped in the porous silicon "sponge-like" material, stressrelated effects, and enhanced leakage currents in devices isolated by this technique have been difficult to overcome. Mechanical devices, on the other hand, may not be restricted by these disadvantages.

Besides magnifying the effective thermal oxidation rates, porous silicon can also be chemically attacked at enormously high rates. As expected, the interiors of the pores provide a very large surface area for exposure to the etchant solution. Wafers covered with  $100-\mu$ m-thick porous silicon layer, for example, will actually shatter and explode when immersed in fast-etching HNA solutions.

Gradations in the porosity of the layer can be simply realized by changing the current with time. In particular, a low current density followed by a high current density will result in a high-porosity region covered with a low-porosity film. Since the porous region is still a single crystal covered with small holes (reported to be near 100 Å on the surface), it is not surprising that single-crystal epitaxial layers have been g own over porous silicon regions, as demonstrated by Unagami and Seki [55]. Once the thickness of the epi-layer corresponds to several times the diameter of the surface pores, it has been verified that the layer will be a uniform single crystal since the crystallinity of the substrate was maintained throughout, despite its permeation with fine holes.

A relatively new tool added to the growing list of micromechanical processing techniques is laser etching. Very high instantaneous etch rates have been observed when high-intensity lasers are focussed on a silicon surface in the presence of some gases. In particular, 20-30 MW/cm<sup>2</sup> of visible argon-ion laser radiation, scanned at rates of 90  $\mu$ m/s in atmospheres of HCl and Cl<sub>2</sub> produced 3- $\mu$ m-deep grooves [56], as shown in Fig. 9. At least part of the etching reaction occurs solely as a result of local thermal effects. It has been known for some time that silicon will be vigorously attacked by both these gases at temperatures above about 1000°C. Recent experiments in laser annealing have verified that silicon can easily be raised above the melting point at these power densities. There is still some controversy concerning the magnitude of photochemical effects, which might aid in the dissociation of the chlorine-based molecules and enhance the etch rate. In a typical reaction, for example,

$$4HCl + Si_{solid} \rightarrow 2H_2 + SiCl_4$$

Although many applications in the area of IC fabrication have been suggested for laser etching, the fact that the laser must be scanned over the entire wafer and the etching therefore takes place "serially," net processing time per wafer will necessarily by very high in these applications. For example, a 20-W laser at a power density of  $10^7$  W/cm<sup>2</sup> etching a 1- $\mu$ m layer will require over 100 h to completely scan a 4-in-diameter wafer even if etch rates of 100  $\mu$ m/s are realized. Laser etching is clearly applicable only in special micromachining processing requirements such as the various contours which may be required in print-heads, recording-heads, or other miniature mechanical structures integrated with electronics on the same silicon ship. Versatile as they are, conventional, isotropic, anisotropic, electrochemical, and ion-etching processes exhibit a limited selection of etched shapes. On the other hand, the significant key advantage of laser etching is that nearly any shape or contour can be generated with laser etching in a gaseous atmosphere simply by adjusting the local exposure dose continuously over the etched region. Such a capability will be extremely useful in the realization of complex mechanical structures in silicon.

# Epitaxial Processes

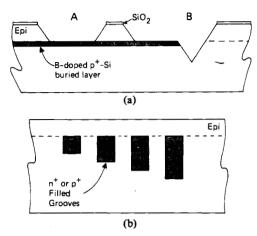

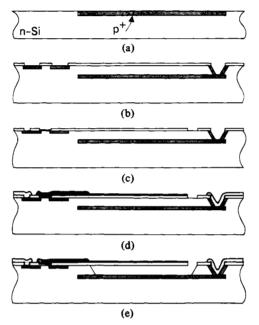

While the discussion up to this point has concentrated on material removal as a micromachining technique, material addition, in the form of thin film deposition or growth, metal plating, and epitaxial growth are also important structural tools. Deposited thin films have obvious applications in passivation, wear resistance, corrosion protection, fatigue strength enhancement (elaborated on in Section II), and as very thin, high-precision spacers such as those employed in hybrid surface acoustic wave amplifiers and in other thin-film devices. On the other hand, epitaxy has the important property of maintaining the highly perfect single-crystal orientation of the substrate. This means that complex vertical and/or horizontal dopant distributions (i.e., fast and slow etching regions for subsequent micromachining by etching) can be generated over many tens of micrometers without compromising the crystal structure or obviating subsequent anisotropic processes. Etchstop layered structures are important examples and will be considered in more detail in Section VI. Fig. 10(a), however, briefly illustrates two simple configurations: hole A is a simple etch-stop hole using anisotropic etching and a p<sup>+</sup> boron-doped buried layer while hole B is a multilevel hole in which the epilayer and a portion of the lightly doped substrate have been anisotropically etched from the edge of the p<sup>+</sup> buried region. One obvious advantage of these methods is that the depth of the hole is determined solely by the thickness of the epi-layer. This thickness can be controlled very accurately and measured even before etching begins. Such depth control is crucial in many micromechanical applications we will discuss later, particularly in fiber and integrated optics.

Where the goal of IC manufacturing is to fabricate devices as small as possible (indeed, diffusions deeper than a few micrometers are very difficult and/or time-consuming), a necessary feature of most micromechanical processing techniques is the

Fig. 10. (a) Since anisotropic etchants such as KOH and EDP exhibit reduced etch rates on silicon heavily doped with boron, many useful structures have been realized by growing epi over a diffused region to form a buried etch-stop layer. (b) Diagram showing how epitaxial silicon could be grown preferentially [57] in vertical-walled grooves. Doped grooves with large cross sections (>25  $\times$  25  $\mu$ m) can then be buried beneath an ordinary epi-layer.

ability to generate structures on the order of tens or even hundreds of micrometers. Both etching and epitaxial deposition possess this property. Epitaxial silicon can be grown at rates of 1  $\mu$ m/min, so that layers even greater than 100  $\mu$ m are readily attainable. In addition, the process parameters can be accurately controlled to allow the growth of complex threedimensional patterns. For example, since the growth rate depends critically on temperature and gas-mixing dynamics, increased deposition rates can be observed at the bottom of deep, narrow, anisotropically etched grooves. In this way, Runyan et al. [57] (and later Smeltzer) were able to completely fill 10- $\mu$ m-wide grooves (up to 100  $\mu$ m deep) epitaxially with negligible silicon growth over the rest of the wafer surface. The simultaneous addition of HCl gas during the growth process is required to obtain these unusual results. Since HCl gas is an isotropic silicon etchant at these temperatures, the silicon which is epitaxially grown on the outer surface is immediately etched away in the flowing gas stream. Silicon grown in the poorly mixed atmosshere of the grooves, however, etches at a much slower rate and a net growth occurs in the groove. Heavily doped, buried regions extending over tens of micrometers are easily imagined under these circumstances as indicated in Fig. 10(b). After refilling the grooves with heavily doped silicon, the surface has been lightly etched in HCl and a lightly doped layer grown over the entire wafer. These results could not be obtained by conventional diffusion techniques. One implementation of such structures which has already been demonstrated is in the area of high-power electronic devices [58], to be discussed below in more detail. Such a process could also be used in mechanical applications to bury highly doped regions which would be selectively etched away at a later stage to form buried channels within the silicon structure.

Finally, a limited amount of work has been done on epitaxial growth through  $SiO_2$  masks. Normally under these conditions, SCS will grow epitaxially on the bare, exposed crystal while polycrystalline silicon is deposited on the oxide. This mixed deposit has been used in audio-frequency distributed-filter, electronic circuits by Gerzberg and Meindl at Stanford [59]. At reduced temperatures, however, with HCl added to the H<sub>2</sub> and SiCl<sub>4</sub> in the gas stream no net deposits will occur on the SiO<sub>2</sub> while faceted, single-crystal, epitaxial pedestals will grow on the exposed regions since polysilicon is etched

by the HCl at a faster rate than the SCS [60]. Such epitaxial projections may find use in future three-dimensional micro-mechanical structures.

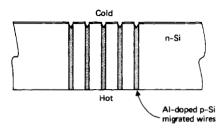

### Thermomigration

During 1976 and 1977, Anthony and Cline of GE laboratories performed a series of experiments on the migration of liquid eutectic Al/Si alloy droplets through SCS [61]-[67]. At sufficiently high temperatures, Al, for example, will form a molten alloy with the silicon. If the silicon slice is subjected to a temperature gradient (approximately 50°C/cm, or 2.0°C across a typical wafer) the molten alloy zone will migrate toward the hotter side of the wafer. The migration process is due to the dissolution of silicon atoms on the hot side of the molten zone, transport of the atoms across the zone, and their deposition on the cold side of the zone. As the Al/Si liquid region traverses the bulk, solid silicon in this way, some aluminum also deposits along with the silicon at the colder interface. Thermomigration hereby results in a p-doped trail extending through, for example, an n-type wafer. The thermomigration rate is typically 3  $\mu$ m/min at 1100°C. At that temperature, the normal diffusion rate of Al in silicon will cause a lateral spread of the p-doped region of only 3-5  $\mu$ m for a migration distance of 400  $\mu$ m (the full thickness of standard silicon wafers).

Exhaustive studies by Anthony and Cline have elucidated much of the physics involved in the thermomigration process including migration rate [62], p-n junction formation [64], stability of the melt [65], effect of dislocations and defects in the silicon bulk, droplet morphology, crystallographic orientation effects, stresses induced in the wafer as a result of thermomigration [67], as well as the practical aspects of accurately generating, maintaining, and characterizing the required thermal gradient across the wafer. In addition, they demonstrated lamellar devices fabricated with this concept from arrays of vertical junction solar cells, to high-voltage diodes, to negative-resistance structures. Long migrated columns were found to have smaller diameters in (100) oriented wafers, since the droplet attains a pyramidally tapered point whose sides are parallel to the (111) planes. Migrated lines with widths from 30 to 160  $\mu$ m were found to be most stable and uniform in traversing 280-µm-thick (100) wafers when the lines were aligned along the (110) directions. Larger regions tended to break up into smaller independent migrating droplets, while lines narrower than about 30  $\mu$ m were not uniform due to random-walk effects from the finite bulk dislocation density in the wafer. Straight-line deviations of the migrated path, as a result of random walk, could be minimized either by extremely low ( $\ll 100/cm^2$ ) or extremely high  $(>10^{7}/cm^{2})$  dislocation densities. On the other hand, the dislocation density in the recrystallized droplet trail is found to be essentially zero, not unexpected from the slow, even, liquid-phase epitaxy which occurs during droplet migration. Dopant density in the droplet trail corresponds approximately to the aluminum solid solubility in silicon at the migration temperature  $\sim 2 \times 10^{19}$  cm<sup>-3</sup>, which corresponds to  $\rho = 0.005$  $\Omega \cdot cm$ . The p-type trail from a 50-µm-diameter aluminum droplet migrated through a 300-µm-thick n-type wafer would. therefore, exhibit less than 8- $\Omega$  resistance from front to back and would be electrically well-isolated from other nearby trails due to the formation of alternating p-n junctions, as shown in Fig. 11.

Nine potential sources of stress (generated in the wafer from the migrated regions) have been calculated by Anthony and 429

Fig. 11. In some applications of silicon micromechanics, it is important to connect the circuitry on one side of a wafer to mechanical structures on the other side. Thermomigration of Al wires, discussed extensively by Anthony and Cline [61]-[67], allows low-resistance  $(<8 \Omega)$ , close-spaced (<100- $\mu$ m) wires to be migrated through thick (375- $\mu$ m) wafers at reasonable temperatures (~1100°C) with minimal diffusion (<2  $\mu$ m).

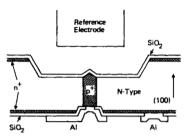

Fig. 12. Structure of the gate-controlled diode of Wen and Zemel [69]. Circuitry is on the bottom (protected) side of the wafer, while the sensor electrode is on the top. The p<sup>+</sup> feedthrough was accomplished by thermomigration of Al from the circuit side to the sensor side of the wafer. For ionic concentration measurements, an appropriate ion-sensitive membrane must be deposited over the oxide on the sensor side. Figure courtesy of C. C. Wen.

Cline. Maximum stresses intrinsic to the process (i.e., those which are present even when processing is performed properly) are estimated to be as high as  $1.39 \times 10^9$  dyne/cm<sup>2</sup>, which can be substantially reduced by a post-migration thermal anneal. Although the annealed stress will be about two orders of magnitude below the yield point of silicon at room temperature, it may increase the susceptibility of the wafer to fracture and should be minimized, especially if a large number of migrated regions are closely spaced.

One obvious utilization of thermomigration is the connection of circuitry on one side of a wafer to a mechanical function on the other side. Another application may be the dopantdependent etching of long narrow holes through silicon. Since the work of Anthony and Cline, the thermomigration process has been used to join silicon wafers [68] and to serve as feedthroughs for solid-state ionic concentration sensors (see Fig. 12) [69]. Use of thermomigrated regions in power devices is another potential application. Even more significantly, laser-driven thermomigration has been demonstrated by Kimerling *et al.* [70]. Such a process may be extremely important in practical implementations of these migration techniques, especially since the standard infrared or electron-beam heating methods used to induce migration are difficult to control uniformly over an entire wafer.

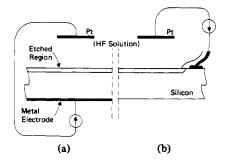

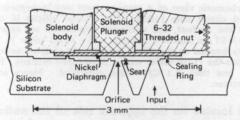

# Field-Assisted Thermal Bonding

The use of silicon chips in exposed, hostile, and potentially abrasive environments will often require mounting techniques substantially different from the various IC packaging methods now being utilized. First reported by Wallis and Pomerantz in 1969, field-assisted glass-metal thermal sealing [71] (sometimes called Mallory bonding after P. R. Mallory and Co., Inc., where Wallis and Pomerantz were then employed) seems to

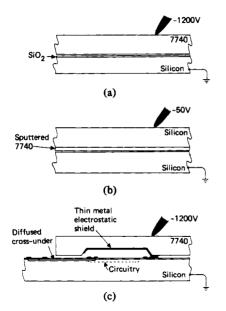

Fig. 13. Field-assisted thermal bonding can be used to hermetically bond (a) 7740 glass to silicon (bare or oxidized) or (b) silicon to silicon simply by heating the assembly to about 300°C and applying a voltage. Glass can be bonded to IC chips (c) if the circuitry is first protected by etching a shallow (~10- $\mu$ m) well in the glass and depositing a grounded metal shield inside the well [76].

fulfill many of the requirements for bonding and mounting micromechanical structures. The technique is simple, low temperature, high strength, reliable, and forms hermetic seals between metals and conventional alkali-silicate glasses [72]. It is also very similar to well-known high-temperature thermal bonds where the cohesive metal-oxides, which are generated during the heating process, readily mix with the viscous glass. In the case of silicon, a glass slide is placed over a polished wafer (bare or thermally oxidized), the assembly is heated to about 400°C, and a high voltage (~1200 V) is applied between the silicon and the metal contact to the other side of the glass. If the sample is not too large, the metal contact may be a simple point probe located near one corner as shown in Fig. 13(a). Since the negative electrode is applied to the glass, ionic conduction causes a drift of positive ions away from the glass/Si interface into the bulk of the glass. The depletion of positive ions at the interface results in a high electric field across the air gap between the two plates. Electrostatic forces here, estimated to be higher than 350 psi, effectively clamp the pieces locally, conforming the two surfaces to obtain the strong, uniform, hermetic seal characteristic of field-assisted thermal bonding. The bonding mechanism itself has been the subject of some controversy, as discussed recently by Brownlow [73]. His convincing series of deductions, however, suggest that the commonly observed initial current peak at the onset of bonding is actually dissipated in the newly formed, narrow space-charge region in the glass at the interface. This high energy-density pulse, in the early stages of bonding, was shown to be capable of increasing the interfacial temperature by as much as 560°C, more than enough to induce the familiar, purely thermal glass/metal seal. Brownlow shows how this model correlates well with several other features observed during the bonding process.

From a device viewpoint, it is important to recognize that the relative expansion coefficients of the silicon and glass should match as closely as possible to alleviate thermal stresses after the structure has cooled. This aspect of field-assisted bonding also has the obvious advantage of yielding integrated mechanical assemblies with very small mechanical drifts due to ambient temperature variations. Corning borosilicate glasses 7740 and 7070 have both been used successfully in this regard. In addition, Brooks *et al.* [74] have even bonded two silicon wafers by sputtering approximately 4  $\mu$ m of 7740 glass over one of the wafers and sealing the two as already described, with the negative electrode contacting the coated wafer as shown in Fig. 13(b). Since the glass is so thin, however, the sealing voltage was not required to be above 50 V.

A high degree of versatility makes this bonding technique useful in a wide variety of circumstances. It is not necessary to bond to bare wafers, for example; silicon passivated with thermal oxide as thick as 0.5  $\mu$ m is readily and reliably bonded at somewhat higher voltage levels. The bonding surface may even be partially interrupted with aluminized lines, as shown by Roylance and Angell [75], without sacrificing the integrity or hermeticity of the seal since the aluminum also bonds thermally to the glass. In addition, glass can be bonded to silicon wafers containing electronic circuitry using the configuration shown in Fig. 13(c) [76]. The circuitry is not affected if a well is etched in the glass and positioned over the circuit prior to bonding. A metal film deposited in the well is grounded to the silicon substrate during actual bonding and serves as an electrostatic shield protecting the circuit. Applications of all these aspects will be presented and expanded upon in the following sections.

# IV. GROOVES AND HOLES

Even simple holes and grooves etched in a silicon wafer can be designed and utilized to provide solutions in unique and varied applications. One usage of etched patterns in silicon with far-reaching implications, for example, is the generation of very high precision molds for microminiature structures. Familiar, pyramidal-shaped holes anisotropically etched in (100) silicon and more complex holes anisotropically etched in (110) silicon were used by Kiewit [77] to fabricate microtools such as scribes and chisels for ruling optical gratings. After etching the holes in silicon through an SiO<sub>2</sub> mask, the excess SiO<sub>2</sub> was removed and very thick layers of nickelphosphorus or nickel-boron allovs were deposited by electroless plating. When the silicon was completely etched away from the thick plated metal, miniature tools or arrays of tools were accurately reproduced in the metal with geometrically well-defined points having diameters as small as 50 nm. The resulting metal tools had a hardness comparable to that of file steel.

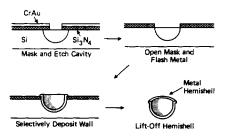

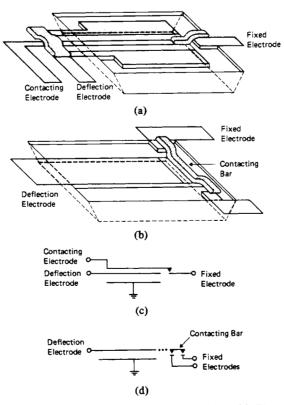

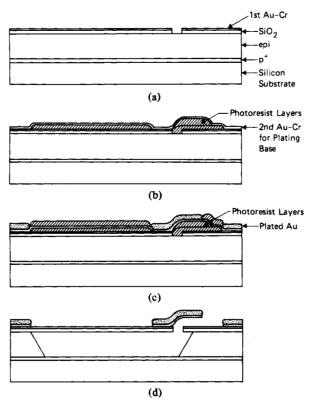

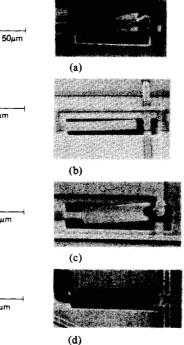

Similar principles were employed by Wise *et al.* [78] to fabricate miniature hemispherical structures for use as thermonuclear fusion targets. In these experiments, a large two-dimensional array of hemispherical holes was etched into a silicon wafer using an HNA isotropic solution, approximately as shown in Fig. 4(c). After removing the  $SiO_2/Cr/Au$  etch mask, polymer, glass, metal, or other thin films are deposited over the wafer, thereby conforming to the etched hemispherical shapes. When two such wafers are aligned and bonded, the silicon mold can be removed (either destructively by etching or nondestructively by using a low adhesion coating between the silicon and the deposited film). The resulting molded shape is a thin-walled spherical shell made from the deposited material. Fig. 14 is the process schedule for a simple metal hemishell demonstrated by Wise *et al*.

The potential of making arrays of sharp points in silicon itself by etching was employed in a novel context by Thomas and Nathanson [79], [80]. They defined a very fine grid

Fig. 14. Fabrication sequence for free-standing metal hemishells using an isotropic silicon-etching technique [78]. Typical dimensions of the hemishell are 350- $\mu$ m diameter with a 4- $\mu$ m-thick wall. Courtesy of K. D. Wise.

(typically 25  $\mu$ m center to center) in an SiO<sub>2</sub> mask, then isotropically etched the silicon exposed in the grid lines with an HNA mixture. The isotropic etch undercuts each square segment of the oxide grid uniformly around its periphery. If the etching is quenched just after the oxide segments are completely undercut and fall from the surface, a large array of very sharply tipped silicon points is obtained. Point diameters were estimated to be about 20 nm. These silicon points, at densities up to  $1.5 \times 10^5$  cm<sup>2</sup>, were used by Thomas and Nathanson as efficient, uniform, photosensitive field emitter arrays which were imaged onto a phosphor screen closely spaced to the wafer. A more complex extension of this fabrication technique will be described below in the section on Thin Cantilever Beams.

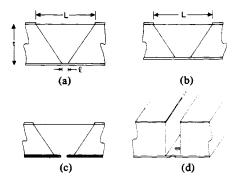

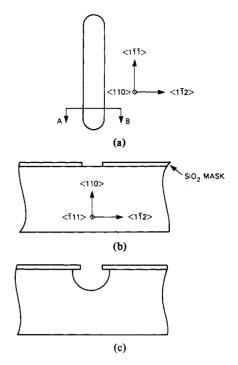

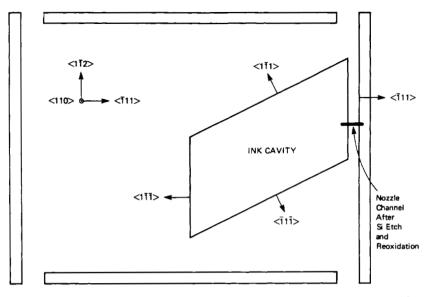

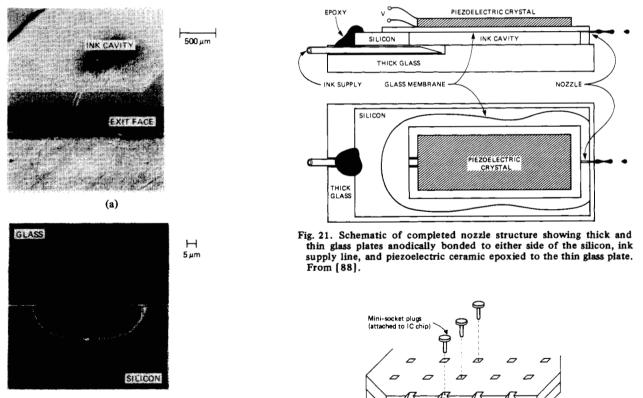

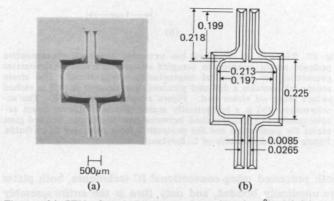

#### Ink Jet Nozzles

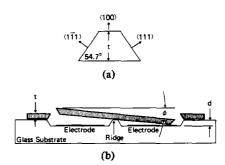

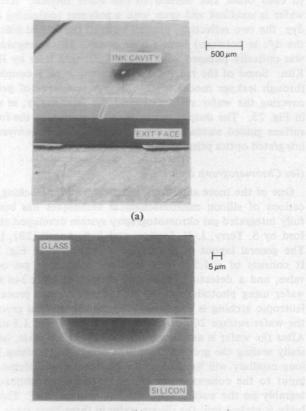

Since anisotropic etching offers a powerful method for controlling undercutting of masks during silicon etching, these techniques are important candidates for etching high-resolution holes clear through wafers as Bassous et al. [5], [43], [81], [82] first realized and pursued extensively; see Fig. 15. Patterns etched clear through wafers have many potential applications, as will be seen below, but one of the simplest and most commercially attractive is in the area of ink jet printing technology [83], [86]. As shown in Fig. 16(a), the geometry of the pyramidal hole in (100) silicon can be adjusted to completely penetrate the wafer, the square hole on the bottom of the wafer forming the orifice for an ink jet stream. The size of the orifice (typically about 20  $\mu$ m) depends on the wafer thickness t and mask dimension L according to  $l = L - (2t/\tan \theta)$ . where  $\theta = 54.74^{\circ}$  is the angle between the (100) and (111) planes. In practice, the dimension l is very difficult to control accurately because 1) wafer thickness t is not easy to control accurately and 2) small angular misalignments of a square mask will result in an effective L which is larger than the mask dimension [43], thereby enlarging l as shown in Fig. 16(b). The angular misalignment error can be eased by using a round mask (diameter L) which will give a square hole  $L \times L$  independent of orientation, as described in Section III (and Fig. 5(e)) by the general rule of anisotropic undercutting.

Membrane structures have also been used in ink jet nozzle designs not only to eliminate the effects of wafer thickness variations, but also to permit more densely packed orifices as well as orifice shapes other than square. In one technique described by Bassous *et al.* [35], the wafer surface is highly doped with boron everywhere but the desired orifice locations. Next, the wafer is anisotropically etched clear through with EDP as described above, using a mask which produces an *l* which is 3 to 5 times larger than the actual orifice. Since EDP does not attack silicon which is highly doped with boron, a p<sup>+</sup> silicon membrane will be produced, suspended across the bot-

Fig. 15. (a) Cross section and (b) top view of anisotropically etched silicon ink jet nozzle in a (100) wafer developed by E. Bassous *et al.* [5], [43], [8].

Fig. 16. A number of different methods have been developed for fabricating silicon ink jet nozzles. (a) and (b) show the errors in final nozzle size which occurs when the wafer thickness varies. (c) shows a  $p^+$  membrane structure. This design yields round nozzles and also minimizes the effects of wafer thickness variations. Nozzles can be more closely spaced by using the  $p^+$  membrane technique on a (110) wafer, as shown in (d) [35].

tom of the pit with an orifice in the center corresponding to the location previously left undoped; see Fig. 16(c). The use of a membrane can also be extended to decrease the minimum allowed orifice spacing. Center-to-center orifice spacing is limited to about 1.5 times the wafer thickness when the simple square geometries of Figs. 15, 16(a)-(c) are employed, but can be much closer using membranes. Orifice spacings in *two* dimensions can be made very small by using (110) oriented wafers and etching vertical-walled *grooves* (as described in Section III) clear through the wafer, aligned to rows of orifices on the other side fabricated by this membrane technique. The result, shown in Fig. 16(d), is a number of closely spaced rows containing arbitrarily spaced holes in a long, narrow rectangular p<sup>+</sup> membrane [35].

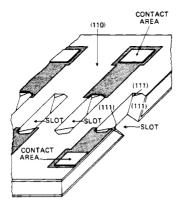

Deep grooves or slots etched clear through (110) silicon have been used by Kuhn *et al.* [87] in another important ink jet application. At a characteristic distance from the ink jet orifice, the ink stream, which is ejected under high pressure, begins to break up into well-defined droplets at rates of about  $10^5$ drops per second as a result of a small superimposed sinusoidal pressure disturbance. A charge can be induced on individual droplets as they separate from the stream at this point by passing the jet through a charging electrode. Once charged, the drops can be electrostatically deflected (like an electron beam) to strike the paper at the desired locations. Kuhn *et al.* etched

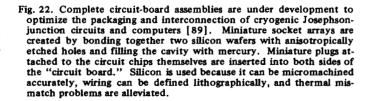

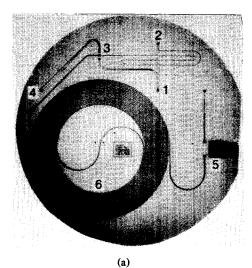

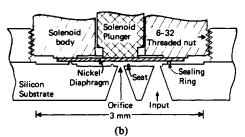

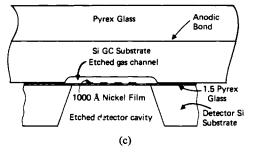

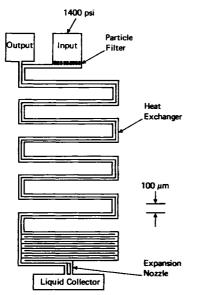

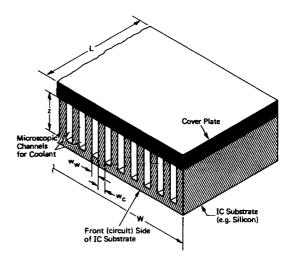

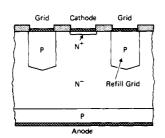

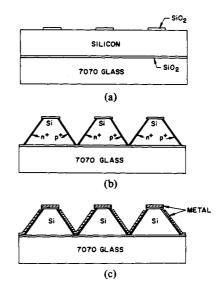

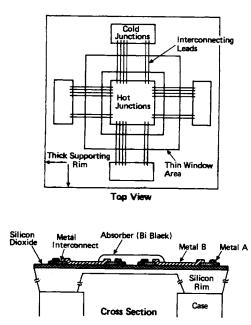

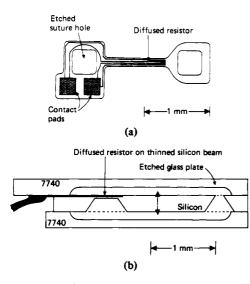

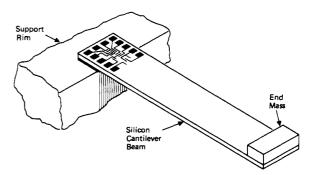

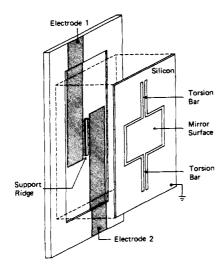

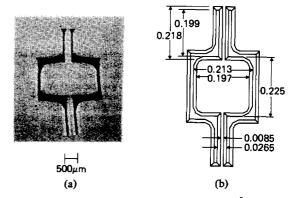

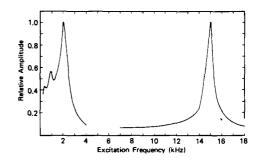

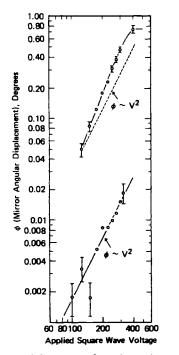

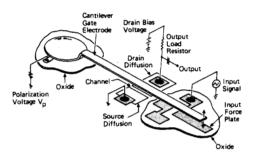

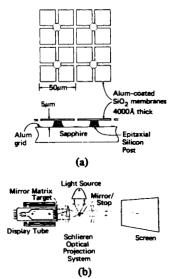

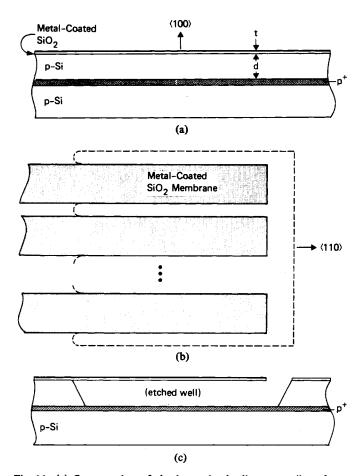

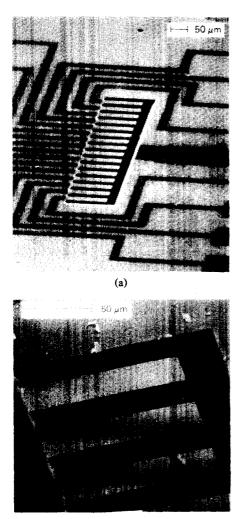

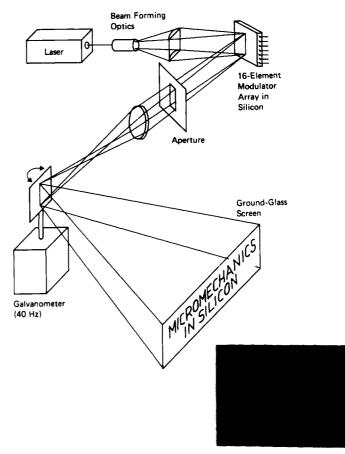

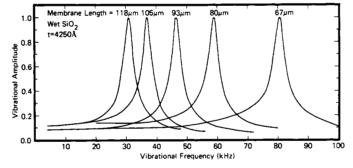

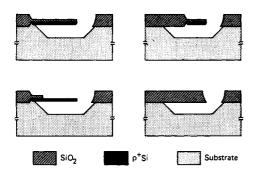

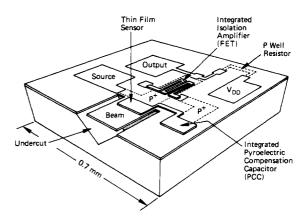

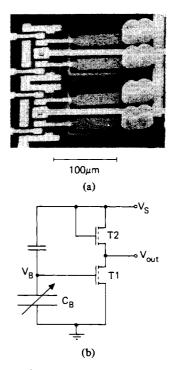

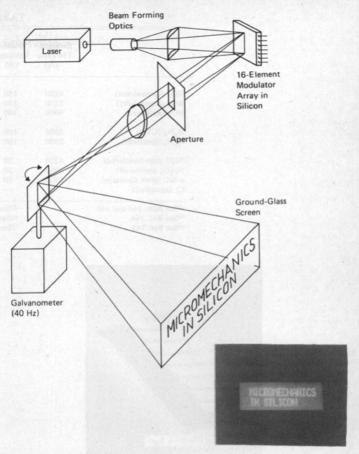

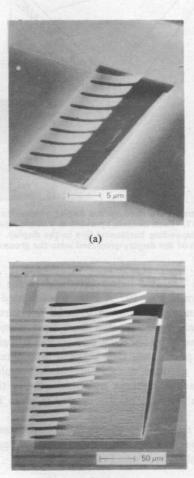

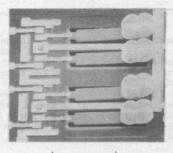

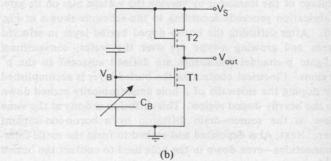

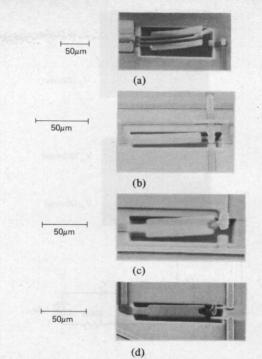

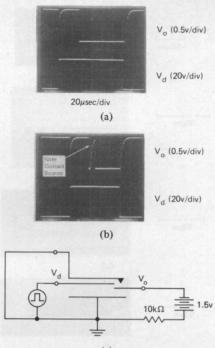

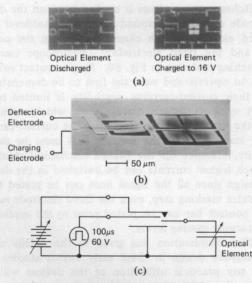

Fig. 17. Grooves anisotropically etched clear through a (110) wafer were employed as charge electrode arrays by Kuhn et al. [87] in an ink jet printing demonstration. A charge can be induced on individual ink droplets as they pass through the grooves by applying a voltage to the walls of the groove. Subsequently, drops are "steered" to the paper after traveling through a high electric field. Figure courtesy of L. Kuhn.