# Ch 3. Working with Combinational Logic

## Working with combinational logic - Introduction

- Two-Level Simplification

- Automating Two-Level Simplification

- Multilevel Logic Networks

- Time Response in Combinational Networks

- Hardware Description Languages

#### **Two-Level Simplification**

#### Design Examples

- Two-bit comparator

- Two-bit binary adder

- BCD increment-by-1 function

- Formalizing the Process of Boolean Minimization

- Algorithm for two-level simplification

- Application of the step-by-step algorithm

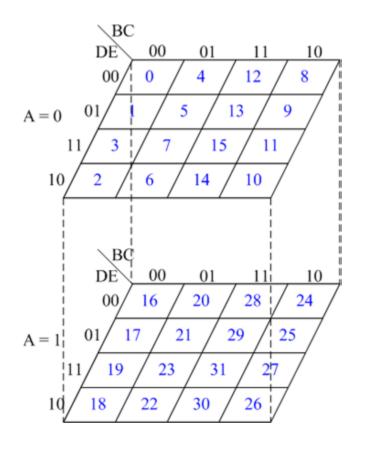

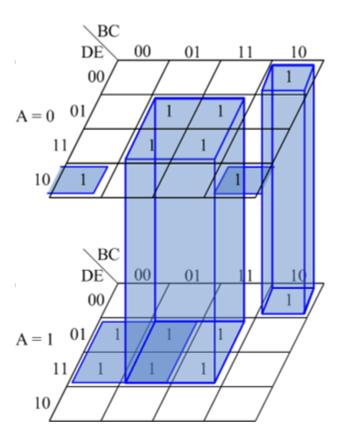

- K-Maps Revisited : Five- and Six-Variable Functions

Five-variable K-maps

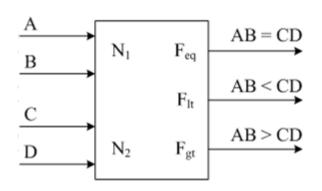

#### Design Examples – Two-bit comparator

The behavior of two-bit comparator

<Block diagram>

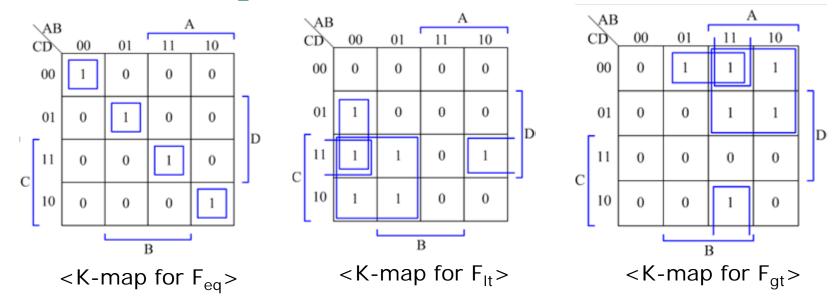

We need 4-variable K-maps for each of 3 output functions

#### <Truth table>

| Α | В | С | D | Feq | $\mathbf{F}_{lt}$ | Fgt |

|---|---|---|---|-----|-------------------|-----|

| 0 | 0 | 0 | 0 | 1   | 0                 | 0   |

|   |   | 0 | 1 | 0   | 1                 | 0   |

|   |   | 1 | 0 | 0   | 1                 | 0   |

|   |   | 1 | 1 | 0   | 1                 | 0   |

| 0 | 1 | 0 | 0 | 0   | 0                 | 1   |

|   |   | 0 | 1 | 1   | 0                 | 0   |

|   |   | 1 | 0 | 0   | 1                 | 0   |

|   |   | 1 | 1 | 0   | 1                 | 0   |

| 1 | 0 | 0 | 0 | 0   | 0                 | 1   |

|   |   | 0 | 1 | 0   | 0                 | 1   |

|   |   | 1 | 0 | 1   | 0                 | 0   |

|   |   | 1 | 1 | 0   | 1                 | 0   |

| 1 | 1 | 0 | 0 | 0   | 0                 | 1   |

|   |   | 0 | 1 | 0   | 0                 | 1   |

|   |   | 1 | 0 | 0   | 0                 | 1   |

|   |   | 1 | 1 | 1   | 0                 | 0   |

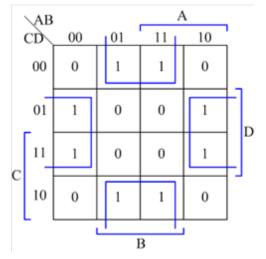

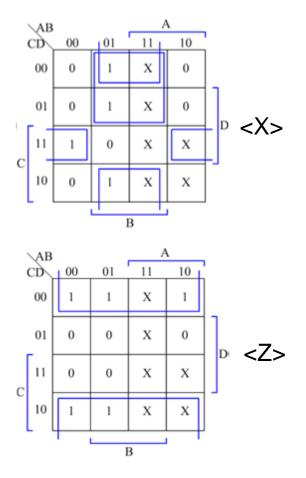

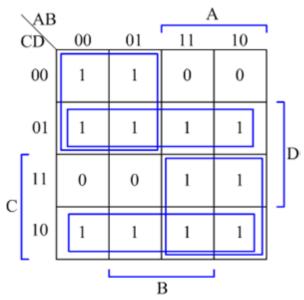

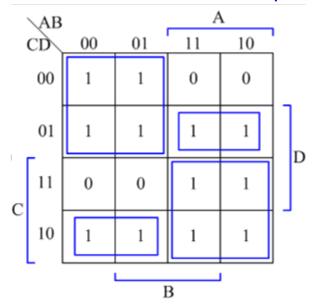

## Design Examples – Two-bit comparator (cont'd)

$F_{eq} = A'B'C'D' + A'BC'D + AB'CD' + ABCD$ = A'C' (B'D' + BD) + AC (B'D' + BD)= (A'C' + AC) (B'D' + BD) $= (A \bigoplus C)' (B \bigoplus D)'$  $= (A \equiv C) (B \equiv D)$

$\begin{array}{ll} \mathsf{F}_{\mathsf{lt}} &= \mathsf{A'B'D} + \mathsf{B'CD} + \mathsf{A'C} \\ \mathsf{F}_{\mathsf{gt}} &= \mathsf{AC'} + \mathsf{ABD'} + \mathsf{BC'D'} \end{array}$

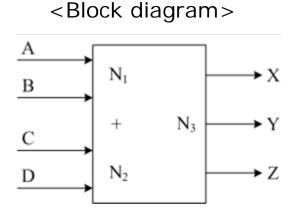

The behavior of two-bit binary adder

X represents

the most significant bit.

#### <Truth table>

| Α | В | С | D | Х | Y | Ζ |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|   |   | 0 | 1 | 0 | 0 | 1 |

|   |   | 1 | 0 | 0 | 1 | 0 |

|   |   | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 |

|   |   | 0 | 1 | 0 | 1 | 0 |

|   |   | 1 | 0 | 0 | 1 | 1 |

|   |   | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 |

|   |   | 0 | 1 | 0 | 1 | 1 |

|   |   | 1 | 0 | 1 | 0 | 0 |

|   |   | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 |

|   |   | 0 | 1 | 1 | 0 | 0 |

|   |   | 1 | 0 | 1 | 0 | 1 |

|   |   | 1 | 1 | 1 | 1 | 0 |

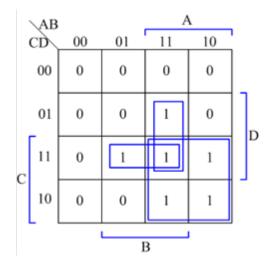

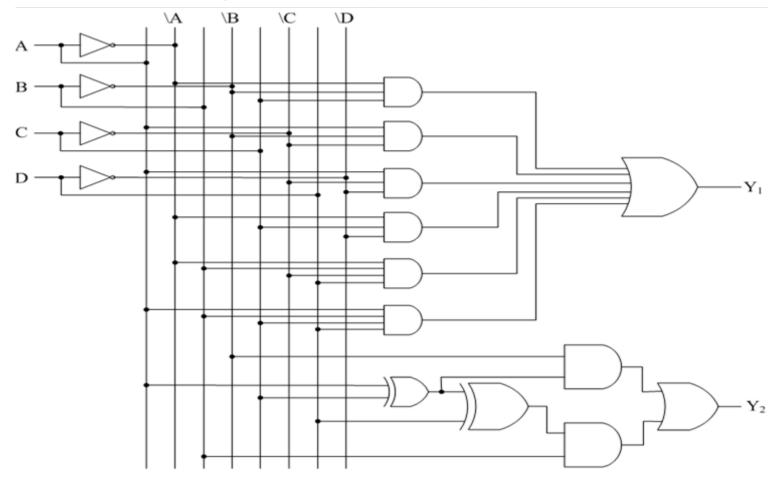

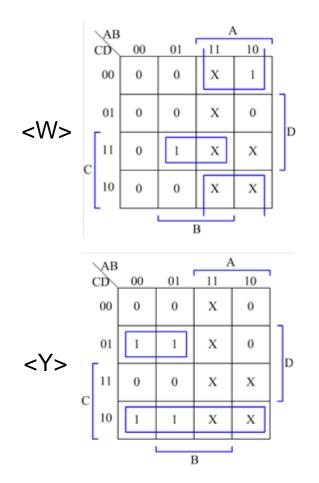

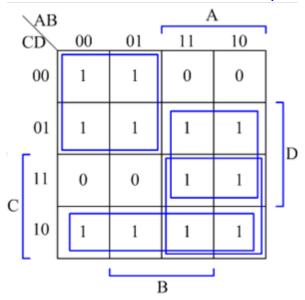

#### Design Examples – Two-bit binary adder (cont'd)

two 2-element groups (three literals), one 4-element group (two literals) :

X = AC + BCD + ABD

two 4-element groups (two literals) :  $Z = BD' + B'D = B \oplus D$

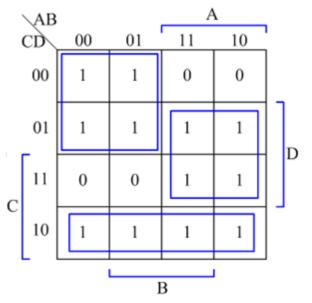

#### Design Examples – Two-bit binary adder (cont'd)

two 2-element groups (three literals) : A'B'C , AB'C'

four single-element groups (four literals) : A'BC'D, A'BCD', ABC'D', ABCD

Factoring

$A'B'C + AB'C' = B'(A'C + AC') = B'(A \oplus C)$   $A'BC'D + A'BCD' = A'B(C \oplus D) \qquad ABC'D' + ABCD = AB(C \oplus D)'$  $A'B(C \oplus D) + AB(C \oplus D)' = B(A \oplus C \oplus D)$

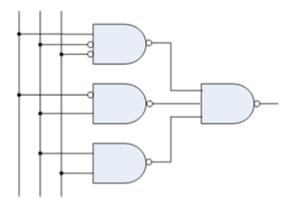

$Y = B' (A \oplus C) + B (A \oplus C \oplus D) \longrightarrow 5 \text{ gates}, 7 \text{ literals}$

If only AND, OR, and NOT gates are allowed :

Y = A'B'C + AB'C' + AC'D' + A'CD' + A'BC'D + ABCD → 7 gates, 20 literals

## Design Examples – Two-bit binary adder (cont'd)

<Two alternative implementations of Y>

III - Working with Combinational Logic

Contemporary Logic Design

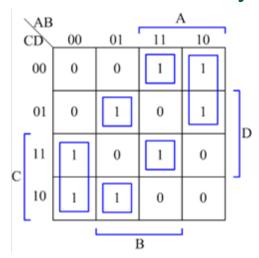

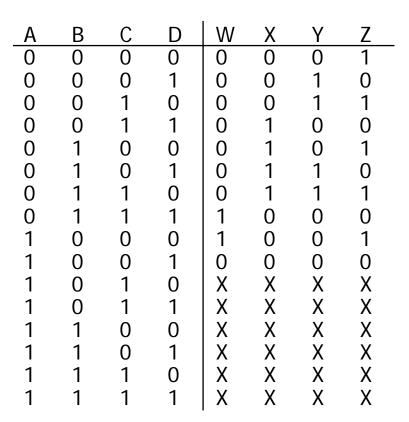

## Design Examples – BCD increment-by-1 function

#### • Truth table $\rightarrow$ Fig. 2.32

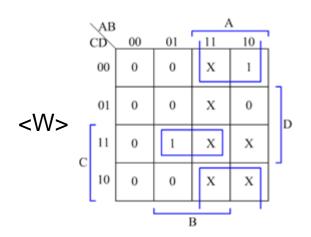

W = BCD + AD'

## Design Examples – BCD increment-by-1 function

$$W = BCD + AD'$$

$$X = BD' + BC' + B'CD$$

$$Y = A'C'D + CD'$$

$$Z = D'$$

## Formalizing the Process of Boolean Minimization

#### Definition of Terms

- Implicant

- A single element of the on-set or any group of elements that can be combined together in a K-map

- Prime implicant

- An implicant that cannot be combined with another one to eliminate a literal

- Essential prime implicant

- A prime implicant that alone covers an element of on-sets

- must be part of the minimized expression as they are needed for any and all covers

#### Objective

- Grow implicant into prime implicants (minimize literals per term)

- Cover the ON-set with as few prime implicants as possible

#### III - Workin(minimize number of product terms)

Combinational Logic

Contemporary Logic Design

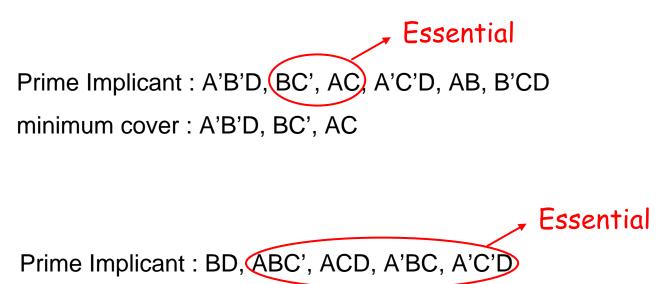

#### Illustrating the Definitions

minimum cover : ABC', ACD, A'BC, A'C'D

Redundant Prime Implicant : BD,(CD) AC, B'C minimum cover : BD, AC, B'C

#### Two-level Simplification Algorithm

- A procedure for finding a minimum sum-of products expression from a K-map

- □ Step 1 : Choose an element from the on-set

- Step 2 : Find all of the "Maximal" groups of 1s and Xs adjacent to that element (This forms prime implicants)

- Repeat Steps 1, 2 until all prime implicants have been found

- Step 3 : Visit an element of the on-set

- To find essential prime implicants

- Repeat Step 3 until all essential prime implicants have been found

- □ Step 4 : If there remain 1s uncovered by essential primes,

- Select a minimum number of prime implicants that cover them

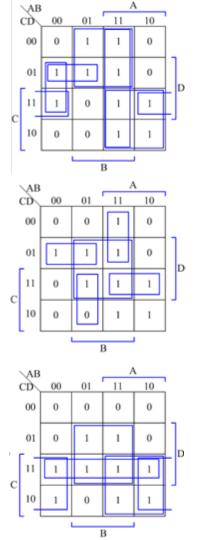

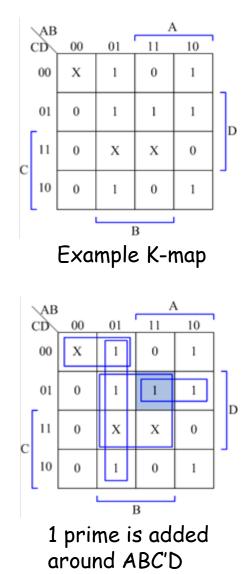

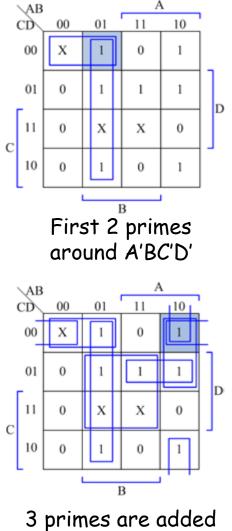

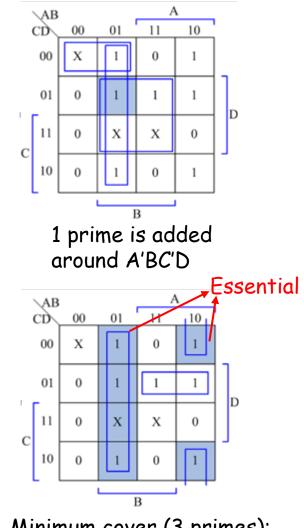

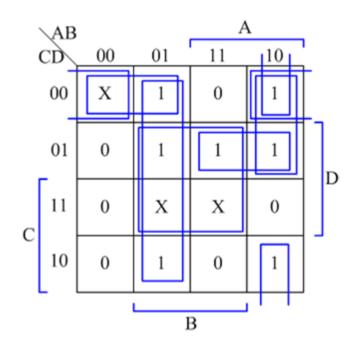

## Application of the Step-by-step Algorithm

III - Working with Combinational Logic

3 primes are added around AB'C'D'

Minimum cover (3 primes): A'B, AB'D', AC'D

## K-maps Revisited : Five-Variable Function Example

$F(A,B,C,D,E) = \sum m(2,5,7,8,10,13,15,17,19,21,23,24,29,31)$

#### Automating Two-Level Simplification

- Quine-McCluskey Method

- Finding prime implicants

- Finding the minimum cover

- Espresso Method

- Algorithm used in *Espresso*

- Example

- Realizing S-o-P and P-o-S Logic Networks

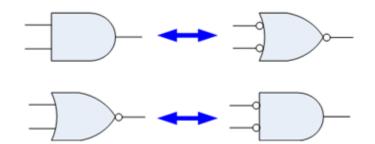

- DeMorgan's law and pushing bubbles

- Four conversion examples

## Quine-McCluskey Method Finding Prime Implicants

• Example Function :  $F = \sum m(4,5,6,8,9,10,13) + d(0,7,15)$

| Column / | Column // | Column III |

|----------|-----------|------------|

| 0000 🗸   | 0-00 *    | 01 *       |

|          | -000 *    |            |

| 0100 🗸   |           | -1-1 *     |

| 1000 🗸   | 010- 🗸    |            |

|          | 01-0 🗸    |            |

| 0101 🗸   | 100- *    |            |

| 0110 🗸   | 10-0 *    |            |

| 1001 🗸   |           |            |

| 1010 🗸   | 01-1 🗸    |            |

|          | -101 🗸    |            |

| 0111 🗸   | 011- 🗸    |            |

| 1101 🗸   | 1-01 *    |            |

| 1111 🗸   | -111 🗸    |            |

|          | 11-1 🗸    |            |

√ implicant

\* prime implicant

III - Working with Combinational Logic

the number of 1s Step 2 : Apply the Uniting theorem – Compare the elements in the 1<sup>st</sup> group against each element in the 2<sup>nd</sup> e.g. 0000 vs. 0100 yields 0-00 0000 vs. 1000 yields -000 When used in a combination, mark with a check (Implicant) If cannot be combined, mark with a star (Prime implicant) Repeat until no further combinations can be made

Stage 1 : Find all prime implicants

Step 1 : Fill Column 1 with ON-set and

DC-set minterm indices, grouped by

## Quine-McCluskey Method Finding Prime Implicants (cont'd)

Prime implicants found by the Quine-McCluskey method :

- 0-00 = A'C'D' -000 = B'C'D'

- 100- = AB'C' 10-0 = AB'D'

- 1-01 = AC'D 01-- = A'B

-1-1 = BD

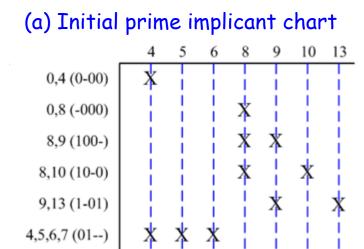

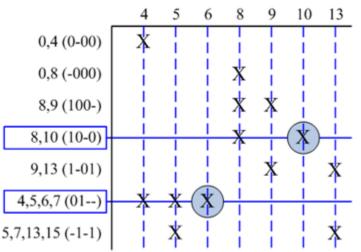

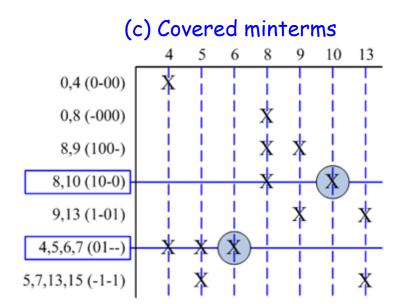

## Quine-McCluskey Method Finding the Minimum Cover

Stage 2 : Find the minimum cover – find the smallest collection of prime implicants that cover the complete on-set of the function through the prime implicant chart

rows = prime implicants,

cols = ON-set elements

If an ON-set element is covered by the prime implicant, place a "X."

III - Working with Combinational Logic

5,7,13,15 (-1-1)

(b) Essential prime implicants

If column has a single X, the implicant associated with the row is essential.

And it must be in the minimum cover.

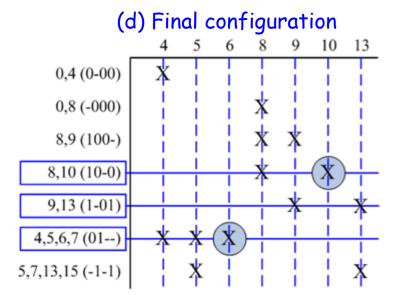

## Quine-McCluskey Method Finding the Minimum Cover (cont'd)

Eliminate all columns covered by essential primes.

Eliminate all rows covered by a set of essential primes.

Find minimum set of rows that cover the remaining columns.

$$F = AB'D' + AC'D + A'B$$

## *Espresso* Method Algorithm Used in *Espresso*

- 1. EXPAND : Expand implicants to their maximum size

- Implicants covered by an expanded implicant are removed from further consideration

- Quality of results depends on the order and direction of implicant expansion

- 2. IRREDUNDANT COVER

- An irredundant cover is extracted from the expanded implicants

- 3. REDUCE : Reduce prime implicants to the smallest size that still cover ON-set

- 4. Repeat sequence REDUCE/ EXPAND/ IRREDUNDANT COVER

- Continue repeating these steps as long as generated cover improves on the last solution

## *Espresso* Method Example

#### (a) Initial prime implicant

Initial set of primes after executing step 1 and 2 for the first time

4 primes, irredundant cover, but not the minimum cover

#### (b) Result of REDUCE step

The result of the REDUCE step : C'D and CD' are reduced (therefore, they are no longer primes)

#### *Espresso* Method Example (cont'd)

#### (c) Result of EXPAND step

The result of the second iteration of EXPAND

*Espresso* guarantees that it never generates the same cover twice

#### (d) Result of IRREDUNDANT COVER step

The extracted IRREDUNDANT COVER result

## Only 3 prime implicants : an improvement on the original result

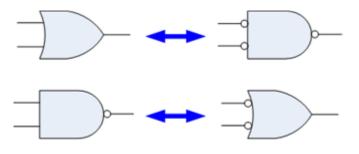

#### Realizing S-o-P and P-o-S Logic Networks

DeMorgan's Law and Pushing Bubbles

(AB)' = (A' + B') AB = (A' + B')'

(A + B)' = (A'B') A + B = (A'B')'

< OR/NAND equivalence >

| A | Ā | В | $\overline{B}$ | A + B | $\overline{A} \cdot \overline{B}$ | $\overline{A} + \overline{B}$ | $\overline{A \bullet B}$ |

|---|---|---|----------------|-------|-----------------------------------|-------------------------------|--------------------------|

| 0 | 1 | 0 | 1              | 0     | 0                                 | 1                             | 1                        |

| 0 | 1 | 1 | 0              | 1     | 1                                 | 1                             | 1                        |

| 1 | 0 | 0 | 1              | 1     | 1                                 | 1                             | 1                        |

| 1 | 0 | 1 | 0              | 1     | 1                                 | 0                             | 0                        |

#### < AND/NOR equivalence >

| A | $\overline{A}$ | В | $\overline{B}$ | $A \bullet B$ | $\overline{\overline{A}+\overline{B}}$ | $\overline{A} \bullet \overline{B}$ | $\overline{A+B}$ |

|---|----------------|---|----------------|---------------|----------------------------------------|-------------------------------------|------------------|

| 0 | 1              | 0 | 1              | 0             | 0                                      | 1                                   | 1                |

| 0 | 1              | 1 | 0              | 0             | 0                                      | 0                                   | 0                |

| 1 | 0              | 0 | 1              | 0             | 0                                      | 0                                   | 0                |

| 1 | 0              | 1 | 0              | 1             | 1                                      | 0                                   | 0                |

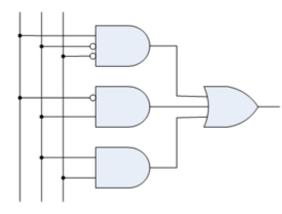

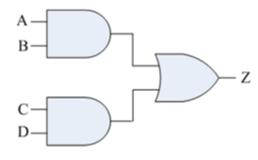

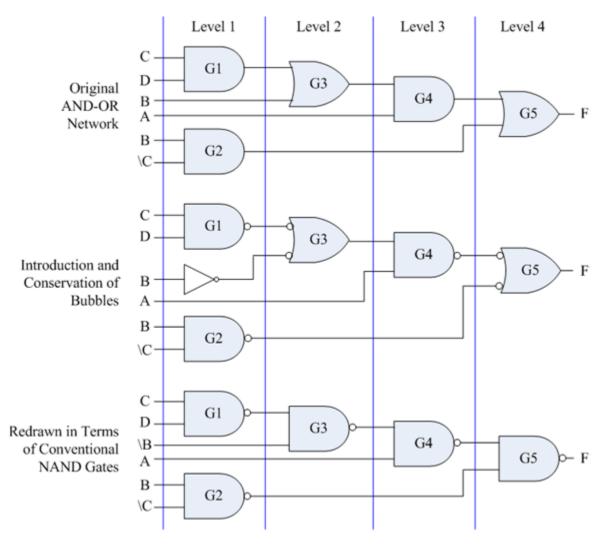

## AND/OR Conversion to NAND/NAND Networks

Initial AND/OR network

Conversion at the  $1^{\mbox{\scriptsize st}}$  level

1<sup>st</sup>-level AND gates are converted to their NAND equivalents

And complement the inputs to OR gates to conserve the circuits logic function Conversion at the 2<sup>nd</sup> level

2<sup>nd</sup> level OR gate with complemented inputs is replaced by NAND gate

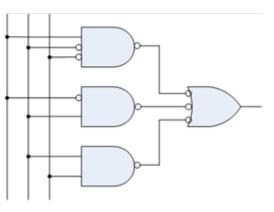

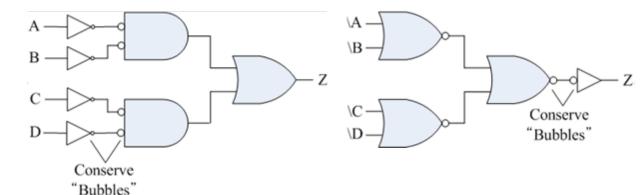

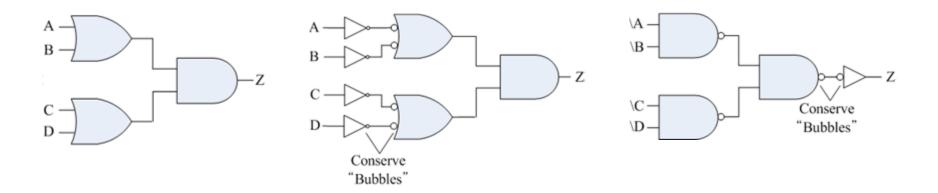

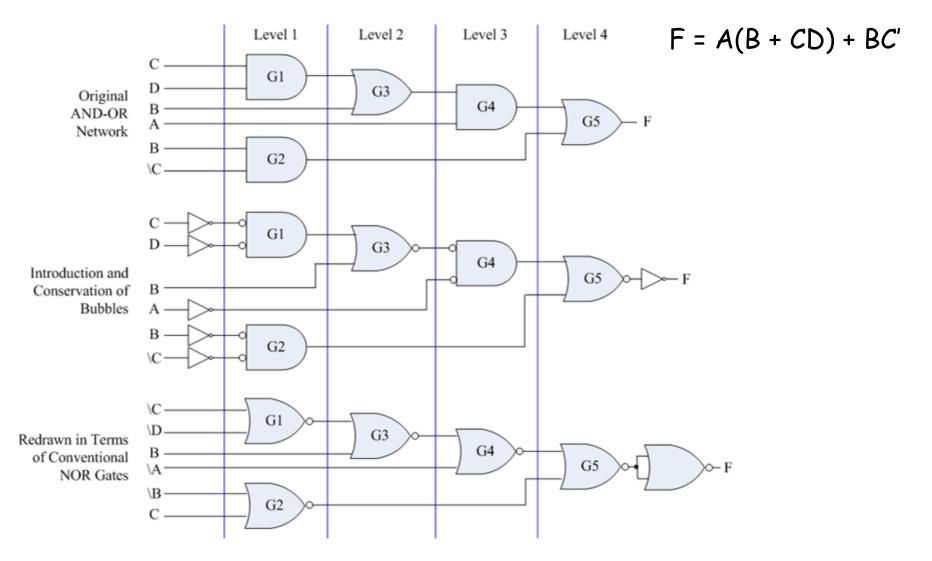

## AND/OR Conversion to NOR/NOR Networks

Initial AND/OR network

Complemented inputs are created at the two AND gates Two AND gates with complemented inputs are replaced by NOR gates

2<sup>nd</sup> level OR gate is converted to NOR gate after introducing a matching inverter

"Conserving Bubbles" :

When a new inversion is introduced, it must be balanced by a complementary inversion

## OR/AND Conversion to NOR/NOR Networks

#### Similar with "AND/OR Conversion to NAND/NAND Networks"

## OR/AND Conversion to NAND/NAND Networks

Similar with "AND/OR Conversion to NOR/NOR Networks"

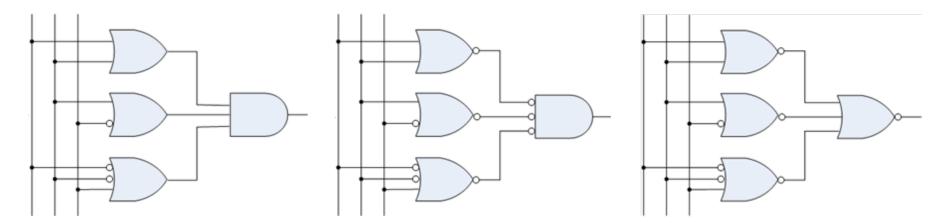

## Multilevel Logic Networks – Multilevel Conversion to NAND Gates

F = A(B + CD) + BC'

#### Multilevel Conversion to NOR Gates

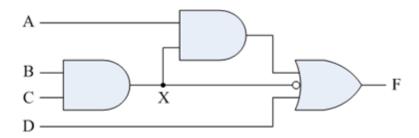

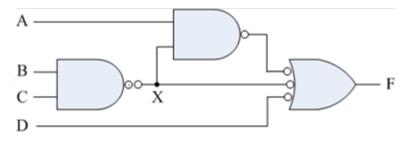

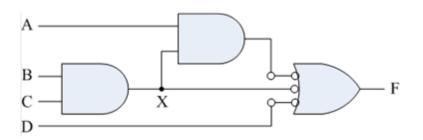

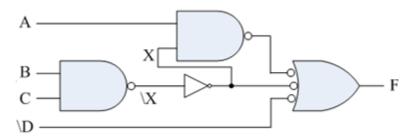

#### Non-Alternating NAND/NOR Multilevel Networks F = AX + X' + DX = BC

(a) Original Circuits

(c) Add Double Bubbles to Invert Output of AND Gate

(b) Add Double Bubbles to Invert All Inputs of OR Gate

(d) Insert Inverters to Eliminate Double Bubbles on a Wire

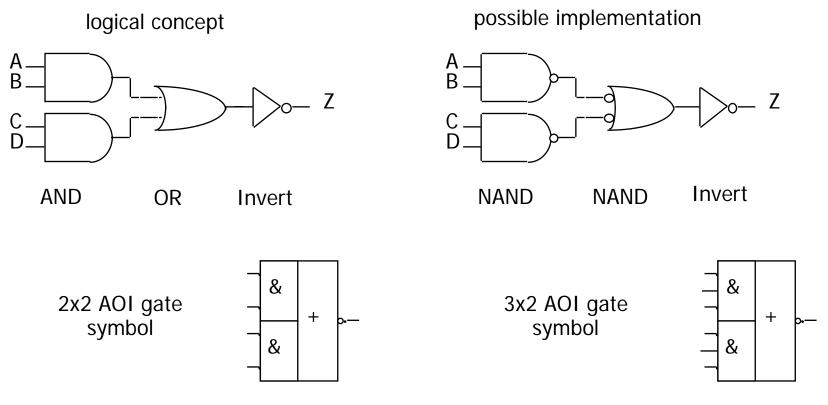

#### AND-OR-Invert Gates

AOI function: three stages of logic — AND, OR, Invert

multiple gates "packaged" as a single circuit block

#### Conversion to AOI Forms

General procedure to place in AOI form

- compute the complement of the function in sum-of-products form by grouping the 0s in the Karnaugh map

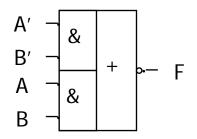

- Example: XOR implementation

- $\Box A \text{ xor } B = A' B + A B'$

- AOI form:

#### Examples of Using AOI Gates

Example:

- $\Box F = AB + AC' + BC'$

- $\Box$  F = (A' B' + A' C + B' C)'

- Implemented by 2-input 3-stack AOI gate

□ F = (A + B) (A + C') (B + C')

$$\Box F = [(A' + B') (A' + C) (B' + C)]'$$

- Implemented by 2-input 3-stack OAI gate

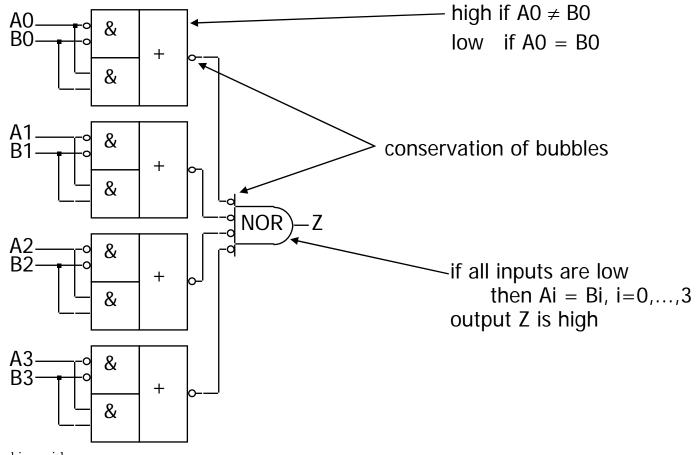

- Example: 4-bit equality function

- $\Box Z = (A0 B0 + A0' B0')(A1 B1 + A1' B1')(A2 B2 + A2' B2')(A3 B3 + A3' B3')$

each implemented in a single 2x2 AOI gate

#### Examples of Using AOI Gates (cont'd)

Example: AOI implementation of 4-bit equality function

#### Time Response in Combinational Networks

Time response tells us about a circuit's dynamic behavior

- Transient output changes: glitches

- Logical error caused by glitches: a hazard

- It is important to visualize the behavior of a circuit as a function of time

- Simulation tools can offer the time-based behavior of circuits

#### Gate Delays

- Defined in terms of minimum (best case), typical (average), and maximum (worst case) times.

- Worst-case delay should always be considered

- There are trade-offs between delay and power

#### Time Response in Combinational Networks

Example

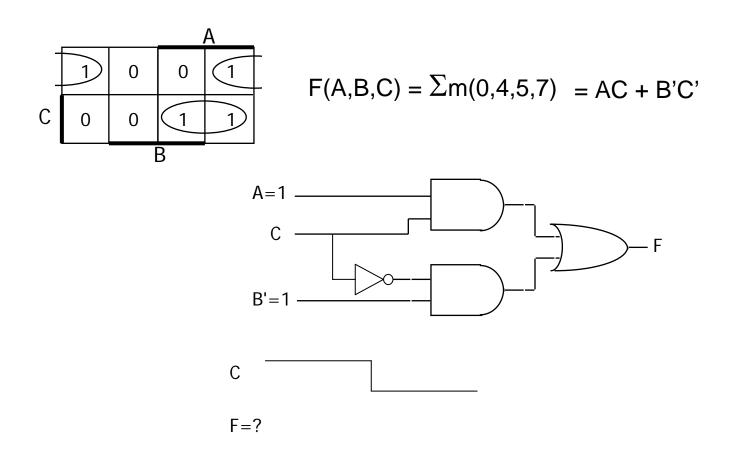

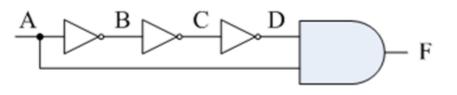

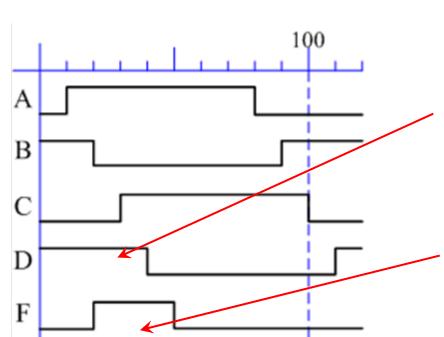

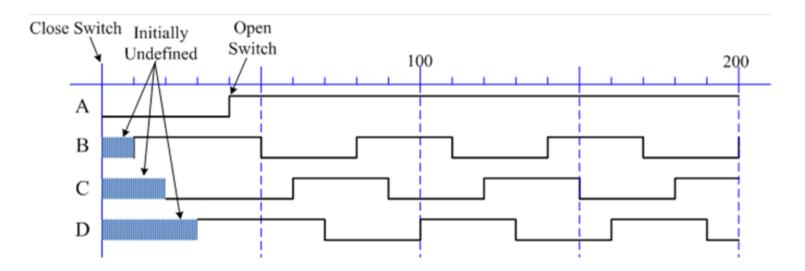

#### Timing Waveforms

- A pulse shaper

- At a glance, A A' = 0

- Delays matter

D remains high for three gate delays after A changes from low to high

F is not always '0'

the pulse is exactly three inverter-delays wide

#### Analysis of a Pulse-Shaper Circuit

#### Another Pulse-Shaper example

#### Hardware Description Languages

#### Describe behavior

- describe what module does, not how

- synthesis generates circuit for module

- Describe structure

- textual replacement for schematic

- hierarchical composition of modules from primitives

- Describe timing

- describe delay

- Describe concurrency

- Describe hardware at varying levels of abstraction

- Enable simulation

- event-driven simulation

#### HDLs

- ABEL (circa 1983) developed by Data-I/O

- targeted to programmable logic devices

- not good for much more than state machines

- ISP (circa 1977) research project at CMU

- simulation, but no synthesis

- Verilog (circa 1985) developed by Gateway (absorbed by Cadence)

- similar to C

- fairly efficient and easy to write

- IEEE standard

- VHDL (circa 1987) DoD sponsored standard

- similar to Ada (emphasis on re-use and maintainability)

- very general but verbose

- IEEE standard

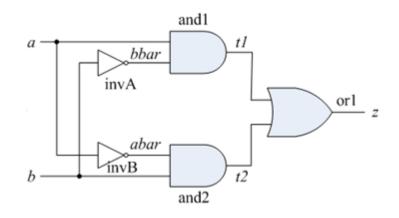

#### Describing Structure

XOR gate :

five gates and connecting wires

```

module xor_gate (a, b, z);

input a, b;

output z;

wire abar, bbar, t1, t2;

Inverter invA (abar, a);

inverter invB (bbar, b);

and_gate and1 (t1, a, bbar);

and_gate and2 (t2, b, abar);

or_gate or1 (z, t1, t2);

Each gate is an instance

of another module

```

#### endmodule

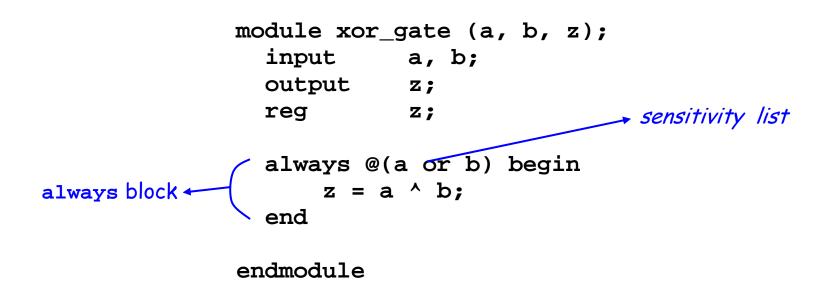

#### Describing Behavior

- always block: specifies when and how the module behave

- sensitivity list: specifies when the block is executed (triggered by which signals)

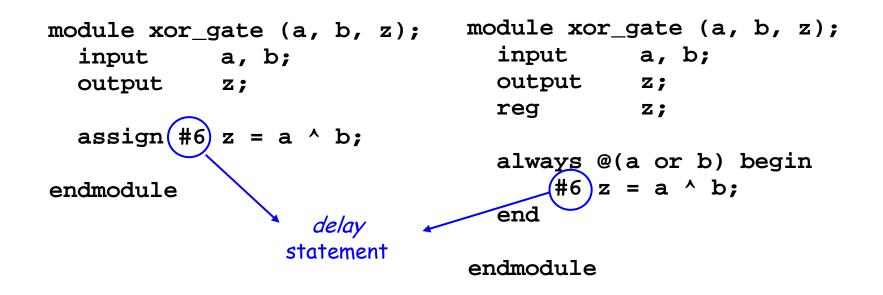

#### Delay

- The *delay* statement postpones the assignment of a new value to output

- delay statements only make sense within a behavioral description

#### **Event-Driven Simulation**

module test-bench (x, y); module both\_together (z); output output x, y; Z; wire w1, w2; req x, y; test-bench tb1(w1, w2); initial begin x = 0; y = 0;xor gate xor1(w1, w2, z); #10; x = 0; y = 1;always @(z) begin #10; \$display("At time: %d with x = 1; y = 0;inputs:%b and %b, the output #10; is: %b", \$time, w1, w2, z); x = 1; y = 1;end #10; **\$finish** endmodule end х endmodule Test Bench У

< Schematic of an XOR gate connected to a stimulus generator >