# Memory

# **Read-Only Memories**

- Mask ROM

- Programmed permanently during manufacturing process

- Programmable ROM

- PROM

- programmed by fusing or anti-fusing process

- the process is irreversible

- Erasable PROM

- UV EPROM

- EEPROM

## **Random Access Memories**

- Transistor efficient methods for implementing storage elements

- Small RAM: 256 words by 4-bit

- Large RAM: 1 billion words by 1-bit

- Static RAMs and Dynamic RAMs

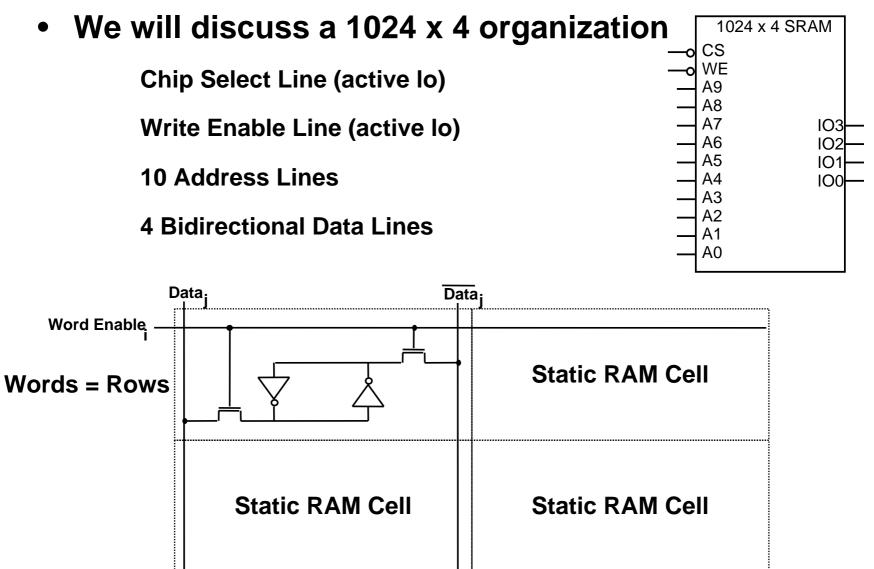

# **Static RAMs**

## Columns = Bits (Double Rail Encoded)

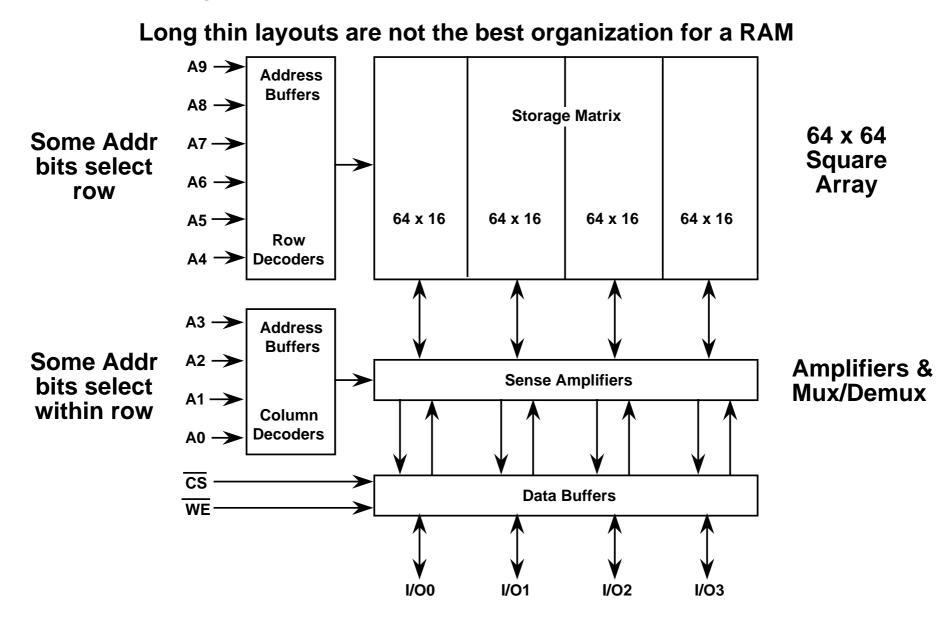

#### **RAM Organization**

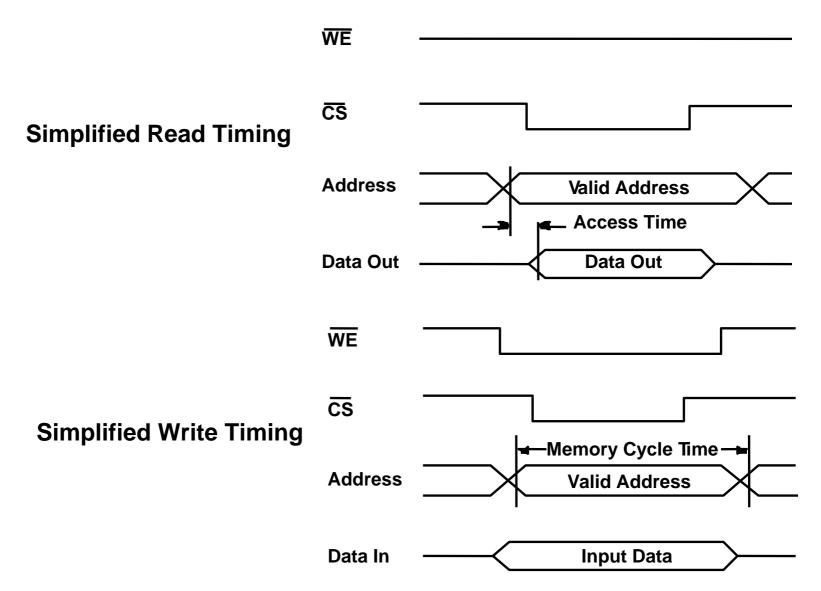

RAM Timing

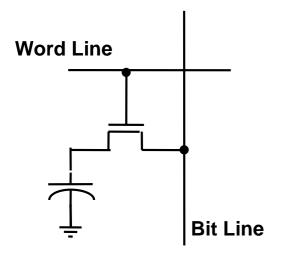

1 Transistor (+ capacitor) memory element Read: Assert Word Line, Sense Bit Line Write: Drive Bit Line, Assert Word Line Need for Refresh Cycles: storage decay in ms Destructive Read-Out Internal circuits read word and write back

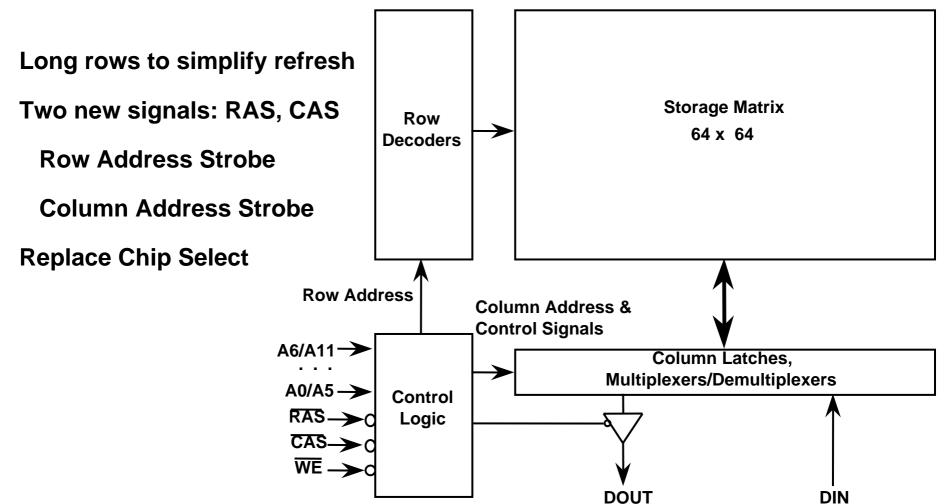

## **DRAM** Organization

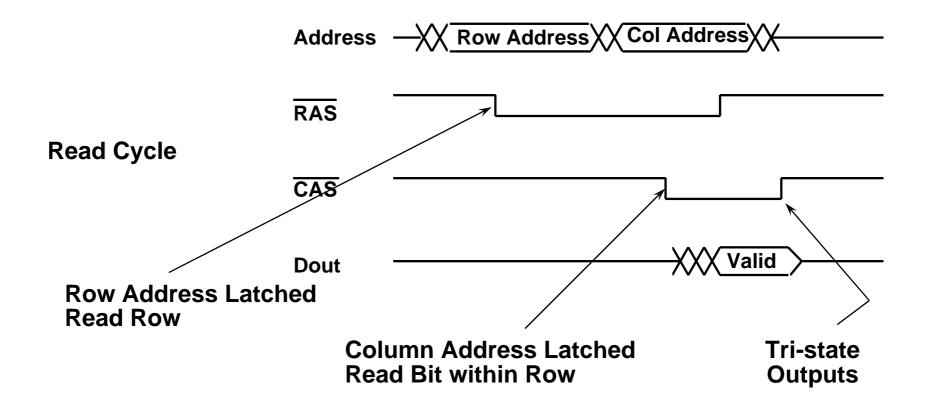

## RAS, CAS Addressing

Even to read 1 bit, an entire 64-bit row is read!

Separate addressing into two cycles: Row Address, Column Address Saves on package pins, speeds RAM access for sequential bits!

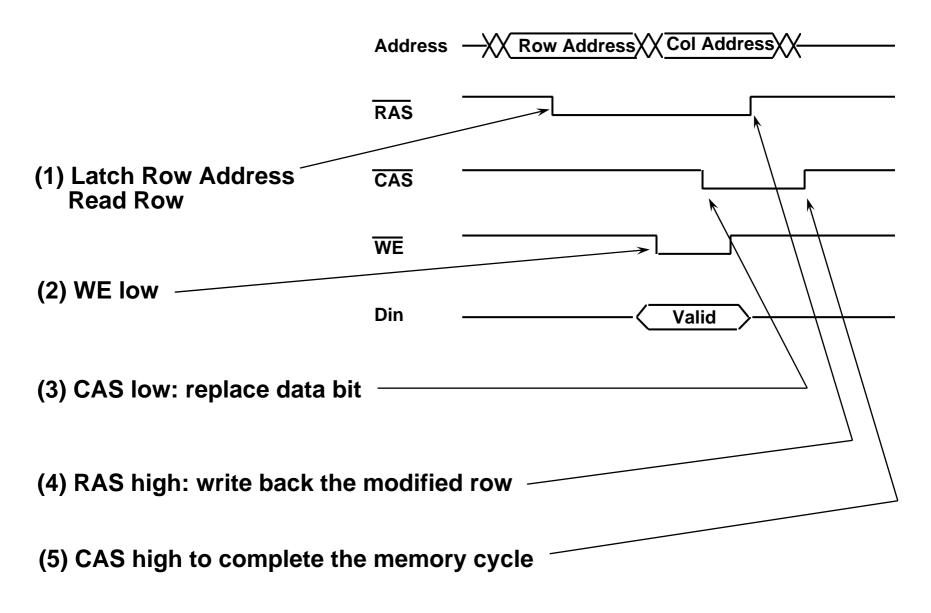

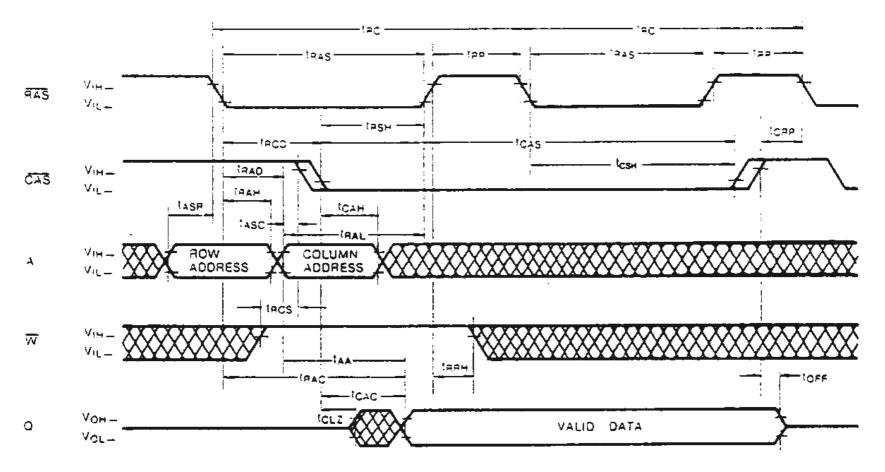

## Write Cycle Timing

RAM Refresh

**Refresh Frequency:**

4096 word RAM -- refresh each word once every 4 ms => This is one refresh cycle every 976 ns

Assume 120ns memory access cycle => 1 in 8 DRAM accesses!

But RAM is really organized into 64 rows => This is one refresh cycle every 62.5 μs(1 in 500 DRAM accesses)

Large capacity DRAMs have 256 rows, refresh once every 16  $\mu$ s

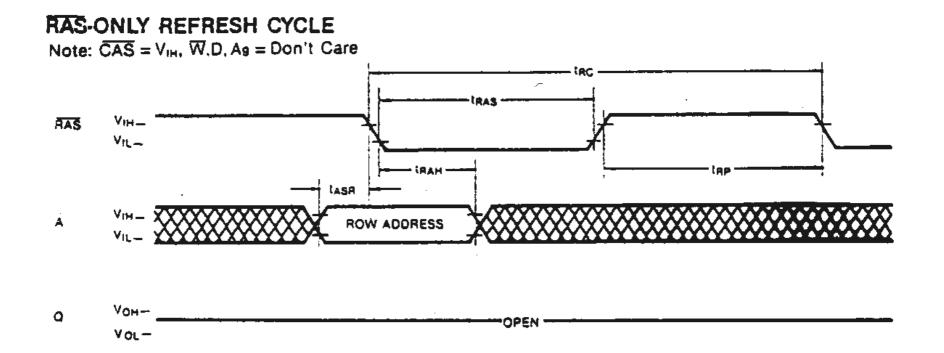

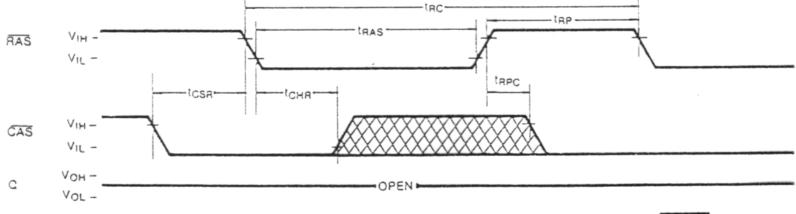

RAS-only Refresh (RAS cycling, no CAS cycling)

External controller remembers last refreshed row

Some memory chips maintain refresh row pointer

CAS before RAS refresh: if CAS goes low before RAS, then refresh

#### HIDDEN REFRESH CYCLE

#### CAS-BEFORE RAS REFRESH CYCLE

• DRAM Variations

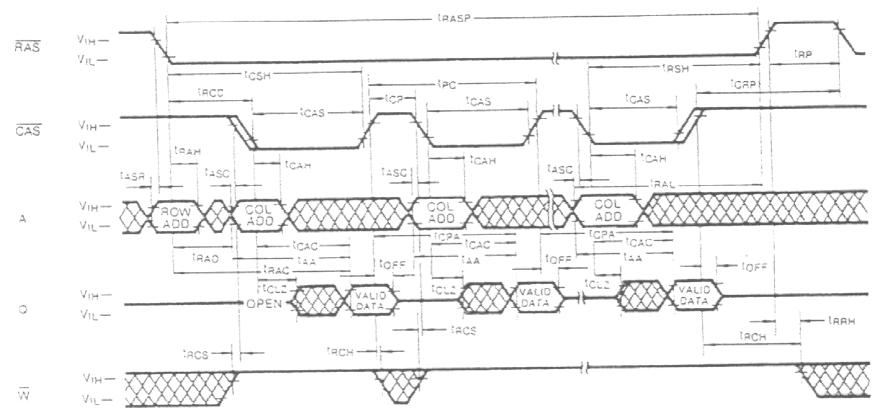

Page Mode DRAM:

read/write bit within last accessed row without RAS cycle

RAS, CAS, CAS, . . ., CAS, RAS, CAS, ...

New column address for each CAS cycle

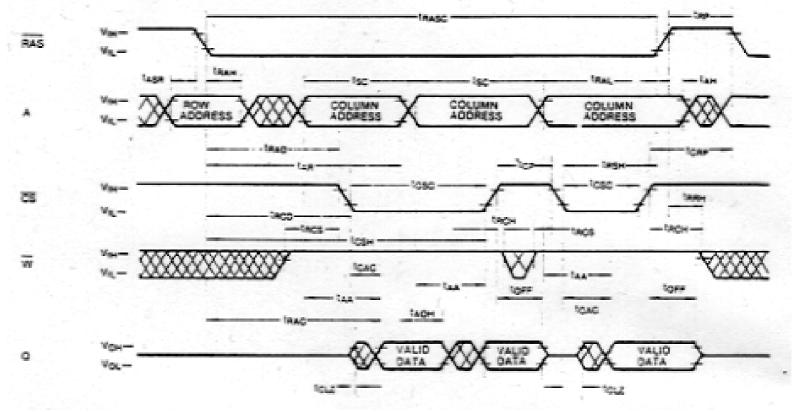

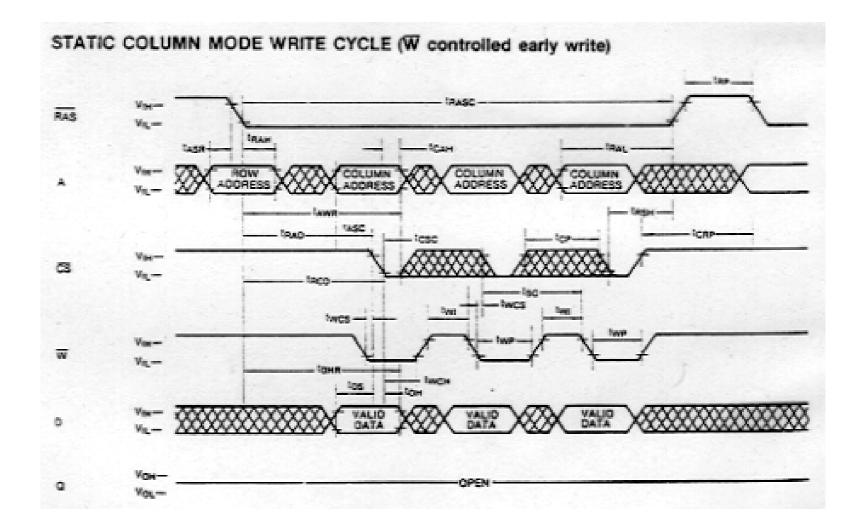

Static Column DRAM:

like page mode, except address bit changes signal new cycles rather than CAS cycling

on writes, deselect chip or CAS while address lines are changing

Nibble Mode DRAM:

like page mode, except that CAS cycling implies next column address in sequence -- no need to specify column address after first CAS

Works for 4 bits at a time (hence "nibble") RAS, CAS, CAS, CAS, CAS, RAS, CAS, CAS, CAS, CAS, ...

FAST PAGE MODE READ CYCLE

STATIC COLUMN MODE READ CYCLE

NIBBLE MODE READ CYCLE ines. Vite AAS.  $\mathcal{V}_{\mathcal{T}_{n-1}}$ LCSP .... INRSH Icap in Barry **NGAS** West-CAS INAD.  $V_{2,\infty}$ 12,000 14.36 INCP. INC.45 TOAH. 法的 TRAM. Vite\_\_\_\_ 8 00L 400 ROW à. 400 1905 iage: 14QH  $\infty$  $\infty$ Western 177 Wegen. -1012 Ingat: 1900 12,000 VAUS QATA NAUG GATA VALID DATA 74UO 0418 Nga-0 VOL-

- More advanced DRAM Technologies

- EDO DRAM (Extended Data Out DRAM)

- One access to the memory can begin before the last one has finished

- SDRAM (Synchronous DRAM)

- Tied to the system clock and is designed to be able to read or write memory in burst mode (after the initial read or write latency) at 1 clock cycle per access (zero wait states)

- DDR SDRAM (Double Data Rate SDRAM)

- Doubles the bandwidth of the memory by transferring data twice per cycle on both the rising and falling edges of the clock signal

- DRDRAM (Direct Rambus DRAM)

- SLDRAM (Synchronous-Link DRAM)