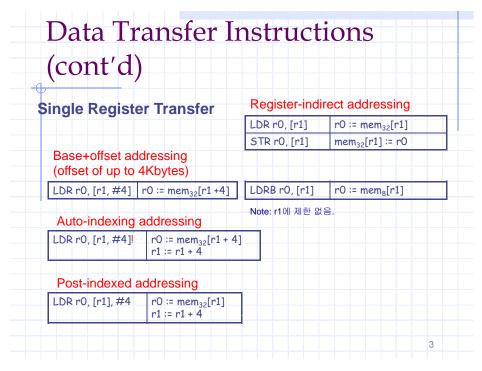

#### Data transfer instructions

- Single register load and store instructions

- Transfer unit: byte, half-word, word

- Multiple register load and store instructions

- Multiple transfer using a single instruction

- Useful for function entries/exits & bulk memory copy

- Single register swap instructions

- An atomic operation

- Useful when implementing semaphores and mutual exclusion in OS

2

#### **Data Transfer Instructions** (cont'd) COPY: LDR r1, .TABLE1 ; r1 points to TABLE1 LDR r2. TABLE2 ; r2 points to TABLE2 LOOP: LDR r0, [r1] STR r0, [r2] ADD r1, r1, #4 ADD r2, r2, #4 .TABLE1: ... LDR r1, .TABLE1 ; r1 points to TABLE1 .TABLE2:... LDR r2, .TABLE2 ; r2 points to TABLE2 LOOP: LDR r0, [r1], #4 STR r0, [r2], #4 .TABLE1: ... .TABLE2:..

## Data Transfer Instructions (cont'd)

- Example:

- C code: A[8] = h + A[8]

- A: an array of 100 words

- r1 : base address of the array A

- r3 : h

- ARM code:

ldr r2, [r1, #32] add r2, r3, r2

Str r2, [r1, #32]

Data Transfer Instructions (cont'd)

- $\bigcirc$  C code: g = h + A[i]

- r1 : base register for A

- g, h, i: r2, r3, r4

- ♦ ARM code:

ldr r5, [r1, r4, asl #2] add r2, r3, r5

6

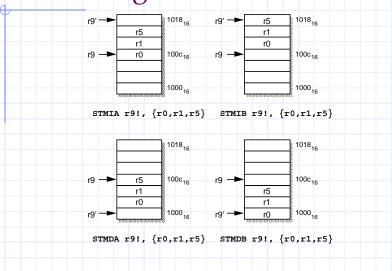

## Data Transfer Instructions (cont'd)

#### **Multiple Register data Transfers**

- Block copy view

- Up or down from the base register

- Address chagne before or after load/store

#### Block Load/Store

- IA Increment After

- IB Increment Before

- DA Decrement After

- DB Decrement Before

#### Stack Pop/Push

- FA full ascending

- EA empty ascending

- FD full descending

- ED empty descending

## Multiple register transfer addressing modes

### Block Memory Copy Example

loop

LDMIA r9!, {r0-r7}

STMIA r10!, {r0-r7}

CMP r9, r11

BNE loop

....

## The mapping between the stack and block copy views

| Addr<br>Mode |                     | Pop   | == LDM | Push  | == STM |

|--------------|---------------------|-------|--------|-------|--------|

| FA           | Full<br>Ascending   | LDMFA | LDMDA  | STMFA | STMIB  |

| FD           | Full<br>Descending  | LDMFD | LDMIA  | STMFD | STMDB  |

| EA           | Empty<br>Ascending  | LDMEA | LDMDB  | STMEA | STMIA  |

| ED           | Empty<br>Descending | LDMED | LDMIB  | STMED | STMDA  |

Push & Pop using LDM & STM

Full Stack (last full) vs. Empty Stack (next empty)

Ascending vs. Descending

10

#### Control flow instructions

| Branch | Interpretation   | Normal uses                                       |  |  |

|--------|------------------|---------------------------------------------------|--|--|

| В      | Unconditional    | Always take this branch                           |  |  |

| BAL    | Always           | Always take this branch                           |  |  |

| BEQ    | Equal            | Comparison equal or zero result                   |  |  |

| BNE    | Not equal        | Comparison not equal or non-zero result           |  |  |

| BPL    | Plus             | Result positive or zero                           |  |  |

| BMI    | Minus            | Result minus or negative                          |  |  |

| BCC    | Carry clear      | Arithmetic operation did not give carry-out       |  |  |

| BLO    | Lower            | Unsigned comparison gave lower                    |  |  |

| BCS    | Carry set        | Arithmetic operation gave carry -out              |  |  |

| BHS    | Higher or same   | Unsigned comparison gave higher or same           |  |  |

| BVC    | Overflow clear   | Signed integer operation; no overflow occurred    |  |  |

| BVS    | Overflow set     | Signed integer operation; overflow occurred       |  |  |

| BGT    | Greater than     | Signed integer comparison gave greater than       |  |  |

| BGE    | Greater or equal | Signed integer comparison gave greater or equal   |  |  |

| BLT    | Less than        | Signed integer comparison gave less than          |  |  |

| BLE    | Less or equal    | Signed integer comparison gave less than or equal |  |  |

| BHI    | Higher           | Unsigned comparison gave higher                   |  |  |

| BLS    | Lower or same    | Unsigned comparison gave lower or same            |  |  |

|        |                  |                                                   |  |  |

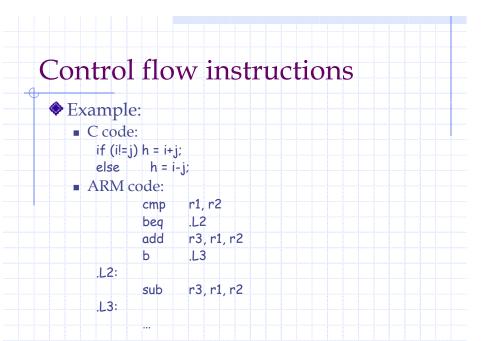

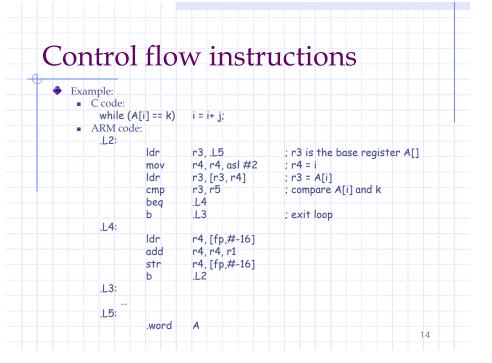

#### Control flow instructions

Example:

C code: if (i==j) h = i+j;

■ ARM code:

cmp r1, r2 bne .L2 add r3, r1, r2

.L2:

2

#### Software Interrupt Instruction

♦ Provide a mechanism to call O/S routines

```

; output r0<sub>[7:0]</sub>

SWI SWI_WriteC

; return from a user program back to monitor

SWI SWI_Exit

```

```

SWI{<cond>} SWI_number

Ir_svc = addr. of inst following the SWI

spsr_svc = cpsr

pc = vectors + 0x8

cpsr mode = SVC

cpsr I = 1 (mask IRQ interrupts)

```

#### SWI Handler Example

```

SWI_handler:

STMFD sp!, {r0-r12, lr}

LDR r10, [lr, #-4]

BIC r10, r10, #0xff000000

; the number in r10 used to call the service routine

BL service_routine

LDMFD sp!, {r0-r12, pc}^

```

### Jump tables

Useful for 'switch' statement:

```

JTAB: CMP rO, #0

BEQ SUBO

CMP rO, #1

BEQ SUB1

CMP rO, #2

BEQ SUB2

```

BL JTAB

Note: slow when the list is long, and all subroutines are equally frequent

```

BL JTAB

...

JTAB: ADR r1, SUBTAB

CMP r0, #SUBMAX; overrun?

LDRLS pc, [r1, r0, LSL #2]

B ERROR

SUBTAB: DCD SUB0

DCD SUB1

DCD SUB2

...

```

#### Hello ARM World!

```

AREA HelloW, CODE, READONLY; declare code area

SWI_WriteC

EQU

; output character in rO

SWI Exit

EQU

; finish program

ENTRY

; code entry point

START: ADR r1. TEXT

: r1 <- Hello ARM World!

LOOP: LDRB r0, [r1], #1

; get the next byte

CMP r0, #0

; check for text end

SWINE SWI WriteC

; if not end of string, print

BNF LOOP

SWI SWI_Exit

: end of execution

TEXT = "Hello ARM World!", &Oa, &Od, O

END

```

#### **PSR** Instruction

- Two instructions for controlling PSR

- MRS Rd, <cpsr | spsr>

- MSR <cpsr | spsr>\_<fields>, Rm

- MSR <cpsr | spsr>\_<fields>, #immediate

- Fields: byte regions of PSR

- control (c): psr[0:7]

- Extension (x): psr[8:15]

- status (s): psr[16:23]

- flags (f): psr[24:31]

21

# MRS & MSR Example

MRS r1, cpsr

BIC r1, r1, #0x80

; clear bit 7

MSR cpsr\_c, r1

22

### Coprocessor Instruction

- ♦ MRC: move from coprocessor register to register

- ♦ MCR: move from register to coprocessor register

### CP15: ARM System Control Coprocessor

- on-chip cache or caches, memory management or protection unit, write buffer, prefetch buffer, branch target cache and system configuration

- In Supervisor mode, MRC,MCR used to access registers

| Register Purpose | 9 |

|------------------|---|

|------------------|---|

- D ID Register

- 1 Control

- 2 Translation Table Base

- 3 Domain Access Control

- 5 Fault Status

- 5 Fault Address

- 7 Cache Operations

- 8 TLB Operations

- 9 Read Buffer Operations

- 10 TLB Lockdown

- 13 Process ID Mapping

- 14 Debug Support

- 15 Test and Clock Control

4, 11-12 UNUSED

3

### **Loading Constant Instruction**

- Two pseudoinstructions to move a 32-bit value into a register

- LDR Rd, =constant

- MOV Rd, #constant

LDR r0, =0xff == MOV r0, #0xff

- ADR Rd, label

- Rd = 32-bit relative address (PC relative add or subtract)

25