## **Device Driver** for Serial Communication

## **RTOS Support**

- NOT necessarily responsible everything

- RTOS system calls

#### Interrupt Management

rtl\_request\_irq

rtl\_free\_irq

rtl\_hard\_enable\_irq

rtl\_hard\_disable\_irq

#### Time Management

clock\_gethrtime

clock\_gettime

clock\_settime

gethrtime

nanosleep

#### Task Management

pthread\_create

pthread\_setschedparam// pri. sched

pthread\_make\_periodic\_np

pthread\_wait\_np

pthread\_delete\_np

pthread\_cancel

pthread\_join

#### **Task Communication**

FIFO

Shared Memory

Signal

#### **Mutual Exclusion**

Lock

Semaphore

#### Device drivers

rt\_com

rtsock

#### Various Devices

- Serial com (UART RS232)

- Parallel com

- Ethernet card (TCP/IP socket interface)

- CAN bus

- CDMA communication chip set

- LCD

#### Device driver (1)

- Simplify the access to devices

- Hide device specific details as much as possibile

- Provide a consistent way to access different devices

- ioctl(), read(), write()

#### Device Driver (2)

- Writing a device driver

- Understand basic physical mechanism

- Understand supporting HW chips

- Implement standard interface functions

- Register necessary interrupt handlers

- Define internal data structure (message buffer)

- Implement standard interface functions

- ioctl, read, write

#### Device Driver (2)

- A device driver <u>USER</u> only needs to know (standard) interface functions without knowledge of physical properties of the device

- A device driver DEVELOPER needs to know physical details and provides the interface functions as specified

# Let's take serial com as an example

Physical communication mechanism

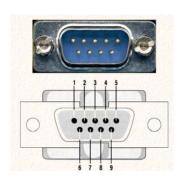

RS-232:widely used industrial standard

| pin | name | function                                                         |  |  |

|-----|------|------------------------------------------------------------------|--|--|

| 1   | DCD  | asserted when the modem detects a<br>"carrier"from the other end |  |  |

| 2   | RD   | Serial data input                                                |  |  |

| 3   | TD   | Serial data output                                               |  |  |

| 4   | DTR  | DTE (UART) ready to establish a link                             |  |  |

| 5   | SG   | Signal ground                                                    |  |  |

| 6   | DSR  | DCE (modem) ready to establish a link                            |  |  |

| 7   | RTS  | DTE (UART) ready to exchange data                                |  |  |

| 8   | CTS  | DCE (modem) ready to exchange data                               |  |  |

| 9   | RI   | Asserted when modem detects a ringing signal from the PSTN       |  |  |

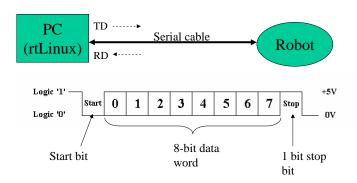

# One word communication (8bit data, no parity, 1 stop bit)

• Why we need start bit in asynchronous communication even when the both sides use the same baud rate?

# Program controls bit level timing? (think about 115200 bps)

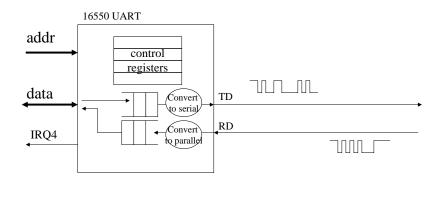

• UART (8250 and compatibles) will help

# Serial communication is possible by touching UART registers

• Port Addresses & IRQ's (standard PC)

| Name  | Address | IRQ |

|-------|---------|-----|

| COM 1 | 3F8     | 4   |

| COM 2 | 2F8     | 3   |

| COM 3 | 3E8     | 4   |

| COM 4 | 2E8     | 3   |

• Table of registers

| Base Address     | DLAB | Read/Write | Abr.             | Register Name                     |

|------------------|------|------------|------------------|-----------------------------------|

|                  | =0   | Write      | -                | Transmitter Holding Buffer        |

| + 0              | =0   | Read       | -                | Receiver Buffer                   |

|                  | =1   | ReadWrite  | -                | Divisor Latch Low Byte            |

| + 1              | =0   | ReadWrite  | IER              | Interrupt Enable Register         |

| T 1              | =1   | Read/Write | -                | Divisor Latch High Byte           |

| + 2              | -    | Read       | IIR              | Interrupt Identification Register |

| + 2              | -    | Write      | FCR              | FIFO Control Register             |

| + 3              | -    | Read/Write | LCR              | Line Control Register             |

| + 4              | -    | Read/Write | MCR              | Modem Control Register            |

| + 5              | -    | Read       | LSR              | Line Status Register              |

| + 6              | -    | Read       | MSR              | Modem Status Register             |

| + 7 - Read/Write |      | -          | Scratch Register |                                   |

# Divisor Latch Low/High Bytes (program Baud Rate Generator)

| Speed (BPS) | Divisor (Dec) | Divisor Latch High Byte | Divisor Latch Low Byte |

|-------------|---------------|-------------------------|------------------------|

| 50          | 2304          | 09h                     | 00h                    |

| 300         | 384           | 01h                     | 80h                    |

| 600         | 192           | 00h                     | C0h                    |

| 2400        | 48            | 00h                     | 30h                    |

| 4800        | 24            | 00h                     | 18h                    |

| 9600        | 12            | 00h                     | 0Ch                    |

| 19200       | 6             | 00h                     | 06h                    |

| 38400       | 3             | 00h                     | 03h                    |

| 57600       | 2             | 00h                     | 02h                    |

| 115200      | 1             | 00h                     | 01h                    |

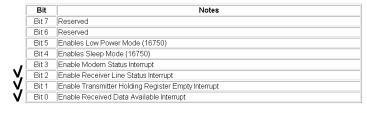

#### Interrupt Enable Register (IER) and Interrupt Identification Register (IIR)

IER

• IIR (read only)

| Bit          | Notes   |                             |                                              |  |  |

|--------------|---------|-----------------------------|----------------------------------------------|--|--|

| Bits 6 and 7 | Bit 6   | Bit 7                       |                                              |  |  |

|              | 0       | 0                           | No FIFO                                      |  |  |

|              | 0       | 1 FIFO Enabled but Unusable |                                              |  |  |

|              | 1       | 1                           | 1 FIFO Enabled                               |  |  |

| Bit 5        | 64 Byte | Fifo En                     | abled (16750 only)                           |  |  |

| Bit 4        | Reserv  | ed                          |                                              |  |  |

| Bit 3        | 0       | Reserv                      | ed on 8250, 16450                            |  |  |

|              | 1       | 16550                       | Time-out Interrupt Pending                   |  |  |

| Bits 1 and 2 | Bit 2   | Bit 1                       |                                              |  |  |

|              | 0       | 0                           | Modem Status Interrupt                       |  |  |

|              | 0       | 1                           | Transmitter Holding Register Empty Interrupt |  |  |

|              | 1       | 0                           | Received Data Available Interrupt            |  |  |

|              | 1       | 1                           | Receiver Line Status Interrupt               |  |  |

| Bit 0        | 0       | Interrup                    | t Pending                                    |  |  |

|              | 1       | No Interrupt Pending        |                                              |  |  |

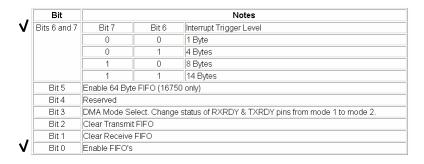

### FIFO Control Register (FCR)

• FCR (write only)

### Line Control Register (LCR)

LCR

| Bit 7         | 1       | Divisor Latch Access Bit                                                                   |                                                                           |                      |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------|--|--|--|

|               | 0       | Access                                                                                     | Access to Receiver buffer, Transmitter buffer & Interrupt Enable Register |                      |  |  |  |

| Bit 6         | Set Bre | ak Enabl                                                                                   | 9                                                                         |                      |  |  |  |

| Bits 3, 4 And | Bit 5   | Bit 4                                                                                      | Bit 3                                                                     | Parity Select        |  |  |  |

| 5             | Х       | Х                                                                                          | 0                                                                         | No Parity            |  |  |  |

|               | 0       | 0                                                                                          | 1                                                                         | Odd Parity           |  |  |  |

|               | 0       | 1                                                                                          | 1                                                                         | Even Parity          |  |  |  |

|               | 1       | 0                                                                                          | 1                                                                         | High Parity (Sticky) |  |  |  |

|               | 1       | 1                                                                                          | 1                                                                         | Low Parity (Sticky)  |  |  |  |

| Bit 2         | Length  | of Stop B                                                                                  | it                                                                        |                      |  |  |  |

|               | 0       | One Stop Bit                                                                               |                                                                           |                      |  |  |  |

|               | 1       | 2 Stop bits for words of length 6,7 or 8 bits or 1.5 Stop Bits for Word lengths of 5 bits. |                                                                           |                      |  |  |  |

| Bits 0 And 1  | Bit 1   | Bit 0                                                                                      | Word L                                                                    | ength                |  |  |  |

|               | 0       | 0                                                                                          | 5 Bits                                                                    |                      |  |  |  |

|               | 0       | 1                                                                                          | 6 Bits                                                                    |                      |  |  |  |

|               | 1       | 0                                                                                          | 7 Bits                                                                    |                      |  |  |  |

|               | 1       | 1                                                                                          | 8 Bits                                                                    |                      |  |  |  |

7

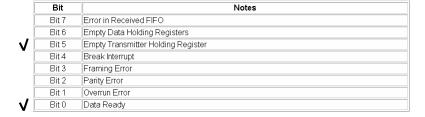

### Line Status Register (LSR)

• LSR (read only)

### Modem Control Register (MCR)

• MCR

| Bit   | Notes                                 |  |  |

|-------|---------------------------------------|--|--|

| Bit 7 | Reserved                              |  |  |

| Bit 6 | Reserved                              |  |  |

| Bit 5 | Autoflow Control Enabled (16750 only) |  |  |

| Bit 4 | LoopBack Mode                         |  |  |

| Bit 3 | Aux Output 2                          |  |  |

| Bit 2 | Aux Output 1                          |  |  |

| Bit 1 | Force Request to Send                 |  |  |

| Bit 0 | Force Data Terminal Ready             |  |  |

## Modem Status Register (MSR)

• MSR (read only)

| Bit   | Notes                        |  |  |  |

|-------|------------------------------|--|--|--|

| Bit 7 | Carrier Detect               |  |  |  |

| Bit 6 | Ring Indicator               |  |  |  |

| Bit 5 | Data Set Ready               |  |  |  |

| Bit 4 | Clear To Send                |  |  |  |

| Bit 3 | Delta Data Carrier Detect    |  |  |  |

| Bit 2 | Trailing Edge Ring Indicator |  |  |  |

| Bit 1 | Delta Data Set Ready         |  |  |  |

| Bit 0 | Delta Clear to Send          |  |  |  |

• For more details, see http://www.beyondlogic.org/serial/serial.htm

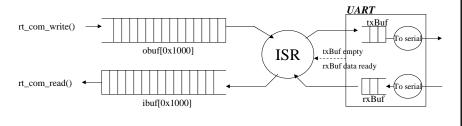

#### How the driver should work?

- Three standard interface functions

- rt\_com\_setup: configure serial com parameters

- rt\_com read: read data received from COM

- int rt\_com\_read(com, char \*ptr, byteCountToBeRead);

- rt com write: write data to be transmitted to COM

- void rt\_com\_write(com, char \*ptr, byteCountToBeWritten);

#### How the driver should work?

- Real-Time response!

- Non-blocked I/O (cf. Blocked I/O)

- "Blocking until the read/write is actually done" is not good for real-time.

- Return immediately even if the operation is partially done and let the rest done whenever UART is ready.

- This allows RT\_Thread make a decision with the partial result.

- Use internal data structure (message buffer (cf. HW buffer))

#### **Driver Initialization**

- Initialize the internal data structure

- Register IRQ4 (COM1) and IRQ3 (COM2) Interrupt Service Routines (ISRs)

- rtl\_request\_irq(irq, isr);

- rtl\_hard\_enable\_irq(irq);

- Setup UART

- Initial setup

- Setup can be changed later by Rt thread (rt\_com\_setup)

#### Source code

#### rt\_com\_setup

- Input parameters: com, baud, parity, stopbits, wordlength

- Operations

- Disable all UART interrupts IER

- Clear all status registers IIR, LSR, MSR, ReceiverBuffer

- Setup baud rate DivisorLatchLow, DivisorLatchHigh

- Setup stopbits, parity, wordlength LCR

- Assert RS-232 signals DTR and RTS MCR

- Interrupt enable for "receive data" and "receive line status change (if LSR changes)" – *IER*

- Enable fifo FCR

#### Source code

```

/* Stop everything, set DLAB */

outb( 0x00, base + RT_COM_IER );

outb( 0x80, base + RT_COM_LCR );

/* clear irg */

inb( base + RT_COM_LSR );

inb( base + RT_COM_LSR );

inb( base + RT_COM_ESR );

inb( base + RT_COM_ESR );

p>>error = 0; //!! init. last error code

p>>callback = 0;

if( 0 == baud ) {

/* return */

} else if( 0 > baud ) {

MOD_DEC_USE_COUNT;

} else {

MOD_INC_USE_COUNT;

divider = p>baud base / baud;

outb( divider * 256, base + RT_COM_DLL );

outb( divider * 256, base + RT_COM_DLM );

/* bits 3, 4 + 5 determine parity - clear all other bits */

par &= 0x38;

/* set transmission parameters and clear DLAB */

outb( (wordlength - 5 ) + ( ( stopbits - 1 ) << 2 ) + par, base + R

T_COM_LCR );

p>>mcr = RT_COM_DTR + RT_COM_RTS + RT_COM_Out1 + RT_COM_out2;

outb( p>>mcr , base + RT_COM_RTS + RT_COM_Out1 + RT_com_out2;

outb( p>>mcr , base + RT_COM_ER );

if (p>>mode & 0x01) p->ier = 0x05; /* if no hs signals enable only r

eceiver interrupts */

outb( p>>ier = 0x0D; /* else enable receiver and modem

interrupts */

outb( p>>ier, base + RT_COM_IER );

rt_com_enable_fifo( base, RT_COM_FIFO_TRIGGER, 0 );

p>>used |= 0x02; /* mark setup done */

}

```

#### rt\_com\_read

- Input parameters: com, dataBuf, byteCountToBeRead

- Operations

- rt\_com\_irq\_off: enter critical section

- Copy from "rt\_com ibuf" to "dataBuf" up to actualByteCount = min(byteCountToBeRead, byteCountReadyInBuffer)

- rt\_com\_irq\_leave: leave critical section

- Return "actualByteCount"

- Note: No blocking inside rt\_com\_read

#### Source code

13

#### rt\_com\_write

- Input parameters: com, dataBuf, byteCountToBeWritten

- Operations

- rt\_com\_irq\_off: enter critical section

- Copy data from "dataBuf" to "rt\_com obuf" (no of bytes = byteCountToBeWritten)

- Enable UART interrupt "Transmitter Holding Register Empty" –

IER

- rt\_com\_irq\_leave: leave critical section

- Note: No blocking inside rt\_com\_write

#### Source code

#### **ISR**

- Triggered by "line-status-change", "receive-data-ready", and "transmit-holding-buffer-empty"

- Operations

- Check if received data is ready in Rx HW buffer LSR

- While there is a byte in Rx HW buffer, copy it to "rt\_com ibuf"

- Check if there is a room in "transmit-holding-buffer" LSR

- If rt\_com obuf is not empty (data to be transmitted), copy up to 16 (Tx HW buffer size) bytes to Tx HW buffer

- If rt\_com obuf becomes empty (no more data to be transmitted), disable "transmit-holding-buffer-empty" interrupt – IER

# Check if received data is ready Check if txHW buffer is empty Check if txHW buffe

## User only needs to know

- Three standard interface functions

- rt\_com\_setup: configure serial com parameters

- rt\_com read: read data received from COM

- int rt\_com\_read(com, char \*ptr, byteCountToBeRead);

- rt\_com write: write data to be transmitted to COM

- void rt\_com\_write(com, char \*ptr, byteCountToBeWritten);