| Two's Compleme                                        |                                            | a <sub>3</sub>                 | a <sub>2</sub>                 | a <sub>1</sub>                | a <sub>0</sub> |                               |                               |

|-------------------------------------------------------|--------------------------------------------|--------------------------------|--------------------------------|-------------------------------|----------------|-------------------------------|-------------------------------|

|                                                       |                                            | X                              | -x <sub>4</sub>                | x <sub>3</sub>                | x <sub>2</sub> | X <sub>1</sub>                | x <sub>0</sub>                |

|                                                       |                                            |                                | -a <sub>4</sub> x <sub>0</sub> | a <sub>3</sub> x <sub>0</sub> | $a_2 x_0$      | a <sub>1</sub> x <sub>0</sub> | a <sub>0</sub> x <sub>0</sub> |

| +                                                     |                                            | -a <sub>4</sub> x <sub>1</sub> | a <sub>3</sub> x <sub>1</sub>  | $a_2 x_1$                     | $a_1 x_1$      | a <sub>0</sub> x <sub>1</sub> |                               |

|                                                       | -a <sub>4</sub> x <sub>2</sub>             | $a_3 x_2$                      | $a_2 x_2$                      | $a_1 x_2$                     | $a_0 x_2$      |                               |                               |

| -a <sub>4</sub> x                                     | <sub>3</sub> a <sub>3</sub> x <sub>3</sub> | $a_2 x_3$                      | $a_1 x_3$                      | a <sub>0</sub> x <sub>3</sub> |                |                               |                               |

| <b>0</b> $a_4x_4 - a_3x_4$                            | $a -a_2 x_4$                               | -a <sub>1</sub> x <sub>4</sub> | -a <sub>0</sub> x <sub>4</sub> |                               |                |                               |                               |

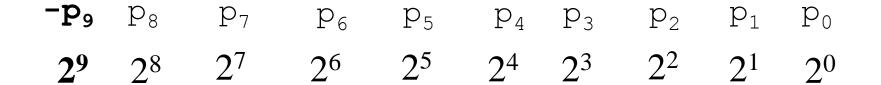

| - <b>P</b> <sub>9</sub> P <sub>8</sub> P <sub>7</sub> | p <sub>6</sub>                             | $p_5$                          | p <sub>4</sub>                 | $p_3$                         | p <sub>2</sub> | p <sub>1</sub>                | p <sub>0</sub>                |

| $2^9$ $2^8$ $2^7$                                     | 26                                         | $2^{5}$                        | $2^{4}$                        | 2 <sup>3</sup>                | $2^{2}$        | $2^{1}$                       | 20                            |

#### SD number in accumulating partial products

Two's complement number in result

| $\mathbf{p}_9$ | $p_8$ | $p_7$   | p <sub>6</sub> | $p_5$ | $p_4$   | $p_3$   | $p_2$   | $p_1$   | p <sub>0</sub> |

|----------------|-------|---------|----------------|-------|---------|---------|---------|---------|----------------|

| -29            | 28    | $2^{7}$ | $2^{6}$        | 25    | $2^{4}$ | $2^{3}$ | $2^{2}$ | $2^{1}$ | $2^{0}$        |

# Baugh-Wooley Two's Complement Multiplier

|                |                                |                                | -                              | -a <sub>4</sub>                | a <sub>3</sub>                | a <sub>2</sub>                | a <sub>1</sub>                | a <sub>0</sub>                |

|----------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

|                |                                | Σ                              | K -                            | -x4                            | X <sub>3</sub>                | x <sub>2</sub>                | X <sub>1</sub>                | X <sub>0</sub>                |

|                |                                |                                |                                | -a <sub>4</sub> x <sub>0</sub> | a <sub>3</sub> x <sub>0</sub> | a <sub>2</sub> x <sub>0</sub> | a <sub>1</sub> x <sub>0</sub> | a <sub>0</sub> x <sub>0</sub> |

|                |                                |                                | -a <sub>4</sub> x <sub>1</sub> | a <sub>3</sub> x <sub>1</sub>  | $a_2 x_1$                     | $a_1 x_1$                     | a <sub>0</sub> x <sub>1</sub> |                               |

|                |                                | -a <sub>4</sub> x <sub>2</sub> | a <sub>3</sub> x <sub>2</sub>  | $a_2 x_2$                      | $a_1 x_2$                     | $a_0 x_2$                     |                               |                               |

|                | -a <sub>4</sub> x <sub>3</sub> | a <sub>3</sub> x <sub>3</sub>  | $a_2 x_3$                      | a <sub>1</sub> x <sub>3</sub>  | a <sub>0</sub> x <sub>3</sub> |                               |                               |                               |

| $a_4 x_4$      | -a <sub>3</sub> x <sub>4</sub> | -a <sub>2</sub> x <sub>4</sub> | -a <sub>1</sub> x <sub>4</sub> | -a <sub>0</sub> x <sub>4</sub> | 1                             |                               |                               |                               |

| p <sub>8</sub> | p <sub>7</sub>                 | p <sub>6</sub>                 | р <sub>5</sub>                 | p <sub>4</sub>                 | р <sub>3</sub>                | p <sub>2</sub>                | p <sub>1</sub> :              | p <sub>0</sub>                |

| p <sub>8</sub> | p <sub>7</sub>                 | p <sub>6</sub>                 | $p_5$                          | p <sub>4</sub>                 | p <sub>3</sub>                | p <sub>2</sub>                | p <sub>1</sub>                | p <sub>0</sub>                |

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008, John Wiley

+

-**p**<sub>9</sub>

$\mathbf{p}_9$

| Baugh-V | Voolev 7 | <b>Fwo's</b> | Comple | ement | <b>Multip</b>  | lier |

|---------|----------|--------------|--------|-------|----------------|------|

| Duagn   | , 0010 5 |              | Compr  |       | <b>Traitip</b> |      |

|   |                 |                  | •                              |                                | -                              |                               |                               | -              |                               |                               |

|---|-----------------|------------------|--------------------------------|--------------------------------|--------------------------------|-------------------------------|-------------------------------|----------------|-------------------------------|-------------------------------|

|   |                 |                  |                                |                                |                                | -a <sub>4</sub>               | a <sub>3</sub>                | a <sub>2</sub> | a <sub>1</sub>                | a <sub>0</sub>                |

|   |                 |                  |                                |                                | X                              | -x4                           | x <sub>3</sub>                | x <sub>2</sub> | x <sub>1</sub>                | x <sub>0</sub>                |

|   |                 |                  |                                |                                |                                | $a_4 \overline{x}_0$          | a <sub>3</sub> x <sub>0</sub> | $a_2 x_0$      | $a_1 x_0$                     | a <sub>0</sub> x <sub>0</sub> |

| + |                 |                  |                                |                                | $a_4 \overline{x}_1$           | a <sub>3</sub> x <sub>1</sub> | $a_2 x_1$                     | $a_1 x_1$      | a <sub>0</sub> x <sub>1</sub> |                               |

|   |                 |                  |                                | $a_4 \overline{x}_2$           | $a_3 x_2$                      | $a_2 x_2$                     | $a_1 x_2$                     | $a_0 x_2$      |                               |                               |

|   |                 |                  | $a_4 \overline{x}_3$           | a <sub>3</sub> x <sub>3</sub>  | $a_2 x_3$                      | a <sub>1</sub> x <sub>3</sub> | a <sub>0</sub> x <sub>3</sub> |                |                               |                               |

|   |                 | $a_4 x_4$        | $\overline{a}_3 x_4$           | $\overline{a}_2 x_4$           | $\overline{a}_1 x_4$           | $\overline{a}_0 x_4$          |                               |                |                               |                               |

|   |                 | $\overline{a}_4$ | a <sub>4</sub> -a <sub>4</sub> | a <sub>4</sub> -a <sub>4</sub> | a <sub>4</sub> -a <sub>4</sub> | a <sub>4</sub>                |                               |                |                               |                               |

|   | -1              | $\overline{X}_4$ | $X_4 - X_4$                    | $X_4 X_4$                      | $X_4 X_4$                      | $X_4$                         |                               |                |                               |                               |

|   | -p <sub>9</sub> | p <sub>8</sub>   | p <sub>7</sub>                 | p <sub>6</sub>                 | р <sub>5</sub>                 | p <sub>4</sub>                | р <sub>3</sub>                | p <sub>2</sub> | p <sub>1</sub>                | p <sub>0</sub>                |

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008, John Wiley

| B | Baugh-Wooley Multiplier |                  |                      |                               |                      |                               |                               |                |                               |                               |

|---|-------------------------|------------------|----------------------|-------------------------------|----------------------|-------------------------------|-------------------------------|----------------|-------------------------------|-------------------------------|

| ļ |                         |                  |                      |                               |                      | -a4                           | a <sub>3</sub>                | a <sub>2</sub> | a <sub>1</sub>                | a <sub>0</sub>                |

|   |                         |                  |                      |                               | X                    | -x <sub>4</sub>               | X <sub>3</sub>                | x <sub>2</sub> | X <sub>1</sub>                | x <sub>0</sub>                |

|   |                         |                  |                      |                               |                      | $a_4 \overline{x}_0$          | a <sub>3</sub> x <sub>0</sub> | $a_2 x_0$      | a <sub>1</sub> x <sub>0</sub> | a <sub>0</sub> x <sub>0</sub> |

| + |                         |                  |                      |                               | $a_4 \overline{x}_1$ | a <sub>3</sub> x <sub>1</sub> | $a_2 x_1$                     | $a_1 x_1$      | a <sub>0</sub> x <sub>1</sub> |                               |

|   |                         |                  |                      | $a_4 \overline{x}_2$          | $a_3 x_2$            | $a_2 x_2$                     | $a_1 x_2$                     | $a_0 x_2$      |                               |                               |

|   |                         |                  | $a_4 \overline{x}_3$ | a <sub>3</sub> x <sub>3</sub> | $a_2 x_3$            | a <sub>1</sub> x <sub>3</sub> | a <sub>0</sub> x <sub>3</sub> |                |                               |                               |

|   |                         | $a_4 x_4$        | $\overline{a}_3 x_4$ | $\overline{a}_2 x_4$          | $\overline{a}_1 x_4$ | $\overline{a}_0 x_4$          |                               |                |                               |                               |

|   |                         | $\overline{a}_4$ |                      |                               |                      | a <sub>4</sub>                |                               |                |                               |                               |

|   | 1                       | $\overline{X}_4$ |                      |                               |                      | X <sub>4</sub>                |                               |                |                               |                               |

|   | $\mathbf{p}_9$          | p <sub>8</sub>   | p <sub>7</sub>       | p <sub>6</sub>                | $p_5$                | $p_4$                         | p <sub>3</sub>                | $p_2$          | p <sub>1</sub>                | p <sub>0</sub>                |

### Modified Baugh-Wooley Multiplier

|   |                 |                  |                     |                               |                     | -a <sub>4</sub>               | a <sub>3</sub>                | a <sub>2</sub> | $a_1$          | a <sub>0</sub>                |

|---|-----------------|------------------|---------------------|-------------------------------|---------------------|-------------------------------|-------------------------------|----------------|----------------|-------------------------------|

|   |                 |                  |                     |                               | X                   | -x <sub>4</sub>               | X <sub>3</sub>                | x <sub>2</sub> | $X_1$          | x <sub>0</sub>                |

|   |                 |                  |                     |                               | -1                  | $\overline{a_4x_0}$           | a <sub>3</sub> x <sub>0</sub> | $a_2 x_0$      | $a_1 x_0$      | a <sub>0</sub> x <sub>0</sub> |

| + |                 |                  |                     | -1                            | $\overline{a_4x_1}$ | a <sub>3</sub> x <sub>1</sub> | $a_2 x_1$                     | $a_1 x_1$      | $a_0 x_1$      |                               |

|   |                 |                  | -1                  | $\overline{a_4x_2}$           | $a_3 x_2$           | $a_2 x_2$                     | $a_1 x_2$                     | $a_0 x_2$      |                |                               |

|   |                 | -1               | $\overline{a_4x_3}$ | a <sub>3</sub> x <sub>3</sub> | $a_2 x_3$           | $a_1 x_3$                     | a <sub>0</sub> x <sub>3</sub> |                |                |                               |

|   |                 | $a_4 x_4$        | $\overline{a_3x_4}$ | $\overline{a_2x_4}$           | $\overline{a_1x_4}$ | $\overline{a_0 x_4}$          |                               |                |                |                               |

|   | -p <sub>9</sub> | p p <sub>8</sub> | p <sub>7</sub>      | p <sub>6</sub>                | р <sub>5</sub>      | p <sub>4</sub>                | р <sub>3</sub>                | p <sub>2</sub> | p <sub>1</sub> | p <sub>0</sub>                |

### Modified Baugh-Wooley Multiplier

|            |                               |                     |                               |                     | -a4                           | a <sub>3</sub>                | a <sub>2</sub>                | a <sub>1</sub>                | a <sub>0</sub>                |

|------------|-------------------------------|---------------------|-------------------------------|---------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

|            |                               |                     |                               | X                   | -x4                           | X <sub>3</sub>                | x <sub>2</sub>                | X <sub>1</sub>                | x <sub>0</sub>                |

|            |                               |                     | -1                            | +1                  | $\overline{a_4x_0}$           | a <sub>3</sub> x <sub>0</sub> | a <sub>2</sub> x <sub>0</sub> | a <sub>1</sub> x <sub>0</sub> | a <sub>0</sub> x <sub>0</sub> |

| +          |                               |                     | -1                            | $\overline{a_4x_1}$ | a <sub>3</sub> x <sub>1</sub> | $a_2 x_1$                     | $a_1 x_1$                     | a <sub>0</sub> x <sub>1</sub> |                               |

|            |                               | -1                  | $\overline{a_4x_2}$           | $a_3 x_2$           | $a_2 x_2$                     | $a_1 x_2$                     | a <sub>0</sub> x <sub>2</sub> |                               |                               |

|            | -1                            | $\overline{a_4x_3}$ | a <sub>3</sub> x <sub>3</sub> | $a_2 x_3$           | $a_1 x_3$                     | a <sub>0</sub> x <sub>3</sub> |                               |                               |                               |

|            | a <sub>4</sub> x <sub>4</sub> | $\overline{a_3x_4}$ | $\overline{a_2x_4}$           | $\overline{a_1x_4}$ | $\overline{a_0 x_4}$          |                               |                               |                               |                               |

| - <b>F</b> | <b>9</b> p <sub>8</sub>       | p <sub>7</sub>      | p <sub>6</sub>                | $p_5$               | p <sub>4</sub>                | p <sub>3</sub>                | p <sub>2</sub>                | p <sub>1</sub>                | p <sub>0</sub>                |

# Modified Baugh-Wooley Multiplier

$$-a_{4} \quad a_{3} \quad a_{2} \quad a_{1} \quad a_{0}$$

$$\mathbf{x} \quad -x_{4} \quad x_{3} \quad x_{2} \quad x_{1} \quad x_{0}$$

$$+1 \quad \overline{a_{4}x_{0}} \quad a_{3}x_{0} \quad a_{2}x_{0} \quad a_{1}x_{0} \quad a_{0}x_{0}$$

$$\overline{a_{4}x_{1}} \quad a_{3}x_{1} \quad a_{2}x_{1} \quad a_{1}x_{1} \quad a_{0}x_{1}$$

$$\overline{a_{4}x_{2}} \quad a_{3}x_{2} \quad a_{2}x_{2} \quad a_{1}x_{2} \quad a_{0}x_{2}$$

$$\overline{a_{4}x_{3}} \quad a_{3}x_{3} \quad a_{2}x_{3} \quad a_{1}x_{3} \quad a_{0}x_{3}$$

$$-1 \quad a_{4}x_{4} \quad \overline{a_{3}x_{4}} \quad \overline{a_{2}x_{4}} \quad \overline{a_{1}x_{4}} \quad \overline{a_{0}x_{4}}$$

$$-\mathbf{P_{9}} \quad P_{8} \quad P_{7} \quad P_{6} \quad P_{5} \quad P_{4} \quad P_{3} \quad P_{2} \quad P_{1} \quad P_{0}$$

\_

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008, John Wiley

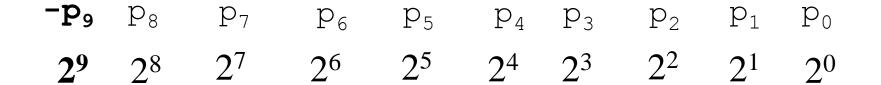

#### SD number in accumulating partial products

Two's complement number in result

| $\mathbf{p}_9$ | p <sub>8</sub> | $p_7$   | p <sub>6</sub> | $p_5$ | $p_4$   | $p_3$   | $p_2$   | $p_1$   | p <sub>0</sub> |

|----------------|----------------|---------|----------------|-------|---------|---------|---------|---------|----------------|

| -29            | 28             | $2^{7}$ | 26             | 25    | $2^{4}$ | $2^{3}$ | $2^{2}$ | $2^{1}$ | $2^{0}$        |

# Sign-bit Conversion from SD to 2's complement

| $-1$ $a_4x_4$                | 1 a <sub>4</sub> x <sub>4</sub>        | <u>1</u> a <sub>4</sub> x <sub>4</sub> |  |  |

|------------------------------|----------------------------------------|----------------------------------------|--|--|

| + C                          | + -C                                   | + C                                    |  |  |

| <b>-(1-С)</b> Р <sub>8</sub> | <b>(1-C)</b> P <sub>8</sub>            | <b>(1+C)</b> P <sub>8</sub>            |  |  |

| $-1$ $a_4x_4$                | <u>1</u> a <sub>4</sub> x <sub>4</sub> | 1 a <sub>4</sub> x <sub>4</sub>        |  |  |

| + <sub>C</sub>               | + -C                                   | + <sup>C</sup>                         |  |  |

| - <b>P</b> 9 P8              | <b>P</b> 9 P8                          | <b>P</b> <sub>9</sub> P <sub>8</sub>   |  |  |

| A: SD                        | B: 2's complement                      | C: 2's complement                      |  |  |

| <b>p</b> <sub>9</sub> =      | $p_9 = (1+C)$                          |                                        |  |  |

#### Modified Baugh-Wooley Multiplier: A

$$-a_{4} \quad a_{3} \quad a_{2} \quad a_{1} \quad a_{0}$$

$$X \quad -x_{4} \quad x_{3} \quad x_{2} \quad x_{1} \quad x_{0}$$

$$+1 \quad \overline{a_{4}x_{0}} \quad a_{3}x_{0} \quad a_{2}x_{0} \quad a_{1}x_{0} \quad a_{0}x_{0}$$

$$\overline{a_{4}x_{1}} \quad a_{3}x_{1} \quad a_{2}x_{1} \quad a_{1}x_{1} \quad a_{0}x_{1}$$

$$\overline{a_{4}x_{2}} \quad a_{3}x_{2} \quad a_{2}x_{2} \quad a_{1}x_{2} \quad a_{0}x_{2}$$

$$-1 \quad a_{4}x_{4} \quad \overline{a_{3}x_{4}} \quad \overline{a_{2}x_{4}} \quad \overline{a_{1}x_{4}} \quad \overline{a_{0}x_{4}}$$

$$-P_{9} \quad P_{8} \quad P_{7} \quad P_{6} \quad P_{5} \quad P_{4} \quad P_{3} \quad P_{2} \quad P_{1} \quad P_{0}$$

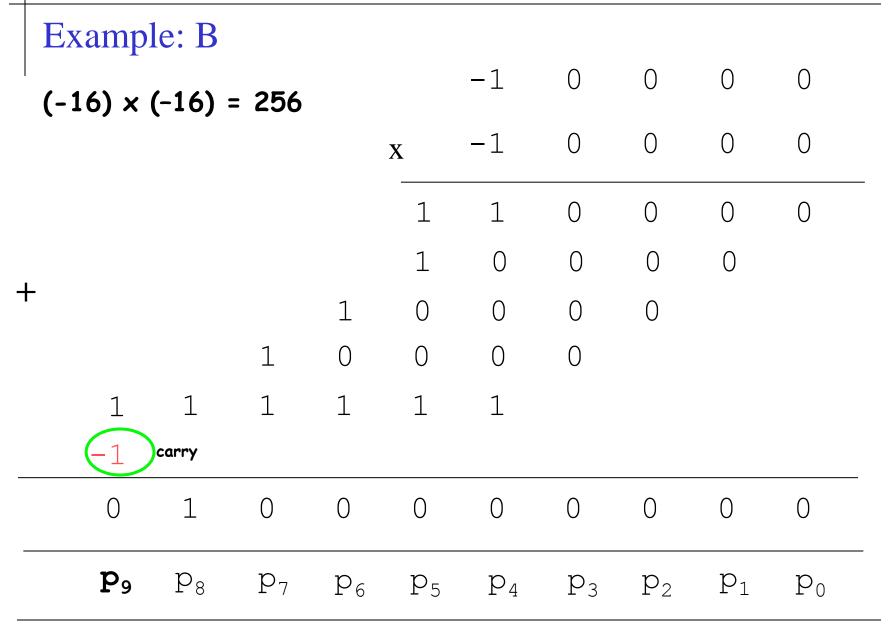

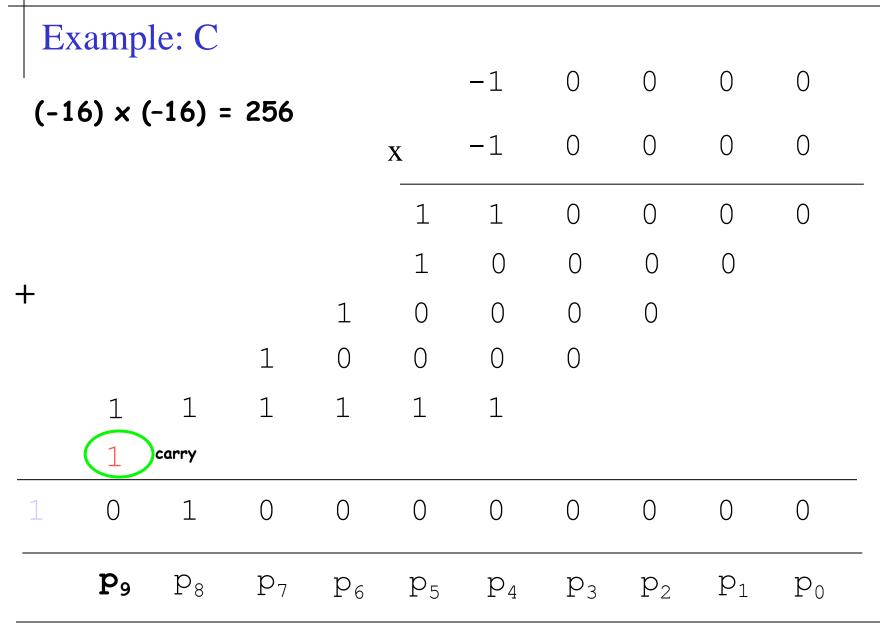

#### Example $(-16) \times (-16) = 256$ -1 Χ $\left(\right)$ ╋ -1 carry $p_8$ $-\mathbf{p}_9$ $p_7$ p<sub>6</sub> $p_5 p_4$ $p_2$ p<sub>1</sub> $p_0$ p<sub>3</sub>

#### Modified Baugh-Wooley Multiplier: B,C

$$-a_{4} \quad a_{3} \quad a_{2} \quad a_{1} \quad a_{0}$$

$$\mathbf{x} \quad -x_{4} \quad x_{3} \quad x_{2} \quad x_{1} \quad x_{0}$$

$$1 \quad \overline{a_{4}x_{0}} \quad a_{3}x_{0} \quad a_{2}x_{0} \quad a_{1}x_{0} \quad a_{0}x_{0}$$

$$\overline{a_{4}x_{1}} \quad a_{3}x_{1} \quad a_{2}x_{1} \quad a_{1}x_{1} \quad a_{0}x_{1}$$

$$\overline{a_{4}x_{2}} \quad a_{3}x_{2} \quad a_{2}x_{2} \quad a_{1}x_{2} \quad a_{0}x_{2}$$

$$1 \quad a_{4}x_{4} \quad \overline{a_{3}x_{4}} \quad \overline{a_{2}x_{4}} \quad \overline{a_{1}x_{4}} \quad \overline{a_{0}x_{4}}$$

$$P_{9} \quad P_{8} \quad P_{7} \quad P_{6} \quad P_{5} \quad P_{4} \quad P_{3} \quad P_{2} \quad P_{1} \quad P_{0}$$

# Chapter 13: Verification

#### Prof. Soo-Ik Chae

# Objectives

After completing this chapter, you will be able to:

- Describe the importance and essential of verification

- Understand the essential of timing and functional verification

- Describe the essential issues of simulators

- Understand the essential principles of test bench designs

- Understand the principle of dynamic timing analysis

- Understand the principle of static timing analysis

- Understand issues of coverage analysis

- Describe the ISE design flow and related issues

# Verification

- The goal of verification is to ensure a module 100% correct in its functionality and timing.

- On average, design teams usually spend 50 ~ 70% of their time to verify their designs.

- Functional verification only considers if the logic function of the design meets the specifications.

- simulation

- formal proof

- Timing verification considers whether the design meets the timing constraints.

- dynamic timing simulation

- static timing analysis

# **Functional Verification**

- Simulated-based functional verification

- The design is placed under a test bench.

- Input stimuli are applied to the design.

- The outputs from the design are compared with the reference outputs.

- Formal verification

- A protocol, an assertion, a property, or a design rule are proved to hold for all possible cases in the design.

# **Design Models**

- Black box model

- Only the external interfaces (namely, the input and output behavior of the design) are known.

- The internal signals and constructs are unknown (namely, black).

- Most simulation-based verifications begin with this model.

- White box model

- Both the external interfaces and internal structures are known.

- Most formal verification environments use this model.

- Gray box model

- This model is a combination of both black box and white box.

- Some of the internal signals in addition to the external interfaces are known.

- Most simulation-based verification environments use this model.

# **Assertion-Based Verification**

- Types of assertions:

- Static assertion: A static assertion is an atomic and simple check for the absence of an event.

- Temporal assertion: Several events occur in sequence and many events have to occur before the final asserted event can be checked.

# Simulation-Based Verification

- Simulation-based verification

- Test signals are applied to the DUT.

- The results are stored and analyzed.

- If the result checking and code coverage analysis meet the expected results, then we have done it.

Design specification

Functional test plan

Device under test (DUT)

Result checking

Meet the

expected results

Yes

Done

No

# Hierarchy of Functional Verification

#### Designer level (or block-level)

- Verilog HDL or VHDL is used for both design and verification.

- Unit level

- Randomized stimuli and autonomous checking are applied.

- Core level

- A well-defined process coupled with well-documented specification are applied.

- Chip level

- Ensuring that all units are properly connected and the design adheres to the interface protocols of all units.

# A Verification Test Set

#### Verification test set includes at least:

- Compliance tests

- Corner case tests

- Random tests

- Real code tests

- Regression tests

- Property check

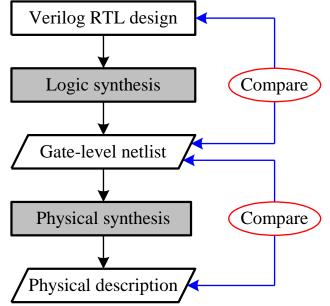

# Formal Verification

- Formal verification

- It uses mathematical techniques to prove an assertion or a property of the design.

- It proves a design property by exploring all possible ways to manipulate the design.

Verilog RTL design

- It can prove the correctness of a design without doing simulation.

# Simulations

- Types of simulations

- Behavioral simulation

- Functional simulation

- Gate-level (logic) simulation

- Switch-level simulation

- Circuit-level (transistor-level) simulation

# Variations of Simulations

#### Software simulation

- It is typically used to run Verilog HDL-based designs.

- Software simulations consume large amount of time.

#### Hardware acceleration

- It is used to speed up existing simulation.

- It can accelerate simulations by two to three orders of magnitude.

#### Hardware emulation

- It is used to verify the design in a real-world environment.

- It is used to assert the design is stable enough.

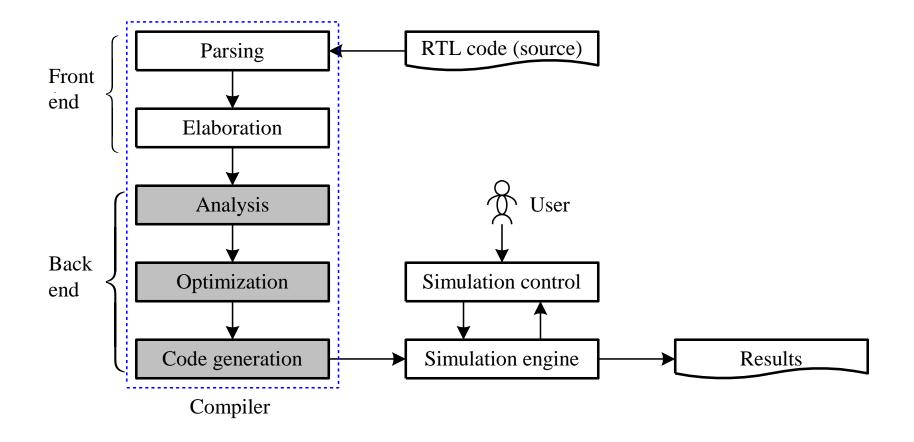

# An Architecture of HDL Simulators

# Types of Software Simulators

- Interpreted simulators

- They run the simulation interpretively.

- For example, Cadence Verilog-XL simulator.

- Compiled code simulators

- They convert the source code to an equivalent C code, then compile and run the C code.

- For example, Synopsys VCS simulator.

- Native code simulators

- They convert the source code directly to binary code for a specific machine platform.

- For example, Cadence Verilog-NC simulator.

# Software Simulators

- Event-driven simulators process elements in the design only when signals at the inputs of these elements change.

- They process all elements in the design, irrespective of changes in signals.

Cycle-based simulators work on a cycle-by-cycle basis.

- They collapse combinational logic into equations.

- They are useful for synchronous designs where operations happen only at active clock edges.

- Timing information between two clock edges is lost.

- Most cycle-based simulators are integrated with an eventdriven simulator.

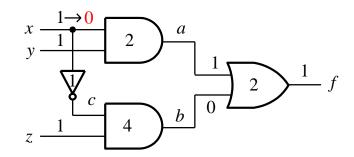

# An Event-Driven Simulation

(a) A circuit example

(b) Timing wheel

- The test bench should

- generate stimuli.

- check responses in terms of test cases,

- employ reusable verification components.

- Two types of test benches: ?

- deterministic: verify basic functions in an early stage

- self-checking: automate the tedious result checking process

- Options of choosing test vectors:

- Exhaustive test

- Random test

- Verification vector files

- Two basic choices of stimulus generation are:

- Deterministic versus random stimulus generation

- Pregenerated test case versus on-the-fly test case generation

- Types of result checking:

- on-the-fly checking

- end-of-test checking

- Result analysis:

- Waveform viewers

- Log files

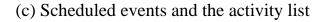

- Types of automated response checking:

- Golden vectors: known outputs

- Guidelines

- The time unit set in timescale must be matched with the actual propagation delay of gate-level circuitry.

- Set reset signal properly, especially, the time interval of the reset signal must be large enough; otherwise, the initial operation of the gate-level simulation may not work properly.

- Coding style:

- All response checking should be done automatically.

### Test Bench Designs --- A Trivial Example

```

// test bench design example 1: exhaustive test.

`timescale 1 ns / 100 ps

module nbit adder for tb;

parameter n = 4;

reg [n-1:0] x, y;

reg

c in;

wire [n-1:0] sum;

wire c out;

// Unit Under Test port map

nbit_adder_for UUT ( .x(x), .y(y), .c_in(c_in), .sum(sum), .c_out(c_out));

reg [2*n-1:0] i;

initial for (i = 0; i \leq 2^{**}(2^{*n})-1; i = i + 1) begin

x[n-1:0] = i[2*n-1:n]; y[n-1:0] = i[n-1:0]; c_in = 1'b0; #20; end

#1280 $finish;

initial

initial

monitor(\text{srealtime, "ns \%h \%h \%h \%h", x, y, c in, {c out, sum});

endmodule

```

## Test Bench Designs --- A Trivial Example

```

// test bench design example 2: Random test.

`timescale 1 ns / 100 ps

module nbit_adder_for_tb1;

parameter n = 4;

reg [n-1:0] x, y;

reg

c in;

wire [n-1:0] sum;

wire c out;

// Unit Under Test port map

nbit_adder_for UUT ( .x(x), .y(y), .c_in(c_in), .sum(sum), .c_out(c_out));

integer i;

reg [n:0] test_sum;

initial for (i = 0; i \le 2*n; i = i + 1) begin

x =  $random % 2**n; y = $random % 2**n;

c in =1'b0;

test\_sum = x + y;

#15; if (test_sum != {c_out, sum}) $display("Error iteration h(n", i);

#5;

end

initial #200 $finish;

initial $monitor($realtime, "ns %h %h %h %h", x, y, c in, {c out, sum});

endmodule

```

#### Test Bench Designs --- A Trivial Example

```

// test bench design example 3: Using Verification vector files.

`timescale 1 ns / 100 ps

module nbit_adder_for_tb2;

//Internal signals declarations:

parameter n = 4;

parameter m = 8;

reg [n-1:0] x, y;

reg

c in:

wire [n-1:0] sum;

wire c out;

// Unit Under Test port map

nbit_adder_for UUT (.x(x), .y(y), .c_in(c_in), .sum(sum), .c_out(c_out));

integer i;

reg [n-1:0] x_array [m-1:0];

reg [n-1:0] y_array [m-1:0];

reg [n:0] expected_sum_array [m-1:0];

```

#### Test Bench Designs --- A Trivial Example

| <pre>initial begin // reading verification vector files     \$readmemh("inputx.txt", x_array);     inputx.txt inputy.txt</pre> |        |     |          |      |   |    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------|------|---|----|--|--|--|--|

| <pre>\$readmemh("inputy.txt", y_array);</pre>                                                                                  |        | 4   |          | 1    |   | 05 |  |  |  |  |

| <pre>\$readmemh("sum.txt", expected_sum_array);</pre>                                                                          |        | 9   |          | 3    |   | 0c |  |  |  |  |

| end                                                                                                                            |        | d   |          | d    |   | 1a |  |  |  |  |

| initial                                                                                                                        |        | 5   |          | 2    |   | 07 |  |  |  |  |

| for $(i = 0; i \le m - 1; i = i + 1)$ begin                                                                                    |        | 1   |          | d    |   | 0e |  |  |  |  |

| $x = x_array[i]; y = y_array[i];$                                                                                              |        | 6   |          | d    |   | 13 |  |  |  |  |

| c_in =1'b0;                                                                                                                    |        | d   |          | С    |   | 19 |  |  |  |  |

| #15; if (expected_sum_array[i] != {c_out, sum})                                                                                |        | 9   |          | 6    |   | 0f |  |  |  |  |

| <pre>\$display("Error iteration %h\n", i);</pre>                                                                               |        |     |          |      |   |    |  |  |  |  |

| #5; end                                                                                                                        |        |     |          |      |   |    |  |  |  |  |

| initial                                                                                                                        |        |     |          |      |   |    |  |  |  |  |

| #200 \$finish;                                                                                                                 |        |     |          |      |   |    |  |  |  |  |

| initial                                                                                                                        |        |     |          |      |   |    |  |  |  |  |

| \$monitor(\$realtime,"ns %h %h %h %h", x, y, c_                                                                                | _in, { | c_0 | out, sum | ı}); | ) |    |  |  |  |  |

| endmodule                                                                                                                      |        |     |          |      |   |    |  |  |  |  |

## **Coverage Analysis**

- Two major types verification coverage:

- Structural coverage denotes the representation of the design to be covered.

- Functional coverage means the semantics of the design implementation to be covered.

- ✤ What does 100% functional coverage mean?

- You have covered all the coverage points you included in the simulation.

- Functional coverage let you know if you are done.

- A high coverage number is by no means an indication that the job is done.

## Structural (or code) Coverage

- Structural coverage:

- statement coverage

- branch or condition coverage: all branch sub-conditions

- toggle coverage: signals

- trigger coverage: signals in the sensitivity list of always block

- expression coverage: similar to condition coverage, but covers signal assignments instead of branch decision

- path coverage: paths

- finite-state machine coverage: state coverage and transition coverage

## **Functional Coverage**

- Functional coverage

- Item coverage

- Cross coverage

- Transition coverage

- Comments:

- The quality of coverage analysis strongly depends on how well the test bench is.

| Instance               | Design unit      | Design unit type | Stmt count | Stmt hits | Stmt misses | Stmt % | Stmt graph | Branch count |

|------------------------|------------------|------------------|------------|-----------|-------------|--------|------------|--------------|

| 🛛 🧾 /three_steps_step: | 3_tb three_steps | Module           | 35         | 5 35      | i (         | 100%   |            |              |

| 🗾 /three_steps_step:   | 3 controller     | Module           | 21         | 21        | (           | 100%   |            |              |

| 🧾 /three_steps_step(   | 3 datapath       | Module           | Ę          | 5 5       | i C         | 100%   |            | 1            |

## Why Static Timing Analysis?

Timing analysis is to estimate when the output of a given circuit gets stable.

- The purposes of timing analysis are as follows:

- Timing verification

- Verifies if a design meets a given timing constraint.

- Example: cycle-time constraint.

- Timing optimization

- Needs to identify critical portion of a design for further optimization.

- Identifies critical paths.

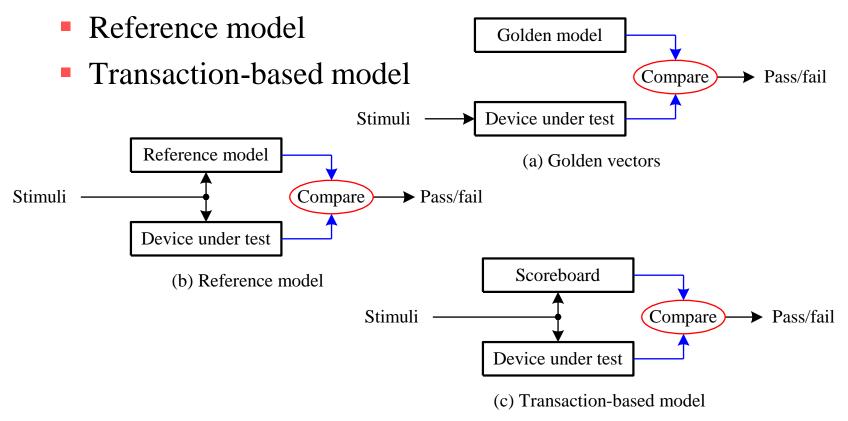

## Why Static Timing Analysis?

- The output needs to be stable by t = T for the correct functionality. But how to make sure of it?

- At least two approaches:

- Dynamic timing simulation

- Static timing analysis

- Why static timing analysis?

- Using dynamic timing simulation has posed a bottleneck for large complex designs.

- Dynamic simulation relies on the quality and coverage of the test bench used for verification.

## **Static Timing Analysis**

- Static timing analysis (STA): without having to simulate clock cycles.

- No combinational feedback loops are allowed.

- All register feedback paths are broken by the clock boundary.

- The delay of each path is calculated.

- All path delays are checked to see if timing constraints have been met.

# **Static Timing Analysis**

- Note that:

- Comprehensive sets of test benches are still needed to verify the functionality of the source RTL.

- STA is used to verify timing.

- Formal verification technique is usually used to verify the functionality of the gate-level netlist against the source RTL.

## **Static Timing Analysis**

- In STA, designs are broken into sets of signal paths, each path has a start point and an endpoint.

- Start points:

- Input ports

- Clock pins of storage elements

- Endpoints:

- Output ports

- Data input pins of storage elements

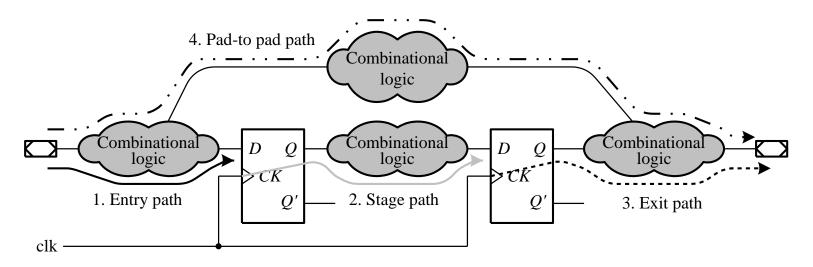

#### What to Analyze in STA

- \* Four types of path analysis:

- entry path (input-to-D path)

- stage path (register-to-register path or clock-to-D path)

- exit path (clock-to-output path)

- pad-to-pad path (port-to-port path)

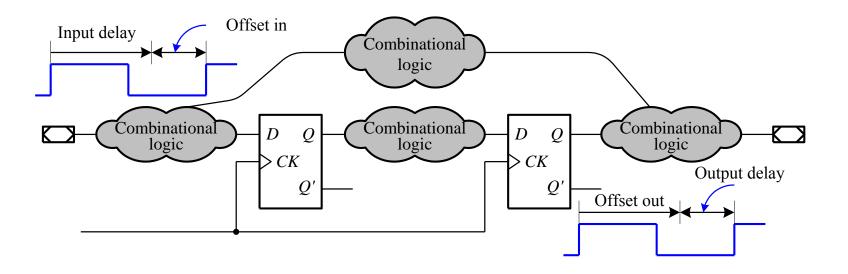

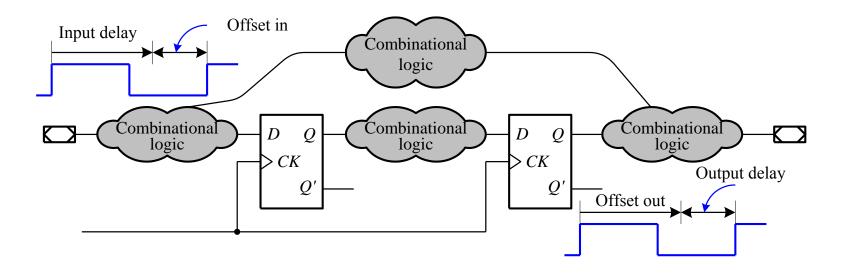

#### Timing Specifications: port-related constraints

- Input delay (offset in) constraint applies to paths from input pads to the input of a storage element.

- It specifies the arrival time of the input signal relative to the active edge of the clock.

#### Timing Specifications: port-related constraints

- Output delay (offset out) constraint applies to paths from the clock input of a storage element to output pads.

- It specifies the latest time that a signal from the output of a register may reach to output pads.

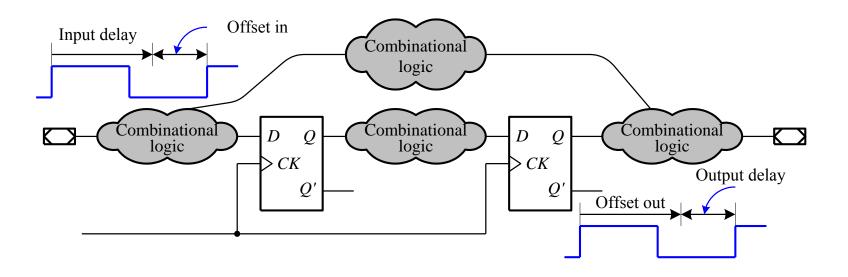

Timing Specifications: port-related constraints

Input-output (pad to pad) constraint applies to paths from input pads to output pads without passing through any register

#### Timing Specifications: clock-related constraints

- Cycle time (period) constraint applies to the paths between registers and specifies the maximum period of the clock of a synchronous circuit.

- clock jitter, clock-to-Q delay, slew rate, clock skew

- Set-up time, hold time

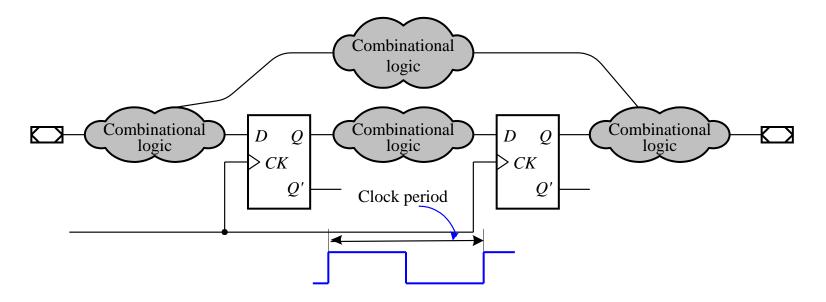

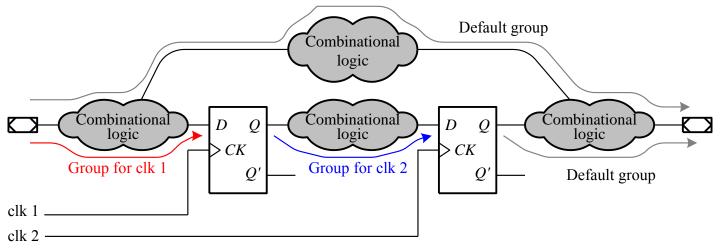

## Timing Specifications --- Path Groups

- The paths are grouped according to the clocks controlling their endpoints.

- Each clock will be associated with a set of paths called a path group.

- The default path group comprises all paths not associated with a clock.

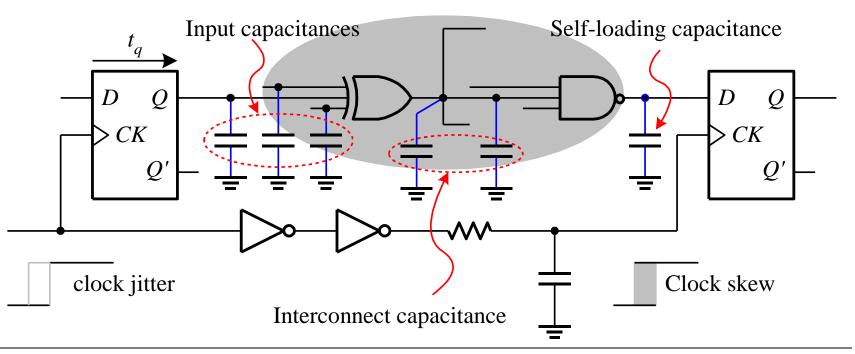

# **Factors Affecting Timing**

Factors that affect timing are:

- Clock jitter

- Clock-to-Q delay:

- Input pin capacitance

- Slew rate

- Interconnect loading

- Fan-out loading

- Clock skew

- Temperature

### Setup Time and Hold Time Checks

- Setup time: The minimum time that data must stabilize before the active clock transition.

- The maximum data path is used to determine whether setup constraint is met or not.

- Hold time: The minimum time that data must remain stable after the active clock transition.

- The minimum data path is used to determine if hold time is met.

## Critical Paths

- ✤ A critical path is the path of longest propagation delay.

- A critical path is a combinational logic path that has negative or smallest slack time, where slack time is defined as:

- slack = required time arrival time

- = requirement datapath (in ISE)

- Critical paths limit the system performance.

- Critical paths not only tell us the system cycle time, it also points out which part of the combinational logic must be changed to improve system performance.

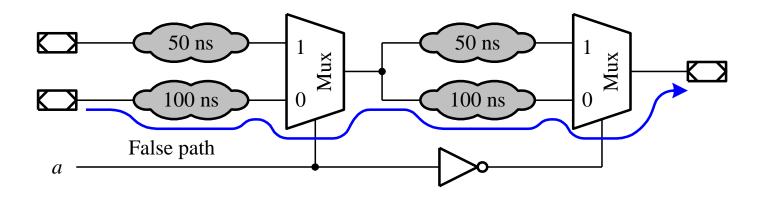

## **Timing Exceptions**

- Timing analysis tools usually treat all paths in the design as single-cycle by default and perform STA accordingly.

- Two common timing exceptions:

- False paths: A false path is identified as a timing path that does not propagate a signal.

- Multi-cycle paths: In the model, data may take more than one clock cycle to reach its destination.

#### False Paths

- False paths are paths that static timing analysis identifies as failing timing, but that the designer knows are not actually failing.

- A false path is a timing path that does not propagate a signal.

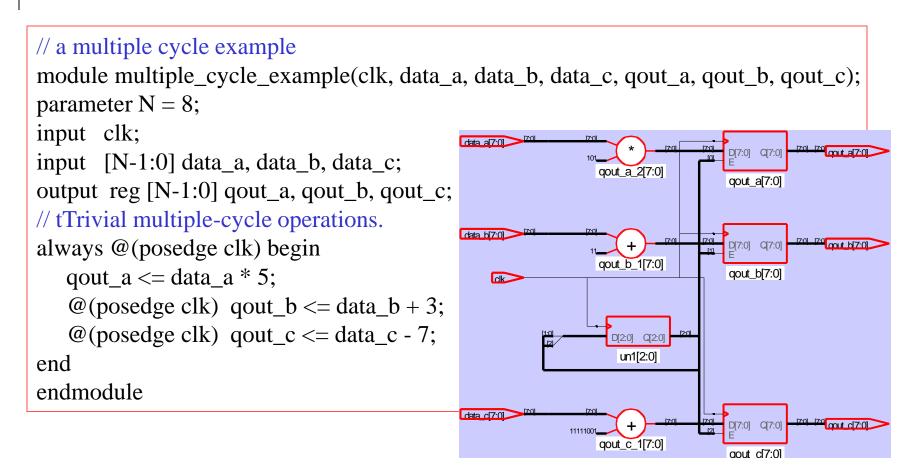

## Multi-Cycle Paths --- A Trivial Example

#### Q: Explain the operation of above code.

## Multi-Cycle Paths --- A Trivial Example

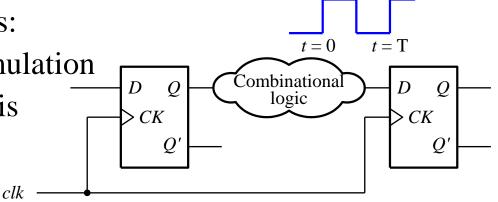

| <del>ị wave - default</del> |        |        |                          |                  |              |                    |     |                   |              |                |             |                 |        |    | _ 🗆 ×  |

|-----------------------------|--------|--------|--------------------------|------------------|--------------|--------------------|-----|-------------------|--------------|----------------|-------------|-----------------|--------|----|--------|

| <u>File Edit View</u>       | Insert | Format | <u>T</u> ools <u>W</u> i | ndow             |              |                    |     |                   |              |                |             |                 |        |    |        |

| 6883                        | §  ] ¥ | , 🖻 🕻  | 3 <b>/4</b>              | ₽ ¥ 7€           | ןֿ∙          |                    |     | 8                 | se uiju es   | <u>(</u>   196 | ų yr        | (   \$1 )       |        |    | 1 14 🕅 |

|                             | €<br>€ |        | £ 3 <b>4</b>             |                  |              |                    |     |                   |              |                |             |                 |        |    |        |

| 📄 🔷tb/clk                   | 1      |        |                          |                  |              |                    |     |                   |              |                |             |                 |        |    |        |

| ⊕>data_a                    | 13     | 3      | (23                      |                  |              | X13                |     |                   | X27          |                |             |                 | 1      |    |        |

| ⊕data_b                     | 98     | 249    | (199                     |                  |              | ),98               |     |                   | <u>(</u> 173 |                |             |                 |        |    |        |

| ⊞data_c                     |        | 87     | X67                      |                  |              | )26                |     |                   | )(54         |                |             |                 |        |    |        |

| a<br>⊕                      | 65     | 15     | (115                     |                  |              | (65                |     |                   | (135         |                |             |                 | 6      |    |        |

| qout_b                      | 101    | 252    |                          | (202             |              |                    | 101 |                   |              | (176           |             |                 |        |    |        |

| œ <b></b> ⇒qoul_c           | 60     | (80    |                          |                  | <u> (</u> 60 |                    |     | <u>)(19</u>       |              |                | <u>)</u> 47 |                 |        |    |        |

|                             |        |        |                          |                  |              |                    |     |                   |              |                |             |                 |        |    |        |

| Now                         | 50 ps  | 600000 |                          | lunuuuuu lu<br>O | 10.01.010    | duurnusru tu<br>60 | 80  | 01.001.001.0<br>] | 100          | ]              | 1           | 100000000<br>20 | Li com | 40 | diroon |

| Cursor 1                    | 75 ps  | 75 ps  |                          |                  |              |                    |     |                   |              |                |             |                 |        |    |        |

| *                           | 4 4    | $\leq$ |                          | 1                |              |                    |     | 10                |              |                |             |                 |        |    |        |

| 22 ps to 157 ps             |        |        |                          | Now: 150 p       | s Delta:     | 0                  |     |                   |              |                |             |                 |        |    | 1      |

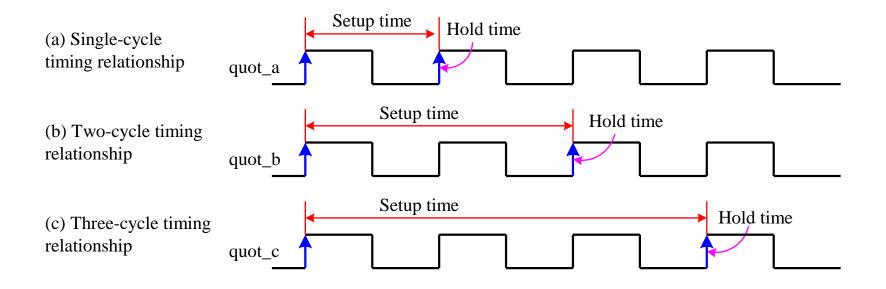

## Multi-Cycle Paths --- Timing Relationship

#### Notice that:

STA tools treat all paths in the design as a single-cycle by default and perform the STA accordingly. So you need to tell them which paths are multi-cycle paths.

## An Example of Practical Verification Process

#### Simulation

- Functional (behavioral) simulation

- Code coverage analysis

- Assertion (property) checking

- Gate-level simulation

- Dynamic timing simulation (gate-level simulation + SDF back annotation)

- Static timing analysis

- Critical paths

- Timing violations

- Prototyping

- FPGA prototyping

- Cell-based prototyping