### **Topics in IC Design**

# 7.1 Modeling of Transmission Lines

Deog-Kyoon Jeong dkjeong@snu.ac.kr School of Electrical and Computer Engineering Seoul National University 2020 Spring

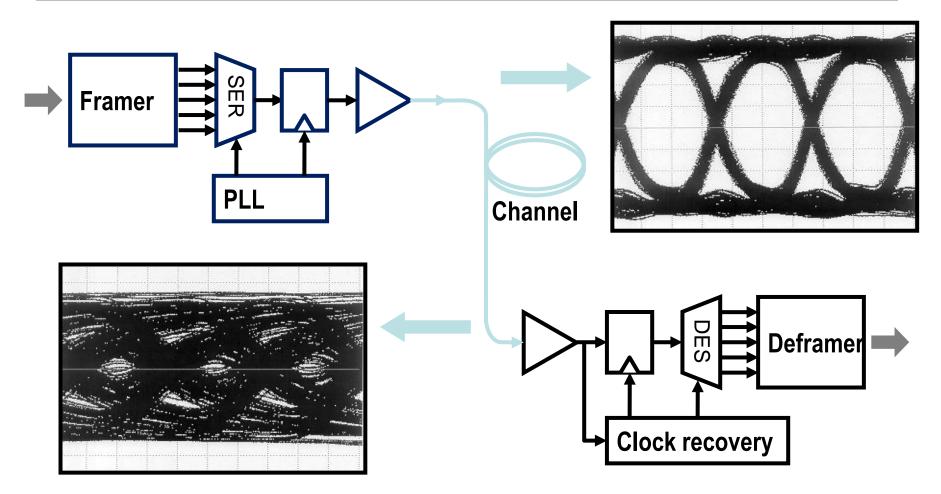

### **Serial-Link Architecture**

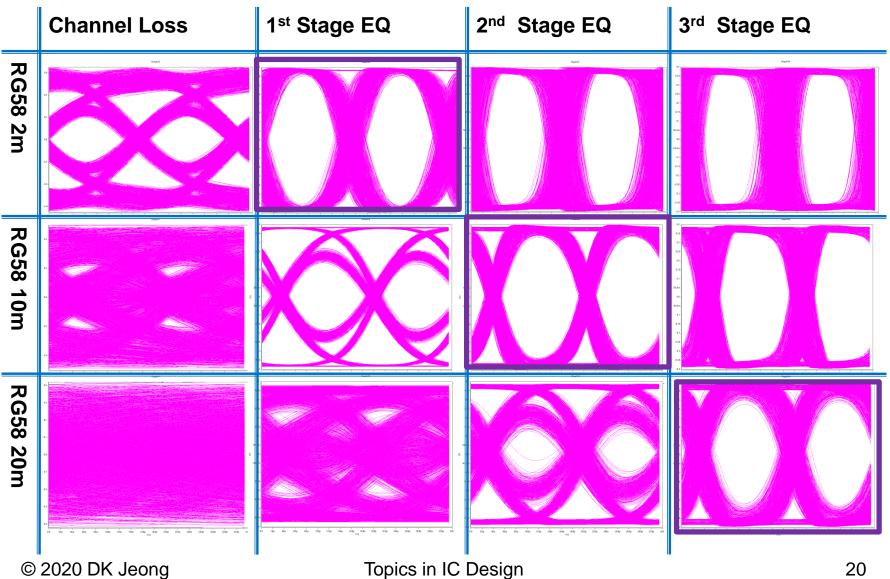

Receiver should compensate channel loss to recover transmitted signal completely!!

© 2020 DK Jeong

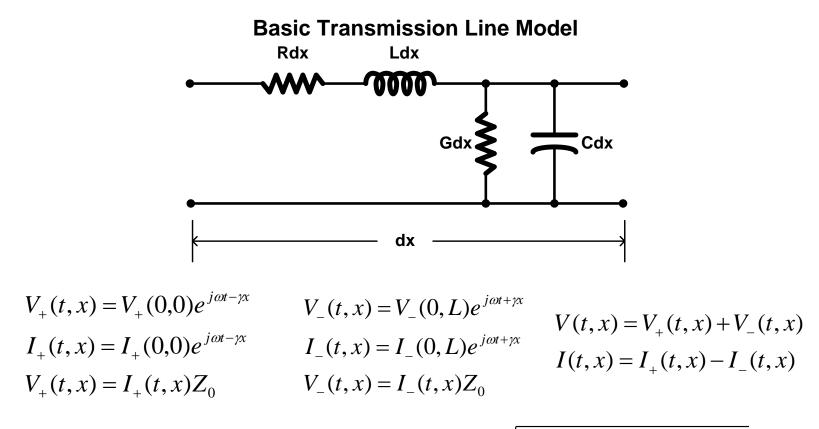

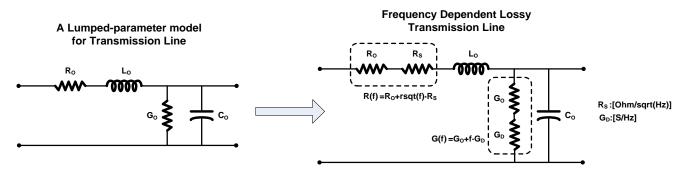

### **Distributed Parameter Channel Model**

Complex propagation constant:  $\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$

Characteristic impedance :

$$Z_o = \frac{R + j\omega L}{\gamma} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

© 2020 DK Jeong

# Skin Effect

- Skin effect is the tendency of an alternating electric current(AC) to distribute itself within a conductor so that the current density near the surface of the conductor is greater than at its core.

- The skin depth is the depth where the current has fallen off to e<sup>-1</sup>(0.381) of its original value.

- The effective series resistance of the cable corresponding to this depth increases with square root of frequency

Skin depth:

$$\delta_s = \sqrt{\frac{1}{\pi f \,\mu \sigma}}$$

Surface resistance (Sheet resistance):  $R_s = \frac{1}{\sigma \delta_s} = \sqrt{\frac{\pi f \mu}{\sigma}}$

Effective series resistance:  $R_{skin} = \frac{1}{2r} \sqrt{\frac{f \mu \rho}{\pi}}$

Skin effect frequency  $f_{skin} = \frac{\rho}{\pi \cdot \mu \cdot r^2}$  (skin depth = radius)

© 2020 DK Jeong

## **Dielectric Loss**

- With some insulating materials, dielectric absorption causes frequency dependent attenuation

- This loss can be modeled as a conductance G between the signal wire and ground.

- Dielectric loss for each material is usually expressed in terms of a parameter, called the loss tangent.

$$\epsilon = \epsilon' - j\epsilon"$$

$$\tan \delta_D = \frac{\epsilon''}{\epsilon'} = \frac{G_{AC}}{\omega C}$$

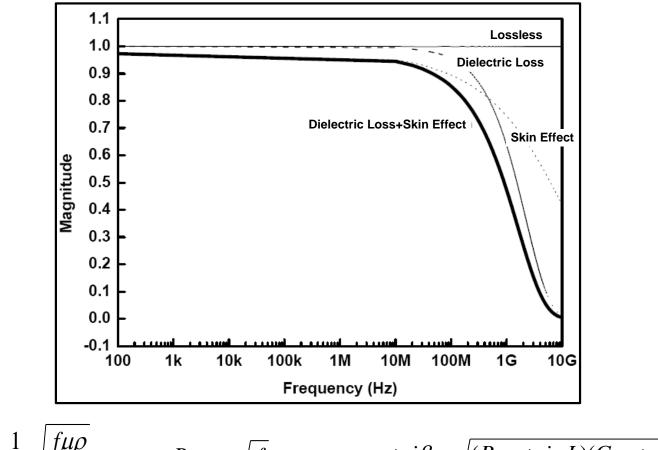

## Frequency Dependent Attenuation-Skin Effect + Dielectric Loss

$$R_{Skin} = \frac{1}{2r} \sqrt{\frac{f\mu\rho}{\pi}} \implies R_{skin} \propto \sqrt{f} \qquad \gamma = \alpha + j\beta = \sqrt{(R_{Skin} + j\omega L)(G_{AC} + j\omega C)}$$

$$G_{AC} = \omega C \tan \delta_D \implies G_{AC} \propto f \qquad \approx j\omega\sqrt{LC} + \frac{R_{Skin}}{2Z_0} + \frac{G_{AC}Z_0}{2}$$

# **Channel Transfer Function (1)**

When properly terminated, the transfer-function of a cable is modeled by

$$H(d,w) = e^{-d\gamma(\omega)} = e^{-d\alpha(\omega)}e^{-jd\beta(\omega)}$$

where propagation constant  $\gamma(\omega) = \alpha(\omega) + j\beta(\omega)$

*d* : cable length

$\alpha, \beta$ : attenuation and phase constants

• From lossy propagation constant where G=0

$$\gamma(\omega) = \sqrt{(R + j\omega L)(j\omega C)}$$

$$= j\omega\sqrt{LC}\sqrt{1 + \frac{R}{j\omega L}}$$

# **Channel Transfer Function (2)**

• When you alter the path of current, you also alter the inductance.

$$\boldsymbol{Z}_{AC} = \boldsymbol{Z}_{real} + \boldsymbol{Z}_{image}$$

- Therefore, to fully characterize skin effect, you need to consider both the changes in resistance and inductance with frequency.

- Self-inductance per length =  $\mu/8\pi$ .

- By Wheeler's assumption about the equality of the real and imaginary parts of conductor internal impedance.

$$Z_{AC} = R_{AC} (1+j) \sqrt{\omega} [\Omega/m]$$

[Wheeler H. A. "Formulas for the skin-effect", Proc. IRE, Vol. 30, 412-424, 1942

• The term (1+j) signifies the real(resistive) and imaginary(inductive) parts are equal

$$R = R_{DC} + R_{AC}(1+j)\sqrt{\omega} @ R_{DC} = \frac{\rho}{A}$$

$$R_{Skin} = \frac{1}{2r} \sqrt{\frac{f\mu\rho}{\pi}} = R_{AC} \sqrt{\omega} \qquad \therefore R_{AC} = \frac{1}{2\pi r} \sqrt{\frac{\mu\rho}{2}}$$

# **Channel Transfer Function (3)**

• If frequency is very high

$$\boldsymbol{R} \approx \boldsymbol{R}_{AC} (\mathbf{1} + \boldsymbol{j}) \sqrt{\omega}$$

$$\gamma(\omega) = j \omega \sqrt{LC} \sqrt{1 + \frac{R}{j\omega L}}$$

$$= j \omega \sqrt{LC} \sqrt{1 + \frac{R_{AC}(1 - j)}{L\sqrt{\omega}}}$$

• Using approximation  $(1+x)^{1/2} \approx 1+x/2$  for x<<1

$$\alpha(\omega) = \frac{R_{AC}}{2} \sqrt{\frac{\omega C}{L}} \text{ (same), } \beta(\omega) = \omega \sqrt{LC} + \frac{R_{AC}}{2} \sqrt{\frac{\omega C}{L}} \text{ (second term added)}$$

$$H_{dB}(d, f) = 20 \log_{10} |H(d, f)| = -8.68d \times R_{AC} \sqrt{\frac{\pi f C}{2L}}$$

$$\therefore The gain in dB \propto -\sqrt{f}$$

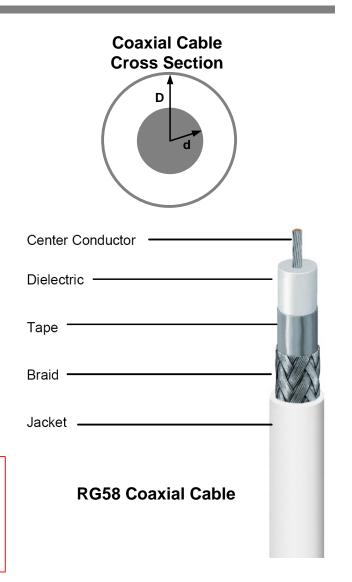

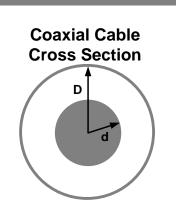

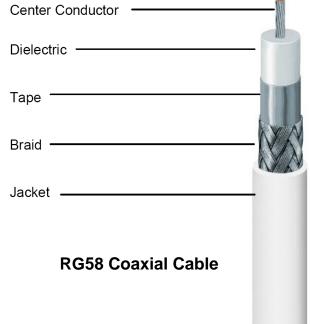

## **Coaxial Cable**

Resistance at DC

$$R = \frac{\sigma}{\pi d^2}$$

Series resistance

$$R_{Skin} = \frac{R_s}{2\pi} (\frac{1}{D} + \frac{1}{d})$$

External Series Inductance

$$L = \frac{\mu}{2\pi} \ln(D/d) = \frac{\mu_0 \mu_r}{2\pi} \ln(D/d)$$

Internal Self-Inductance at DC

$$L_{0} = \frac{\mu}{8\pi}$$

permittivity:  $\varepsilon = \varepsilon' - j\varepsilon''$

permeability:  $\mu = \mu_{0}\mu_{r}$

Surface resistance:  $R_{s} = 1/\sigma\delta_{s}$

## **Coaxial Cable**

• Shunt conductance per unit length

$G = \frac{2\pi\omega\varepsilon''}{\ln(D/d)}$

Shunt capacitance per unit length

$C = \frac{2\pi\varepsilon'}{\ln(D/d)} = \frac{2\pi\varepsilon_0\varepsilon_r}{\ln(D/d)}$

permittivity :  $\varepsilon = \varepsilon' - j\varepsilon''$ permeability :  $\mu = \mu_0 \mu_r$ Surface resistance :  $R_s = 1/\sigma \delta_s$

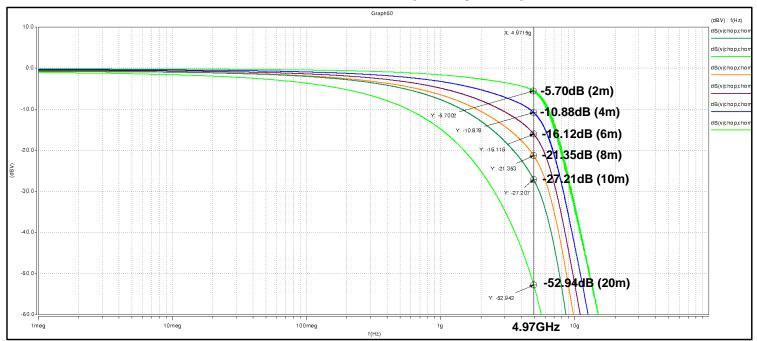

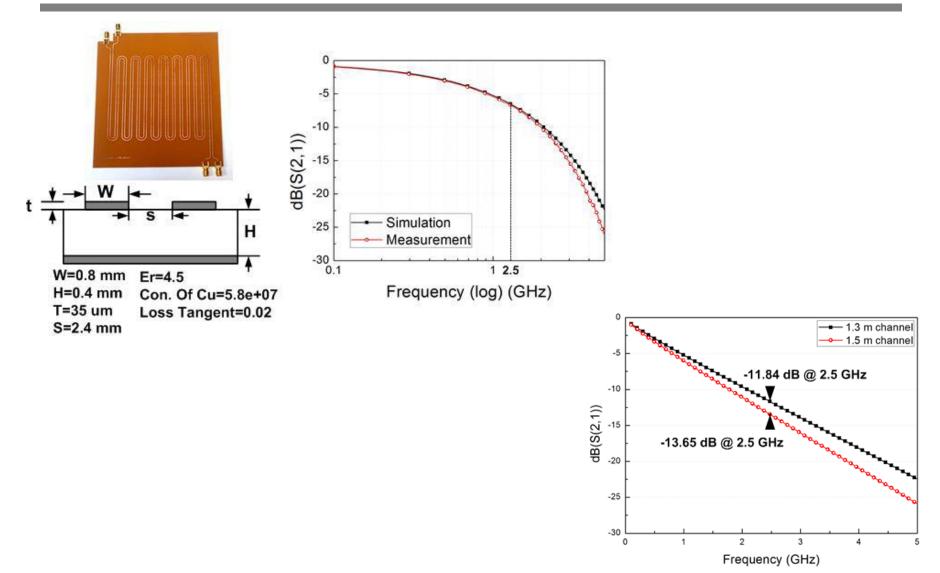

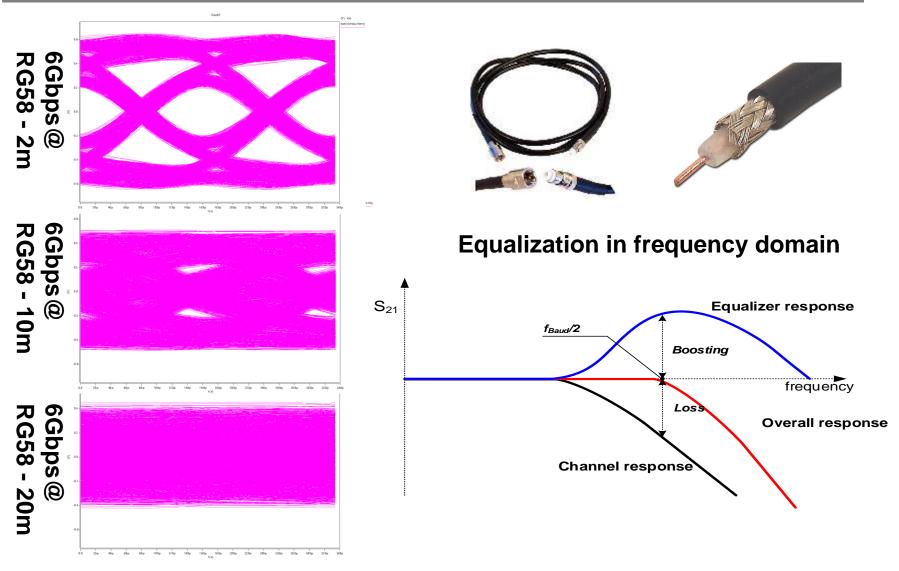

### **Channel Loss**

#### **RG58 Coaxial Cable Frequency Response**

# **Channel Group Delay**

Group Delay: A measure of the transit time of a signal through a device under test, versus frequency.

Group Delay

$$\tau_{g}(\omega) = -\frac{d\phi}{d\omega} = -\frac{1}{360} \cdot \frac{(phase_2 - phase_1)}{(f_1 - f_2)}$$

Graph49 (TDLY(V)) : f(Hz)400n vt(chop) X: 1.0442g **Group Delay** 200n vt(chop) ((V) Y J OT ) vt(chop) 0.0 86.18ns (20m) 48.26ns (10m) -200n Source Terminated: 8.18ns (2m) -6dB loss at DC -400r (dBV) : f(Hz)dB(v(chop)) X: 1.0442g dB(v(chop)) Magnitude -7.64dB (2m) -201 dB(v(chop)) (dBV) -13.67dB (10m) -40.0 -20.83dB (20m) (deg) : f(Hz) 0.0 Phase(v(chop)) X: 1.0442d Phase Phase(v(chop)) -20.0H Y: -2947.8 Phase(v(chop)) (geb) Y: -17393.0 -40.0k Y: -31049:0 -60.0k 100.0 1.0k 10.0k 100.0k 10meg 100meg 1meg 10g 1GHz f(Hz)

RG58 Coaxial Cable Frequency Response

## **Channel Loss vs Frequency**

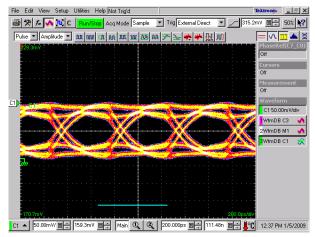

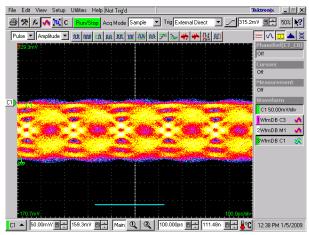

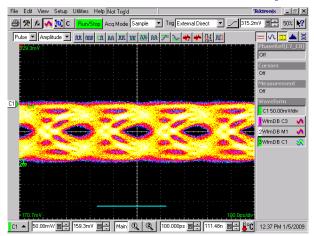

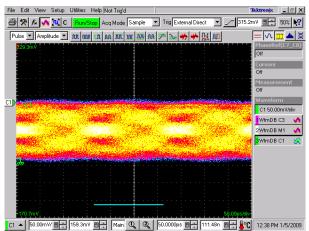

#### 12 inch PCB trace @ 2Gbps

#### 12 inch PCB trace @ 5Gbps

#### 12 inch PCB trace @ 4Gbps

#### 12 inch PCB trace @ 6Gbps

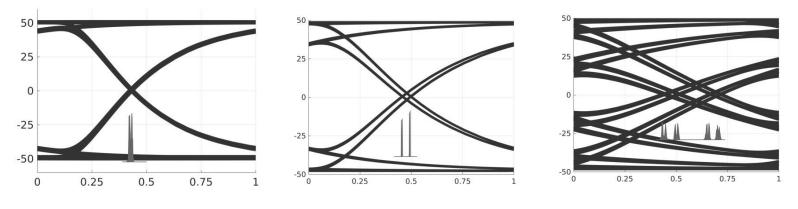

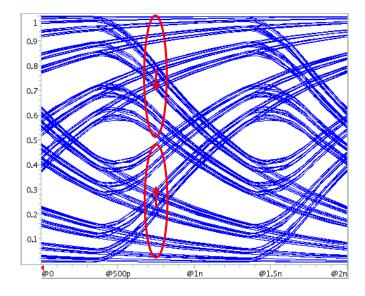

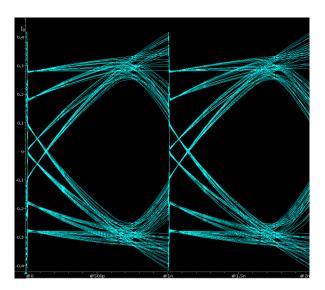

## **Data-Dependent Jitter: ISI**

Previous symbol does not settle completely

Almost no ISI, ISI spanning over 1 bit, ISI spanning over 2 bits

# Pattern Dependent Histogram

### • Data dependent jitter

- When a transition follows consecutive bits (e.g. 110)

→ edge-shift backward

- When a transition follows alternating bits (e.g. 010)

→ edge-shift forward

- Random Jitter

- Convolution with data dependent jitter

- As the channel loss increases, the eye histogram splits

### References

- Bidyut K. Sen and Richard L. Wheeler. "Skin Effects Models for Transmission Line Structures using Generic SPICE Circuit Simulators", IEEE 7<sup>th</sup> Topical Meeting on Electrical Performance of Electronic Packaging, 1998

- S Kim and D.P. Neikirk, "Compact Equivalent Circuit Model for the Skin Effect", IEEE MTT-S International Microwave Symposium Digest, 1996

- M. Tsuk, "The Internal Impedance of Conductors with Arbitrary Cross Sections", Progress in Electromagnetics Research Symposium, July 2000

- David M. Pozar, "Microwave Engineering" John Wiley & Sons, Inc. 2005

### **Backplane Example**

### **Topics in IC Design**

# 7.2 Equalizers

Deog-Kyoon Jeong dkjeong@snu.ac.kr School of Electrical and Computer Engineering Seoul National University 2015 Spring

# Outline

- Equalizer Overview

- TX Equalizer

- FIR (Finite Impulse Response) Filter

- Pre-de-emphasis

### Continuous-Time RX Equalizer

- CT Linear Equalizer (CTLE)

- Bandwidth extension techniques

### Discrete-Time Equalizer

- Feed-Forward Equalizer (FFE)

- Decision Feedback Equalizer (DFE)

- Equalizer Adaptation

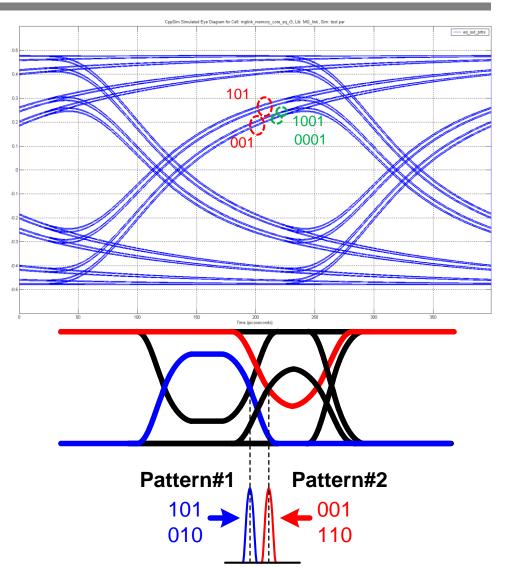

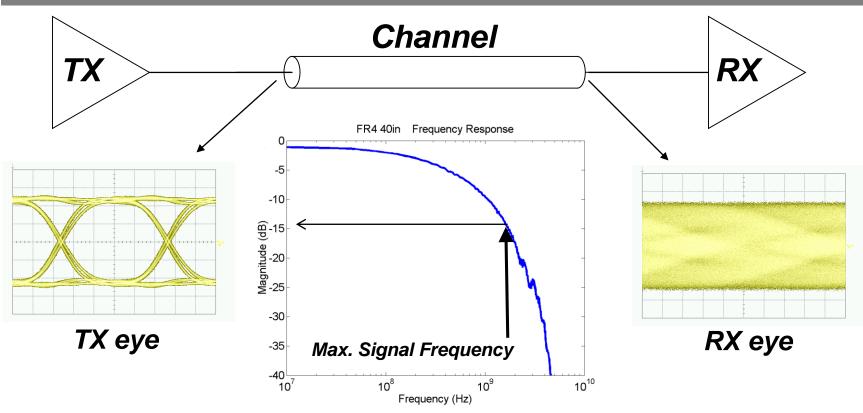

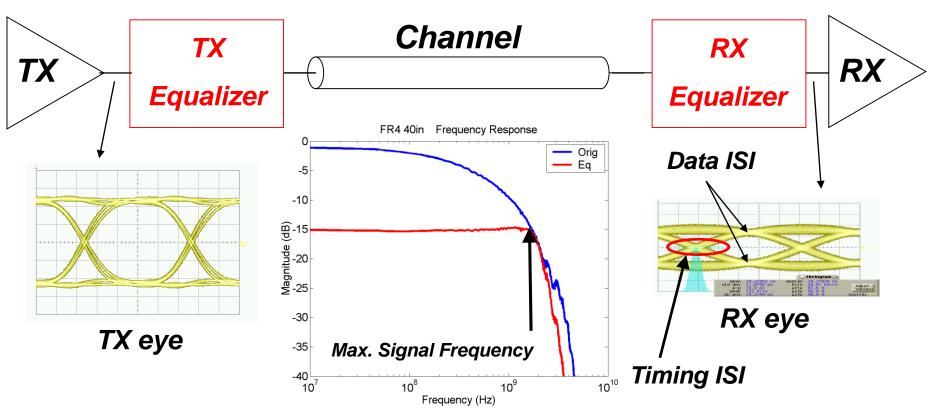

# **Channel Bandwidth and ISI**

- An I/O link = transmitter (TX) + channel + receiver (RX)

- TX,RX contributes voltage noise and timing jitter

- Limited channel bandwidth introduces inter-symbol interference (ISI)

- Bit error rate (BER) depends on voltage noise, timing jitter and ISI

[Broadcom Corp., Wong]

# **Channel Equalization**

- ITRS roadmap predicts that I/O clock rate increases 20% per year

- Channel bandwidth is not scaling at the same rate

- One of the bottlenecks of increasing I/O speed is limited channel band width.

- Channel equalization compensates ISI

© 2020 DK Jeong

Topics in IC Design

[Broadcom Corp., Wong]

# **Definitions of Equalization**

Equalization is the process of using passive or active electronic elements or digital algorithms for the purpose of <u>flattening the frequency response</u> characteristics of a system.

## **Channel Loss and Equalization**

© 2020 DK Jeong

# **Equalizer Classification**

- On-chip vs Off-chip

- On-chip: Pre-emphasis, CT-Linear, FFE, DFE

- Off-chip: Cable equalization

- TX vs RX

- TX: Pre-de-emphasis

- Rx: CT-Linear equalizer, DFE, FIR filter

- Continuous Time vs Digitally Sampled

- Analog: Linear equalizer, Continuous-time equalizer

- Digital: DFE, FIR filter

- Decision Feedback vs Feed-forward

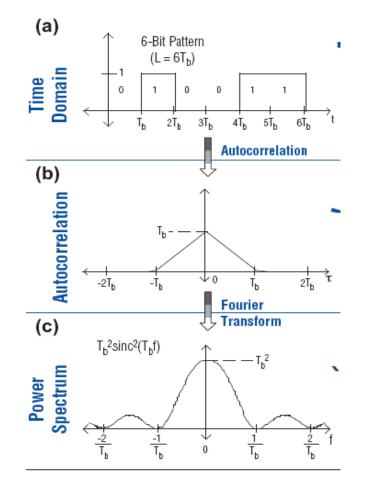

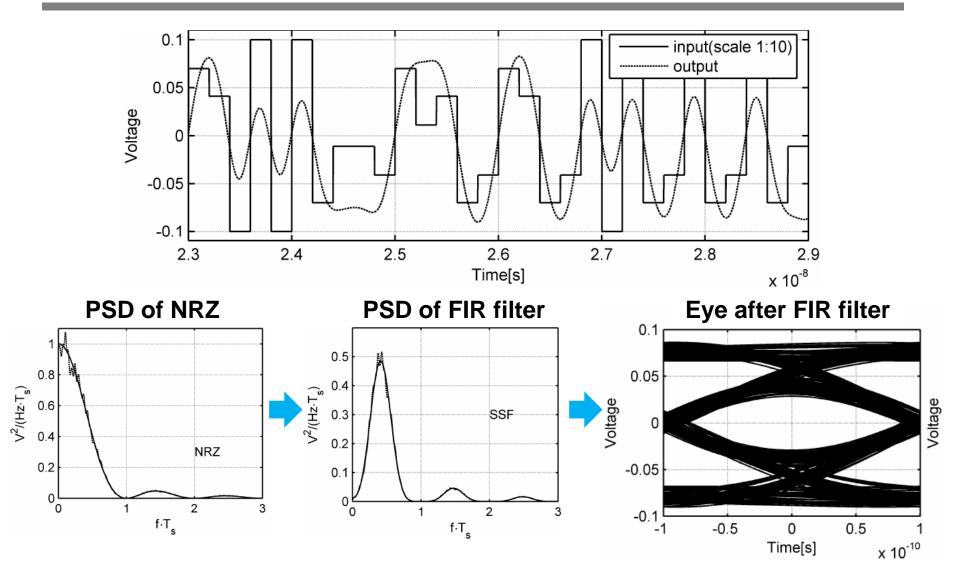

## **Power Spectral Density of NRZ**

sinc<sup>2</sup>(f)

## **PSD** after **FIR** filter

© 2020 DK Jeong

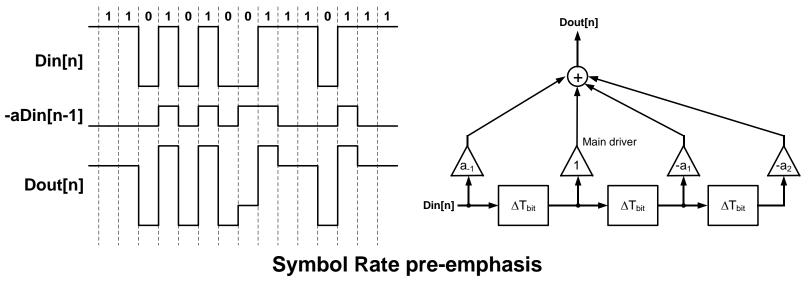

## **Pre-emphasis**

- Attenuates the low-frequency contents.

- The output swing of the Tx driver is limited.

- Be careful about the amplitude of output signal.

- Sum of all abs values of coeffs must be smaller than the allowed peak.

$Dout[n] = a_{1}Din[n+1]+Din[n]-a_{1}Din[n-1]-a_{2}Din[n-2]$

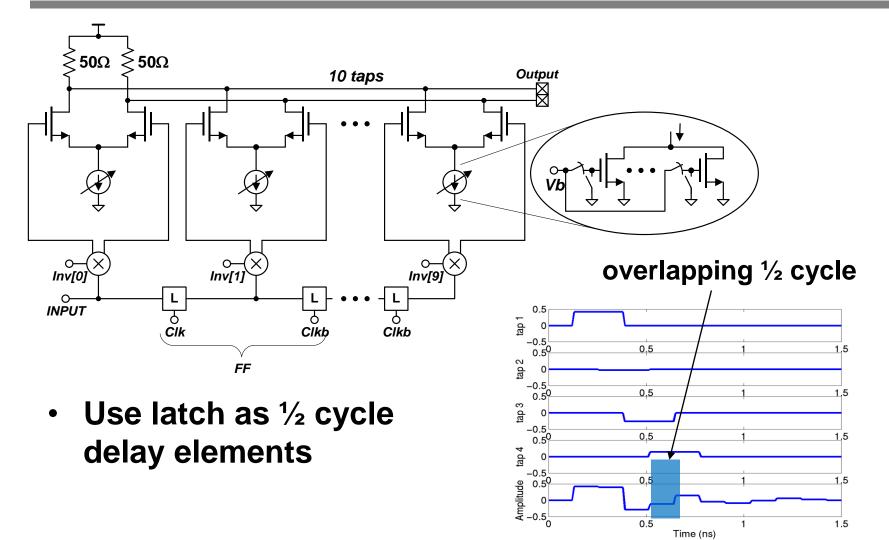

### **Pre-emphasis**

Half-symbol rate by using latch with a half-cycle delay

$Dout[n] = a_{-1}Din[n+1/2]+Din[n]-a_{1}Din[n-1/2]-a_{2}Din[n-1]$

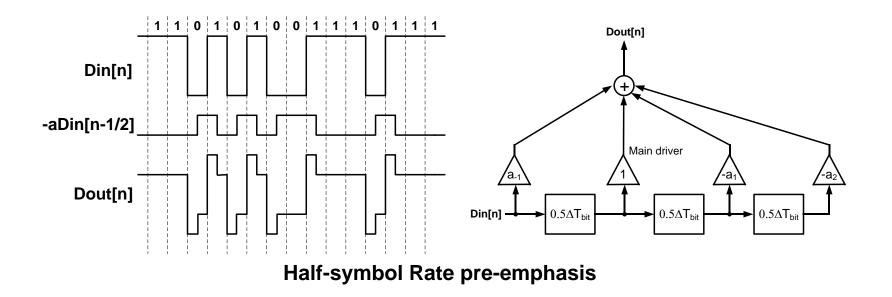

# TX Equalization Example(1)

- Delay signal by multiple of ½ cycle time

- FIR with edge equalization (XFIR)

- Trade-off between voltage and timing margin

OUT

$\alpha_N$

$\alpha_{N-}$

[JSSC'08, Wong]

# Tx Equalization Example(1)

[JSSC'08, Wong]

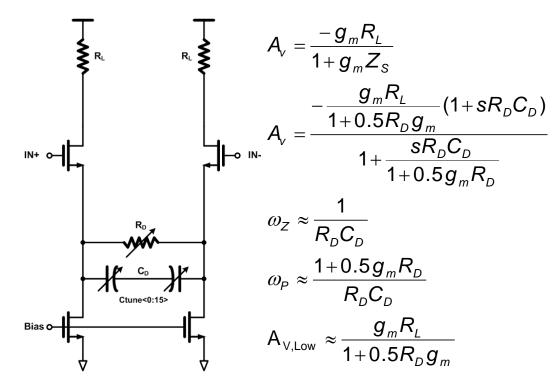

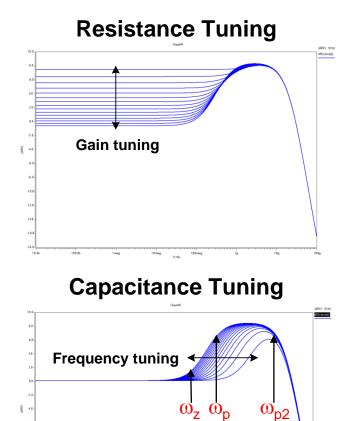

# Linear Equalizer

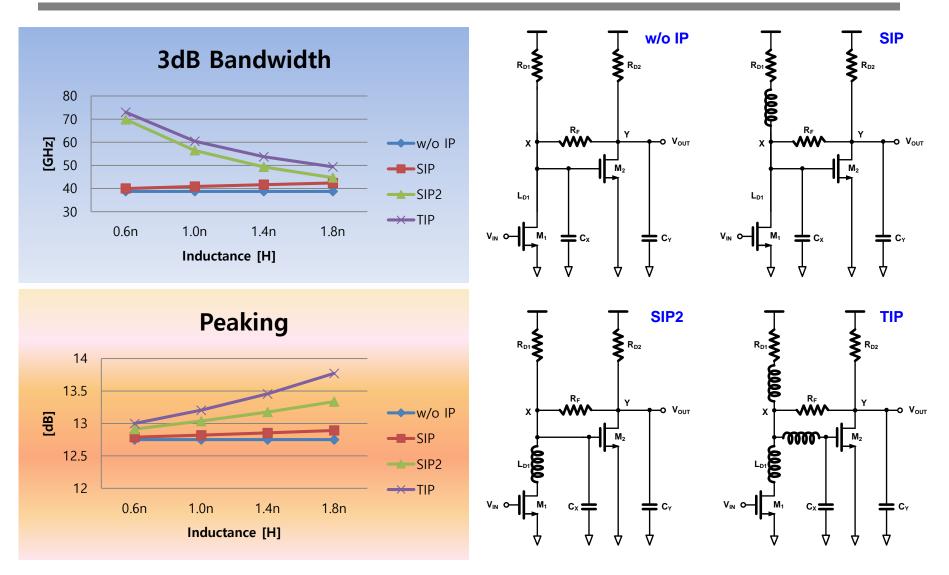

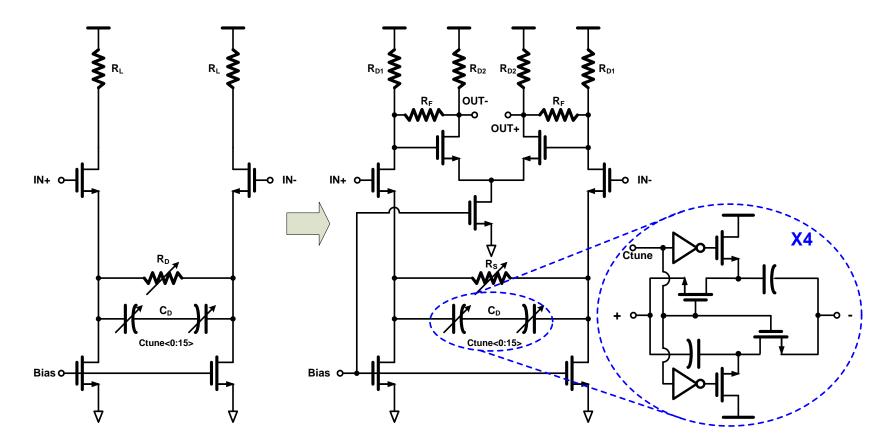

- Addition of zero to boost high frequency

- Capacitive and resistive degeneration

• Inductive Peaking  $V_{DD}$   $V_{DD}$   $V_{DD}$   $R_D$   $V_{DD}$   $R_D$   $V_{DD}$   $R_D$   $V_{DD}$   $R_D$   $V_{DD}$   $R_D$   $V_{DD}$   $V_{DD}$   $R_D$   $V_{DD}$   $V_{DD}$   $V_{DD}$   $R_D$   $V_{OUt}$   $V_{III} \rightarrow C_L$   $V_{III} \rightarrow C_L$  $V_{III} \rightarrow C_L$

$$f_{-3dB} = \frac{1}{2\pi R_D C_L} \qquad \frac{V_{out}}{V_{in}} = -g_m R_D \frac{s + 2\zeta \omega_n}{s^2 + 2\zeta \omega_n s + \omega_n^2} \frac{\omega_n}{2\zeta}$$

$$f_{-3dB} = \frac{1.79}{2\pi R_D C_L} \text{ for } \zeta = 1/\sqrt{2}$$

- Bandwidth extension by 79%

- No extra power consumption

- Area penalty

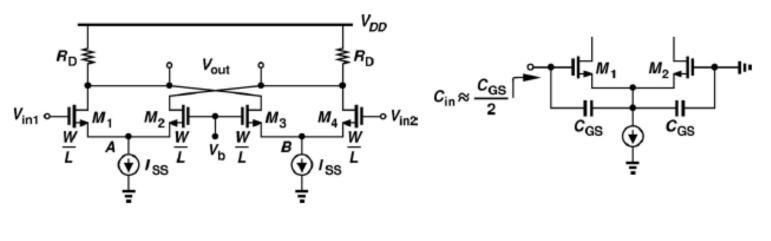

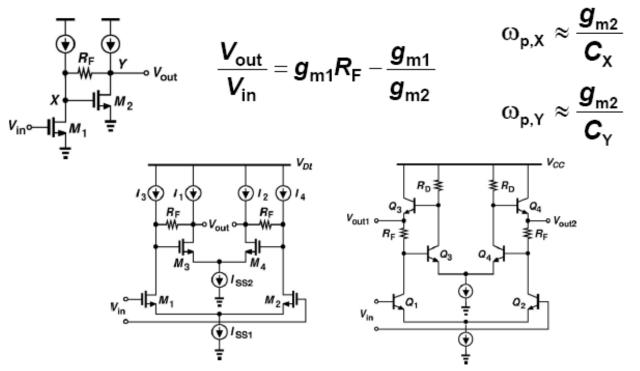

•  $f_T$  Doubler

$V_{\text{out}} = \boldsymbol{g}_{\text{m}} (V_{\text{in1}} - V_{\text{in2}}) \boldsymbol{R}_{\text{D}}$

- Bandwidth Extension

- Decrease the effective input capacitance

- Parasitics on tail current sources degrade the performance

Cherry Hooper Amplifier

- Bandwidth Extended

- Reduced voltage headroom

© 2020 DK Jeong

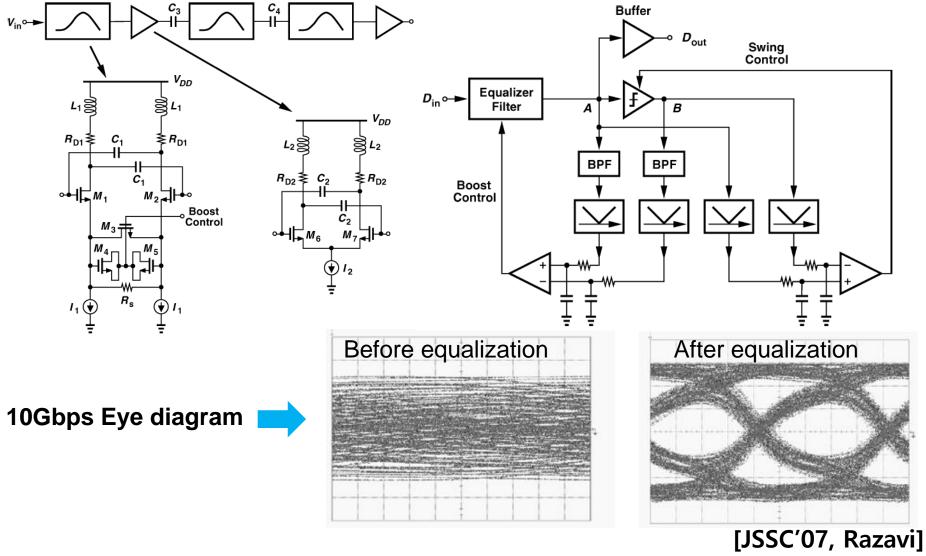

### Linear Equalizer Examples(1)

30% Bandwidth increase

### Linear Equalizer Examples(1)

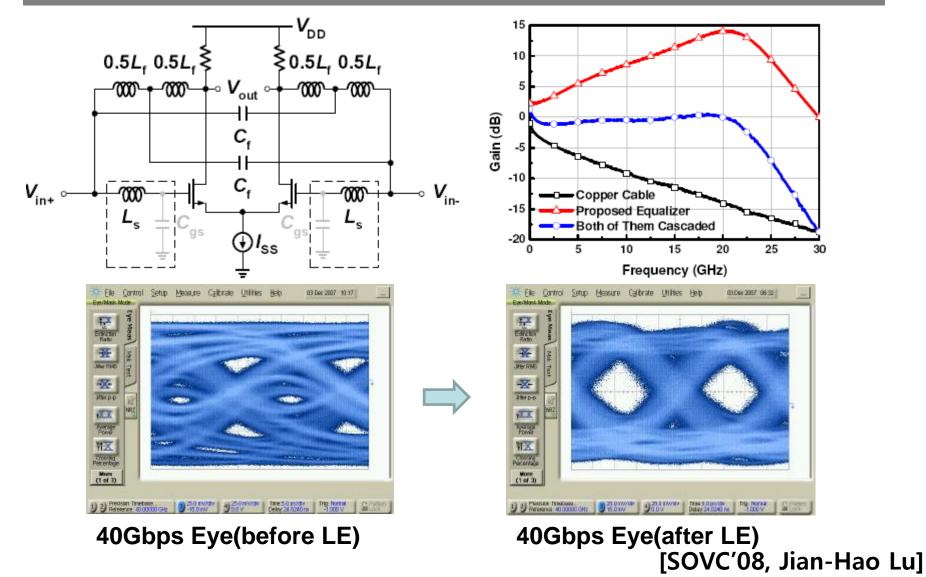

### Linear Equalizer Examples(2)

© 2020 DK Jeong

**Topics in IC Design**

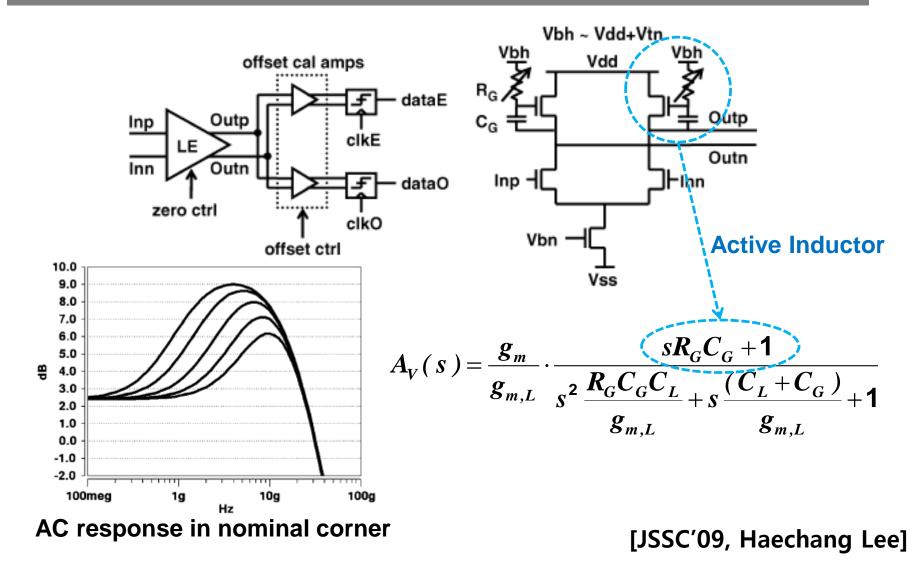

### Linear Equalizer Examples(3)

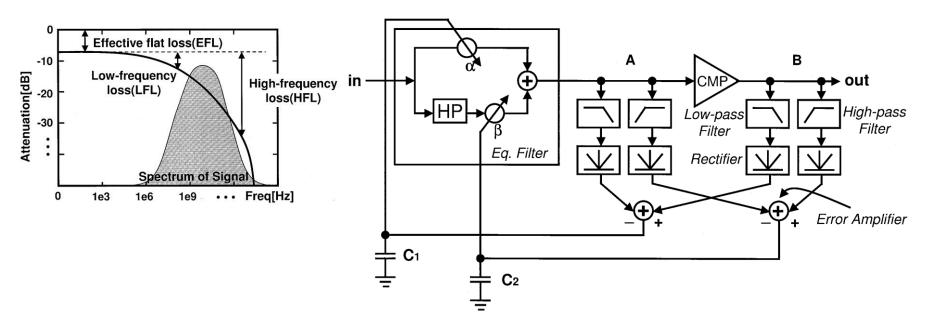

### Linear Equalizer Examples(4)

© 2020 DK Jeong

### **Continuous-Time Equalizer**

- Advantages and Disadvantages

- No dependency with the timing recovery

- Speed is limited by the equalizing filter

- Tradeoff between adaptation accuracy and operating frequency

[JSSC'04, Choi]

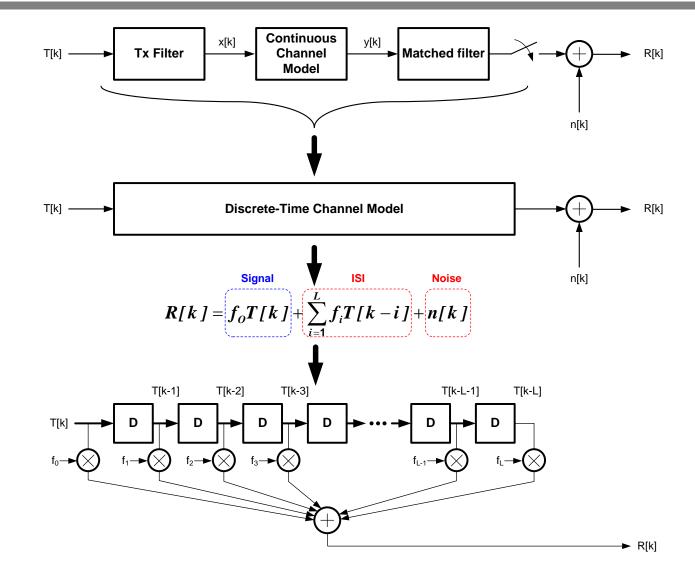

### **Discrete-time Channel Modeling**

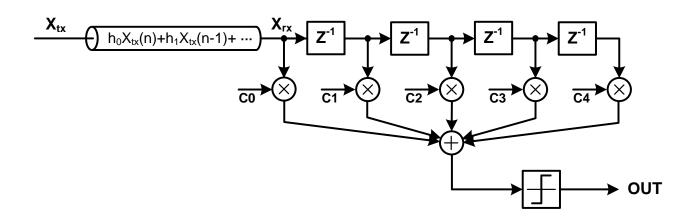

### **Feed-Forward Equalizer**

- AD conversion required

- Relaxed timing constraints

- Timing constraint easy to meet

- No time-critical feedback path

- Boosts high-freq. noise as well

- High power consumption

- ADC and digital blocks

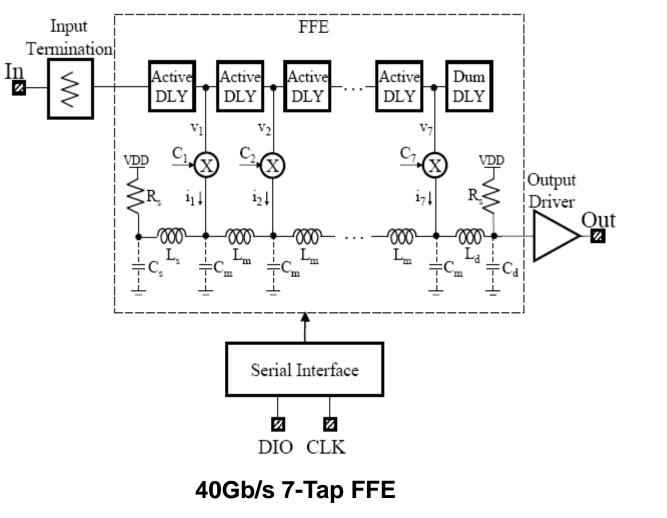

## FFE Examples(1)

FFE

[ISSCC'09, A. Momtaz]

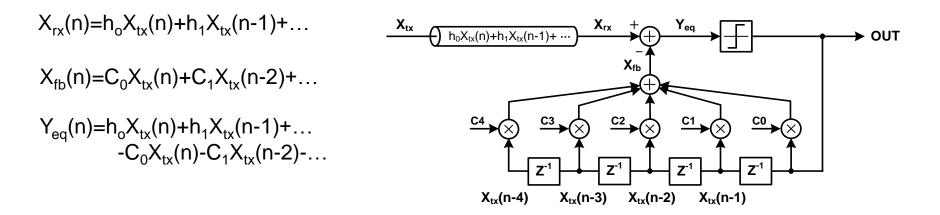

### **Decision Feedback Equalizer**

- Superior performance but timing constraints

- Hard to design DFE

- Only post-cursor cancelled

- Linear equalizer can equalize both pre- and post-cursors

If  $C_0=0 \& C_1=h_1 \& C_2=h_2 \& ..., then Y_{eq}(n)=h_o X_{tx}(n)$ - All ISI due to post-cursors cancelled.

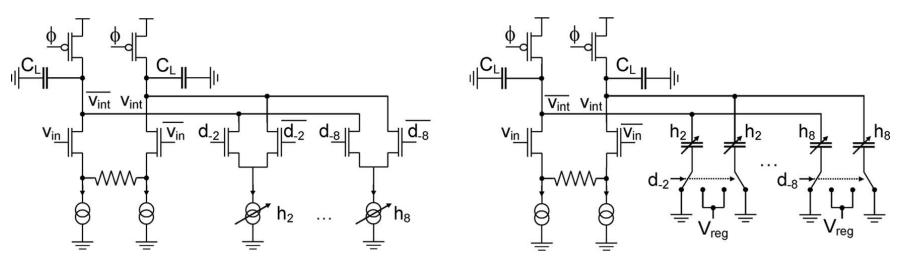

### **Summer Implementation**

- Current summer or Capacitor switching

- In front of a sampler

- Resettable PMOS load can replace load resistor

- Summer must settle within a certain level of accuracy for ISI cancellation

- Trade-off between summer output swing and settling time

- Can result in large bias current for input and taps

[JSSC'12, Thomas Toifl]

### **Summing Sampler Implementation**

- Summer merged at sampler

- Both current and capacitance switching can be used

- Latency reduced

- Speed limited by increased summation node capacitance

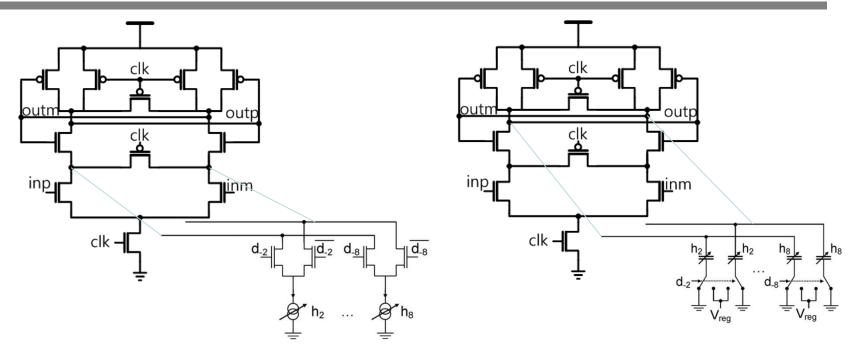

### **DFE Implementation**

**Direct Feedback**

- Direct feedback

- Simple architecture

- Critical path delay should be less than 1UI

- Loop unrolling

- Relaxes time constraints

- Reduces the loading at the summing node

- Increase complexity

## Loop Unrolling (Speculation)

Half-rate 2-tap DFE Architecture

# **Reduction of Critical Path Delay**

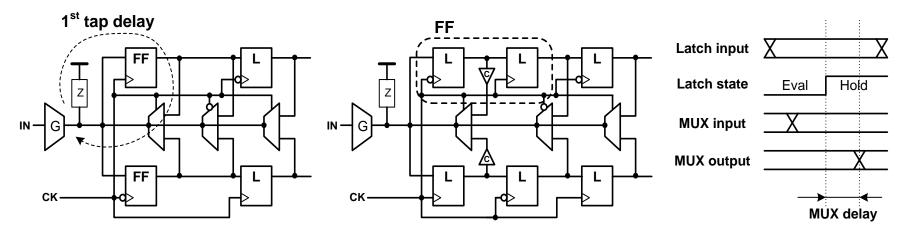

**Flip-Flop Topology**

Latch Topology('09 JSSC Pozzoni)

- Flip-Flop Topology

- The 1<sup>st</sup> tap feedback delay consists of FF and MUX delay.

- Latch-Based Topology

- MUX incorporates the function of the 2<sup>nd</sup> latch in a FF.

- The propagation delay to be limited to the MUX delay.

[JSSC'09, Pozzoni]

### References

- Sameh Abrahim and Behzad Razavi, "A 20-Gbps Serial Link for High-Loss Channels" UCLA

- MAXIM, "Spectral Content of NRZ Test Patterns"

- Koon-Lun Jackie Wong, E-Hung Chen, and Chih-Kong Ken Yang, "Edge and Data Adapti ve Equalization of Serial-Link Transceivers" IEEE, JSSC Sep. 2008

- Haechang Lee, "A 16 Gb/s/Link, 64 GB/s Bidirectional Asymmetric Memory Interface" IEEE, JSSC April 2009

- Massimo Pozzoni, "A Multi-Standard 1.5 to 10 Gb/s Latch-Based 3-Tap DFE Receiver With a SSC Tolerant CDR for Serial Backplane Communication" IEEE, JSSC Apr. 2009

- Srikanth Gondi and Behzad Razavi, "Equalization and Clock and Data Recovery Techniques for 10-Gb/s CMOS Serial-Link Receivers", IEEE JSSC Sept. 2007

- Jian-Hao Lu "A 40Gb/s Low-Power Analog Equalizer in 0.13um CMOS Technology", IEEE SOVC 2008

- A. Momtaz "An 80mW 40Gb/s 7-Tap T/2-Spaced FFE in 65nm CMOS", IEEE ISSCC 2009

### **Topics in IC Design**

# 7.3 DFE (by example)

Deog-Kyoon Jeong dkjeong@snu.ac.kr School of Electrical and Computer Engineering Seoul National University 2020 Fall

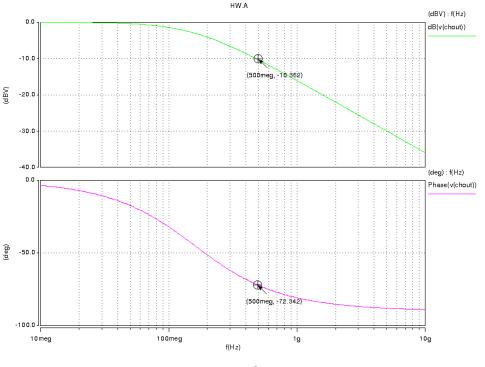

### **Example Channel**

- Channel characteristics

- 1<sup>st</sup>-order RC channel (R=50  $\Omega$ , C = 20pF)

- At the transmission rate of 1 Gbps

- Attenuation at Nyquist Frequency =  $1/\sqrt{(1+\pi^2)}$  = -10.352 dB

- Phase delay at Nyquist Frequency = -72.3°

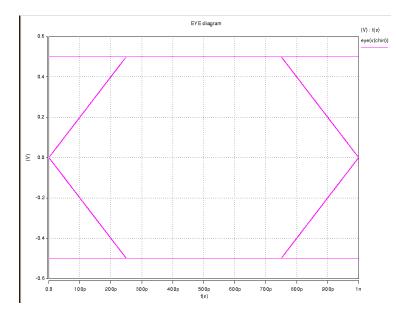

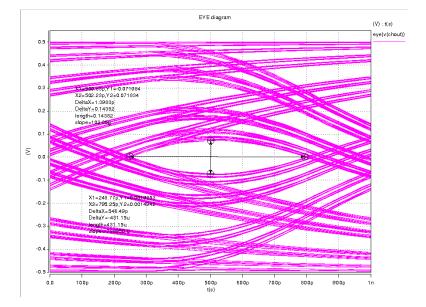

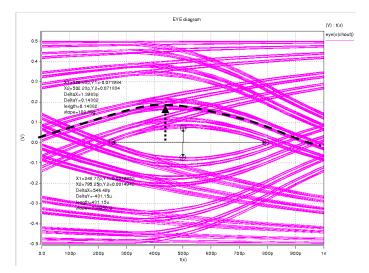

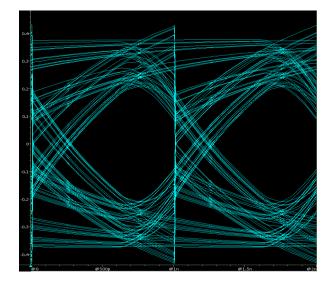

### **TX and RX Eye Diagrams**

PRBS-7 NRZ

Height: 1 V Time width: 1 ns

Height: 0.143 V Time width: 546 ps

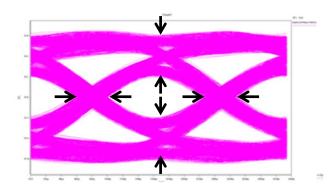

### **Eye Diagram and Channel Loss**

- Loss at the Nyquist frequency.

- The 1010 pattern contains the Nyquist frequency

- Swing of this pattern indicates the attenuation

- See the dotted line and arrow in the picture above.

20log(0.17/0.5)= -9.4dB (-10.35dB)

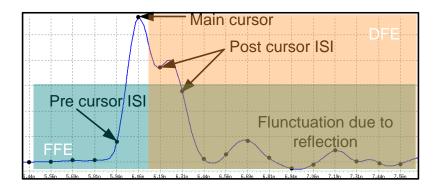

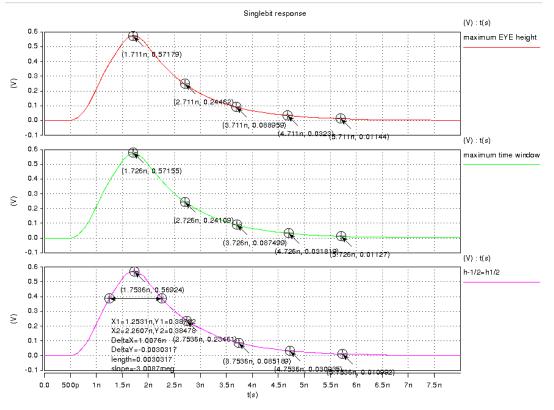

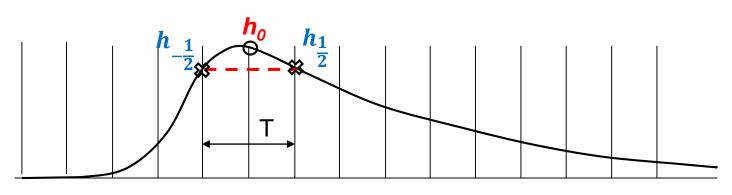

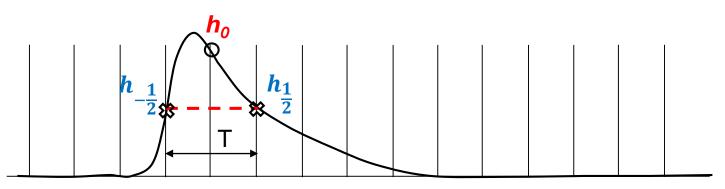

### Single Bit Response

A. h<sub>0</sub> at maximum height

B. h<sub>0</sub> at maximum width

#### C. $h_0$ at mid-point between two points of $h_{1/2} = h_{-1/2}$

© 2020 DK Jeong

Topics in IC Design

### Single Bit Response

#### A. h<sub>0</sub> at maximum height

B. h<sub>0</sub> at maximum width

#### C. $h_0$ at mid-point between two points of $h_{1/2} = h_{-1/2}$

| CASE                                   | h <sub>o</sub> | h <sub>1</sub> | h <sub>2</sub> | h <sub>3</sub> | h <sub>4</sub> |

|----------------------------------------|----------------|----------------|----------------|----------------|----------------|

| A. Maximum height                      | 0.5718         | 0.2446         | 0.0889         | 0.0323         | 0.0114         |

| B. Maximum time width                  | 0.5716         | 0.2411         | 0.0875         | 0.0318         | 0.0113         |

| C. h <sub>1/2</sub> =h <sub>-1/2</sub> | 0.5692         | 0.2346         | 0.0852         | 0.0309         | 0.0110         |

- Precursor  $h_{-1} \approx 0.05$

- Sum of all coefficients = 0.949, 0.9433, 0.9309 + precursor  $\approx$  1

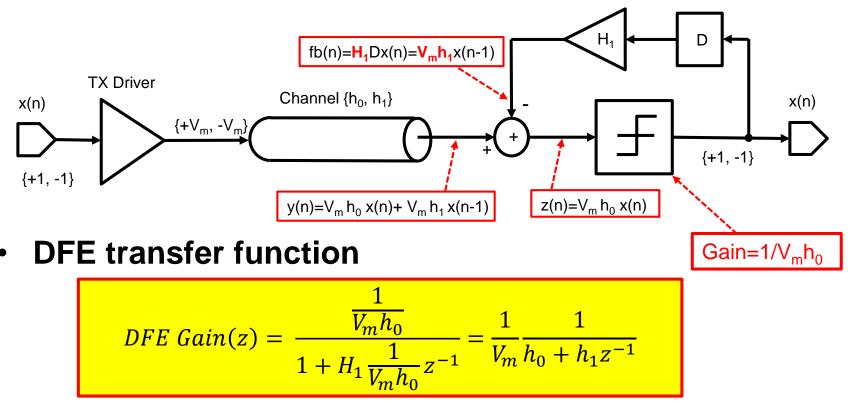

### **DFE Architecture**

#### • 1-tap DFE

- H<sub>1</sub> = V<sub>m</sub><sup>\*</sup> (h<sub>1</sub> of SBR) = V<sub>m</sub><sup>\*</sup>0.2446 (= 0.1223 if V<sub>m</sub> = 0.5V)

Other post-cursors not cancelled

### **Maximum Boost of 1-tap DFE**

$$DFE Gain(\omega) = \frac{1}{V_m} \frac{1}{|h_0 + h_1 e^{-j\omega T}|} \\ = \frac{1}{V_m} \frac{1}{\sqrt{h_0^2 + 2h_0 h_1 \cos(\omega T) + h_1^2}}$$

- DFE Gain at DC =  $1/(h_0+h_1)/V_m = 2.450 = 7.78$ dB (with  $V_m = 0.5V$ )

- DFE Gain at Nyquist =  $1/(h_0-h_1)/V_m = 6.112 = 15.72dB$ (with  $V_m = 0.5V$ )

- DFE Max Boost

- $= (h_0+h_1)/(h_0-h_1) = (0.5718+0.2446)/(0.5718-0.2446)$

- = 2.496 = 7.94dB

- Channel DC Gain with all postcursors =  $V_m = 0.5V$

- Overall DC gain = 0.5\*2.450=1.225=1.76dB (≠ 1, due to no 2<sup>nd</sup> or higher-order postcursor cancellation)

- Overall gain at Nyquist = -10.53dB+7.94dB =-2.59dB

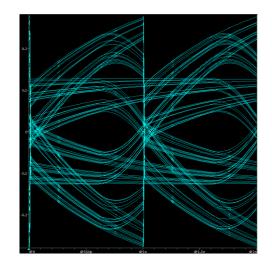

### Eye Diagram with 1-tap DFE

• With feedback delay of 0.25ns

### What if input amplitude changed?

- Input amplitude (V<sub>m</sub>) is increased from 1.0V to 0.5V, while DFE tap coefficient (V<sub>m</sub>\*h<sub>1</sub>) is fixed.

- Tap coeff is reduced by half in effect.

- Need to change tap coeffs depending on the input amplitude!

### 4-Tap DFE

**DFE Gain**(

$$\omega$$

) =  $\frac{1}{V_m} \frac{1}{|h_0 + h_1 e^{-j\omega T} + h_2 e^{-j2\omega T} + h_3 e^{-j3\omega T} + h_4 e^{-j4\omega T}|}$

- DFE Gain at DC =  $1/(h_0+h_1+h_2+h_3+h_4)/V_m = 2.107=6.47$ dB (with  $V_m=0.5V$ )

- DFE Gain at Nyquist = 5.061 = 14.08dB (with V<sub>m</sub>=0.5V)

- DFE Max Boost

= 14.08dB - 6.47dB = 7.61dB

- Channel DC Gain with all postcursors =  $V_m = 0.5V$

- Overall DC gain = 0.5\*2.107=1.054=0.45dB (≠ 1, due to no 2<sup>nd</sup> or higher-order postcursor cancellation)

- Overall gain at Nyquist = -10.53dB+7.61dB =-2.92dB

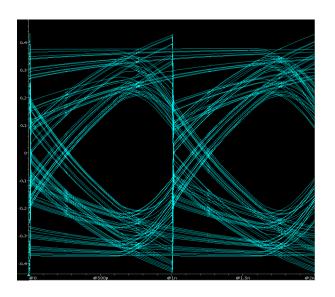

### Eye Diagram with 4-tap DFE

- With feedback delay of 0.25ns

- Almost all the post-cursors removed

- Remaining ISI due to precursors

### References

- Sameh Abrahim and Behzad Razavi, "A 20-Gbps Serial Link for High-Loss Channels" UCLA

- MAXIM, "Spectral Content of NRZ Test Patterns"

- Koon-Lun Jackie Wong, E-Hung Chen, and Chih-Kong Ken Yang, "Edge and Data Adapti ve Equalization of Serial-Link Transceivers" IEEE, JSSC Sep. 2008

- Haechang Lee, "A 16 Gb/s/Link, 64 GB/s Bidirectional Asymmetric Memory Interface" IEEE, JSSC April 2009

- Massimo Pozzoni, "A Multi-Standard 1.5 to 10 Gb/s Latch-Based 3-Tap DFE Receiver With a SSC Tolerant CDR for Serial Backplane Communication" IEEE, JSSC Apr. 2009

- Srikanth Gondi and Behzad Razavi, "Equalization and Clock and Data Recovery Techniques for 10-Gb/s CMOS Serial-Link Receivers", IEEE JSSC Sept. 2007

- Jian-Hao Lu "A 40Gb/s Low-Power Analog Equalizer in 0.13um CMOS Technology", IEEE SOVC 2008

- A. Momtaz "An 80mW 40Gb/s 7-Tap T/2-Spaced FFE in 65nm CMOS", IEEE ISSCC 2009

### **Topics in IC Design**

# 7.4 Adaptive DFE and Timing Recovery

Deog-Kyoon Jeong dkjeong@snu.ac.kr School of Electrical and Computer Engineering Seoul National University 2020 Fall

### **Equalizer Adaptation**

- Adaptive Equalization

- Compensate changes in the transmission channel characteristics

- Compensate manufacturing variation

- Suitable for multi-standard

- Can be applied to any equalizers; FFE, CTLE, and DFE

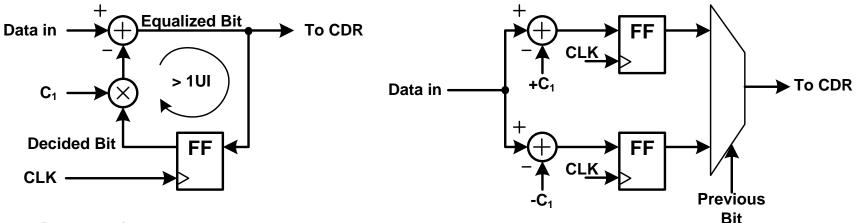

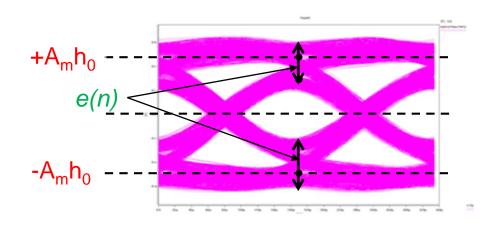

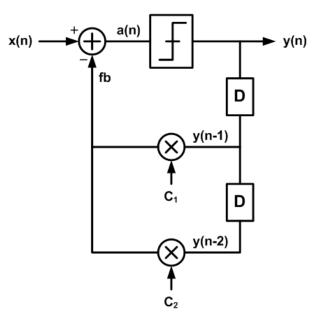

### **DFE Adaptation**

LMS algorithm

$$fb = \sum_{k=1}^{2} C_k y(n-k)$$

$$e(n) = y(n) - a(n)$$

$$a(n) = x(n) - \sum_{k=1}^{2} C_k y(n-k)$$

With LMS updating equation  $C_k(n+1) = C_k(n) + \mu e(n)y(n-k)$

Or use sign-sign adaptation

### How to set A<sub>m</sub>h<sub>0</sub>?

- Must know a priori or

- Adapt so that E[e(n)] = 0.

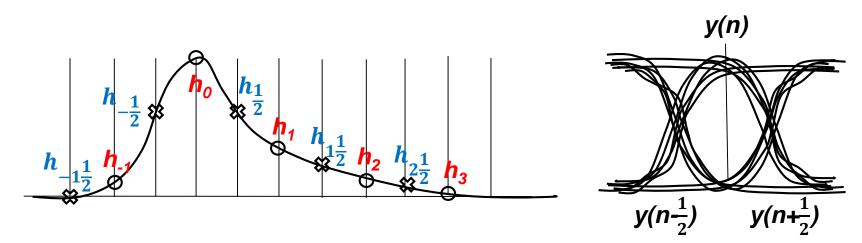

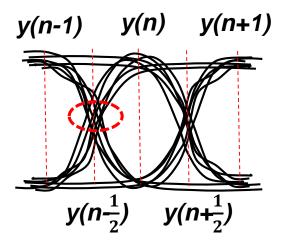

### Single Bit Response & Eye Diagram

• Data Samples:

$y(n) = h_3 x(n-3) + h_2 x(n-2) + h_1 x(n-1) + h_0 x(n) + h_{-1} x(n+1)$ ISI due to Post-Cursor Main Cursor ISI due to Pre-Cursor

• Edge Samples:

$$y\left(n-\frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-3) + h_{1\frac{1}{2}}x(n-2) + h_{\frac{1}{2}}x(n-1) + h_{-\frac{1}{2}}x(n) + h_{-1\frac{1}{2}}x(n+1)$$

$$y\left(n+\frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-2) + h_{1\frac{1}{2}}x(n-1) + h_{\frac{1}{2}}x(n) + h_{-\frac{1}{2}}x(n+1) + h_{-1\frac{1}{2}}x(n+2)$$

© 2020 DK Jeong

Topics in IC Design

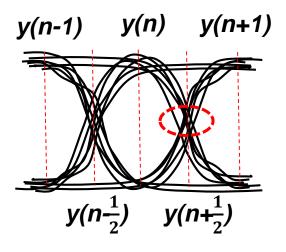

### **Eye Diagram and Timing Recovery**

For the -1 -> +1 transition at (n-1/2) (A), if  $h_{\frac{1}{2}} > h_{-\frac{1}{2}}$ , then y(n-1/2) > 0. Alexander PD asserts DOWN (VCO too fast), and the next sampling time pushed down, then  $h_{-\frac{1}{2}}$  goes down and  $h_{\frac{1}{2}}$  goes up, eventually making  $h_{\frac{1}{2}} = h_{-\frac{1}{2}}$ . Same result for +1->-1 transition (B)

• Zero Crossing levels at y(n-1/2) A. -1->+1 transition at y(n-1) = -1, y(n) = +1  $y\left(n - \frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-3) + h_{1\frac{1}{2}}x(n-2) - h_{\frac{1}{2}} + h_{-\frac{1}{2}} + h_{-1\frac{1}{2}}x(n+1)$ B. +1->-1 transition at y(n-1) = +1, y(n) = -1  $y\left(n - \frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-3) + h_{1\frac{1}{2}}x(n-2) + h_{\frac{1}{2}} - h_{-\frac{1}{2}} + h_{-1\frac{1}{2}}x(n+1)$

© 2020 DK Jeong

**Topics in IC Design**

### **Eye Diagram and Timing Recovery**

For the -1 -> +1 transition at (n+1/2) (B), if  $h_{\frac{1}{2}} < h_{-\frac{1}{2}}$ , then y(n+1/2) > 0. Alexander PD asserts UP (VCO too slow), and the next sampling time pulled up, then  $h_{-\frac{1}{2}}$  goes up and  $h_{\frac{1}{2}}$  goes down, eventually making  $h_{\frac{1}{2}} = h_{-\frac{1}{2}}$ . Same result for +1->-1 transition (B)

Zero Crossing levels at y(n+1/2) A. -1->+1 transition at y(n) = -1, y(n+1) = +1  $y\left(n + \frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-2) + h_{1\frac{1}{2}}x(n-1) - h_{\frac{1}{2}} + h_{-\frac{1}{2}} + h_{-1\frac{1}{2}}x(n+2)$ B. +1->-1 transition at y(n) = +1, y(n+1) = -1

$$y\left(n+\frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-2) + h_{1\frac{1}{2}}x(n-1) + \frac{1}{2} - h_{-\frac{1}{2}} + h_{-\frac{1}{2}}x(n+2)$$

•

## **Eye Diagram and Timing Recovery**

- 2x oversampling with Alexander PD,

- $h_{\frac{1}{2}} = h_{-\frac{1}{2}}$  holds.

- may not offer max SNR when SBR is not symmetric.

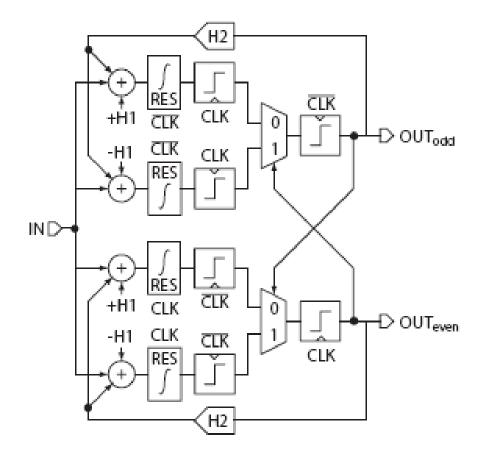

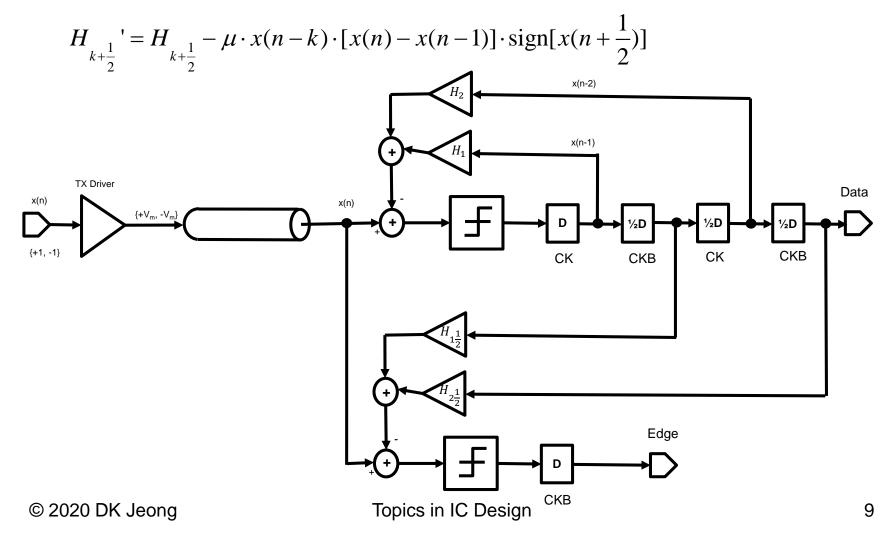

### **Edge Equalization**

- Reduce DDJ at edge for low-jitter clock recovery

- Edge DFE

- Reduce the ISI due to edge post-cursors  $h_{1\frac{1}{2}}$ ,  $h_{2\frac{1}{2}}$ , etc.

- Not possible to cancel ISI due to edge pre-cursors  $h_{-1\frac{1}{2}}$ , etc.

• Edge Samples:

$$y\left(n-\frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-3) + h_{1\frac{1}{2}}x(n-2) + h_{\frac{1}{2}}x(n-1) + h_{-\frac{1}{2}}x(n) + h_{-1\frac{1}{2}}x(n+1)$$

$$y\left(n+\frac{1}{2}\right) = h_{2\frac{1}{2}}x(n-2) + h_{1\frac{1}{2}}x(n-1) + h_{\frac{1}{2}}x(n) + h_{-\frac{1}{2}}x(n+1) + h_{-1\frac{1}{2}}x(n+2)$$

### **Edge DFE Architecture**

Edge Adaptation

### References

- Sameh Abrahim and Behzad Razavi, "A 20-Gbps Serial Link for High-Loss Channels" UCLA

- MAXIM, "Spectral Content of NRZ Test Patterns"

- Koon-Lun Jackie Wong, E-Hung Chen, and Chih-Kong Ken Yang, "Edge and Data Adapti ve Equalization of Serial-Link Transceivers" IEEE, JSSC Sep. 2008

- Haechang Lee, "A 16 Gb/s/Link, 64 GB/s Bidirectional Asymmetric Memory Interface" IEEE, JSSC April 2009

- Massimo Pozzoni, "A Multi-Standard 1.5 to 10 Gb/s Latch-Based 3-Tap DFE Receiver With a SSC Tolerant CDR for Serial Backplane Communication" IEEE, JSSC Apr. 2009

- Srikanth Gondi and Behzad Razavi, "Equalization and Clock and Data Recovery Techniques for 10-Gb/s CMOS Serial-Link Receivers", IEEE JSSC Sept. 2007

- Jian-Hao Lu "A 40Gb/s Low-Power Analog Equalizer in 0.13um CMOS Technology", IEEE SOVC 2008

- A. Momtaz "An 80mW 40Gb/s 7-Tap T/2-Spaced FFE in 65nm CMOS", IEEE ISSCC 2009