#### Lecture 14 : Digital Gates and Combinational Logics

: To introduce the digital gates with combinational logics

# Gate and Truth Table

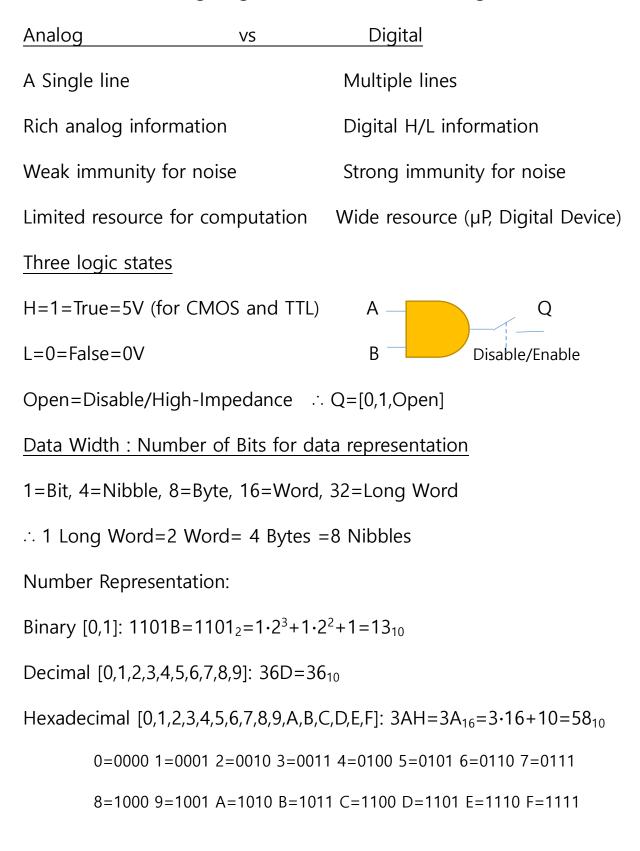

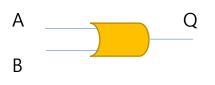

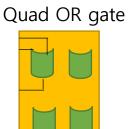

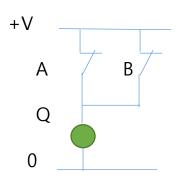

1. OR gate

$: Q=A OR B = A \lor B = A+B$

Symbol

Relay Circuit

| A | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

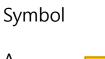

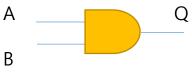

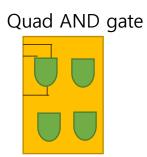

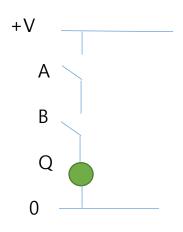

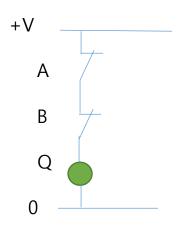

2. AND Gate

# Relay Circuit

| A | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

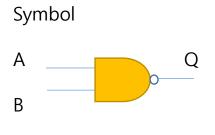

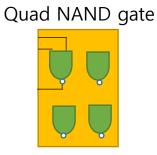

## 3. NAND Gate

: Q=A NAND B= Not  $(A \land B) = (Not A) \lor (Not B) = \underline{A} \lor \underline{B} = \underline{A} + \underline{B}$

## Relay Circuit

| A | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

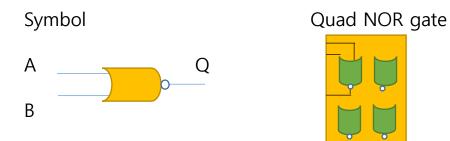

## 4. NOR Gate

: Q=A NOR B= Not(A OR B) = Not A  $\land$  Not B=<u>A</u> $\land$ <u>B</u>=<u>A</u> $\land$ <u>A</u> $\land$ <u>A</u>=<u>A</u> $\land$ <u>A</u>=<u>A</u> $\land$ <u>A</u> $\land$ <u>A</u>

## Relay Circuit

| A | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

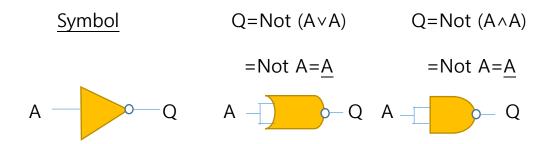

#### 5. Inverter Gate

: Q= Not A=<u>A</u>

## Truth Table

| Α | Q |

|---|---|

| 0 | 1 |

| 0 | I |

1 0

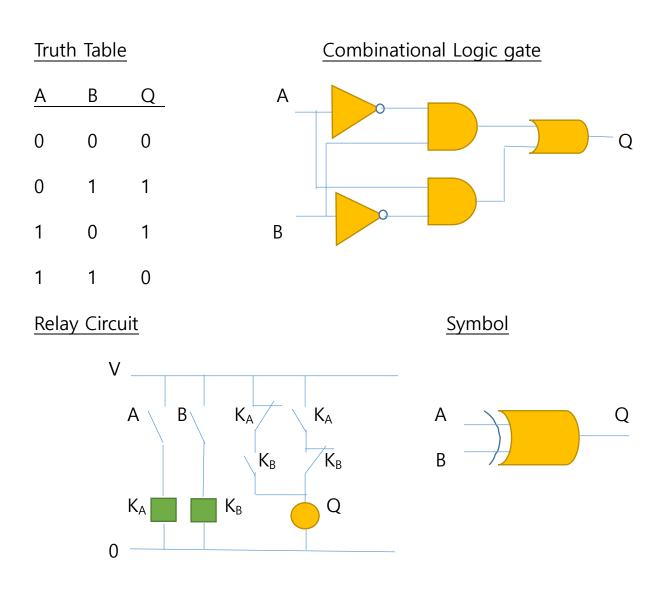

5. XOR (Exclusive OR) Gate, or Digital Comparator : Q=A XOR B = 1 (if A,B are different), 0 (if A,B are the same) =(<u>A</u>  $\land$  B)  $\lor$  (A  $\land$  <u>B</u>)=<u>A</u> $\cdot$ B+A $\cdot$ <u>B</u>

# Relay(계전기,繼電器): Electro-Magnet connected multiple switches for

#### various functions

Source:https://theveterinarymedicine.com/General-Purpose-Relays-Power-PCB-Relay/Other-Transformers-zbtfe-582626.action

| <u>K<sub>A</sub> or K<sub>B</sub></u> | $A_1$          | 1  | 23    |   |

|---------------------------------------|----------------|----|-------|---|

|                                       |                |    | \/    | - |

|                                       | A <sub>2</sub> | 1' | 2' 3' |   |

1,2: a(NO) Type, 3: b(NC) Type Multiple points connected to magnet NO=Normally Open, NC=Normally Closed

#### $\mathsf{A}_1$ , $\mathsf{A}_2$ : Terminal for Electro-Magnet

#### Functions of Relay:

- (1) Switch points(접점,接點) increase; ex) one to three

- (2) Voltage Change ; ex) 5V Switch to 12V Switch

- (3) Switch Type conversion; ex) a Type to b Type or vice versa.

- (4) Logic Function ; Logic statement execution

#### Logic Statement/Logic Function

: Logic statement can be converted to Logic function,

Thence the Logic circuit can be drawn accordingly,

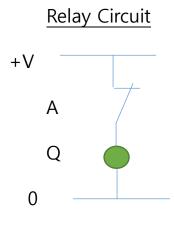

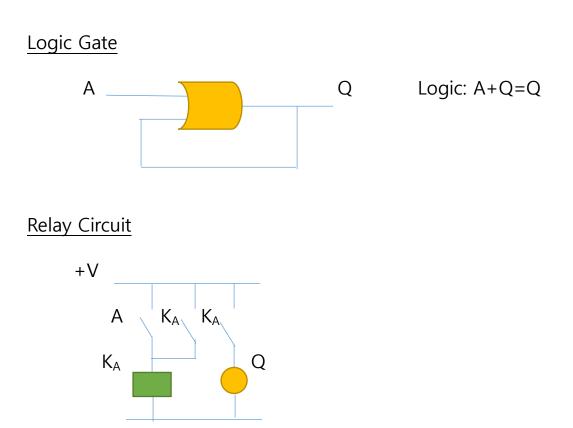

- Case1) Self-Holding Circuit

- : To hold the Switch function ('ON') even when the Switch is released.

It is widely applied to M/C operation.

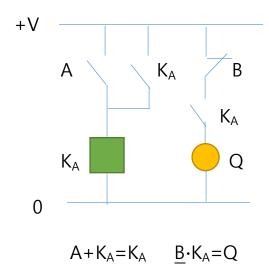

$A+K_A=K_A$   $K_A=Q$   $\therefore$  A+Q=Q

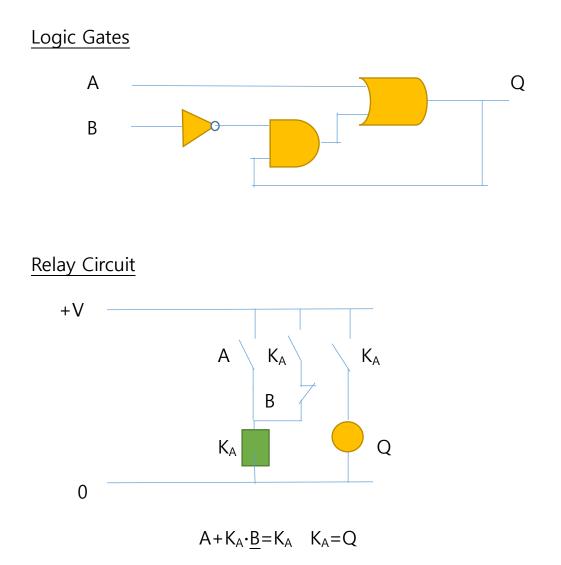

For OFF function, we need a OFF S/W that is B signal, to be pressed, and there are two modes of circuit configuration: Dominant ON mode and Dominant OFF mode. (1) Dominant ON

: To insert OFF S/W, that is B, in front of OR gate. It gives ON even when the A,B switches are pressed. Then logic function is,  $A + \underline{B} \cdot Q = Q$

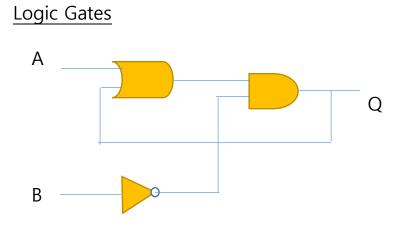

## (2) Dominant OFF

:To insert OFF S/W, that is B, in front of AND gate. It gives OFF when the A,B are pressed. The logic function is,  $(A+Q)\cdot\underline{B}=Q$

Relay Circuit

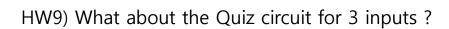

Case2) Interlock Circuit (or Quiz Circuit)

: To interlock each other, and it gives the fastest signal to pass while others are locked. Also, it is called 'Quiz Circuit'.

Logic Gates Ρ А Q В Relay Circuit +V K<sub>A</sub> B  $K_{\text{B}}$ А  $\mathsf{K}_\mathsf{B}$  $\mathsf{K}_\mathsf{A}$ P Q  $\mathsf{K}_\mathsf{A}$  $\mathsf{K}_\mathsf{B}$ 0

Logic Function:  $A \cdot \underline{Q} = P$ ,  $B \cdot \underline{P} = Q$

$A \cdot \underline{K}_{\underline{B}} = K_{A}$ ;  $B \cdot \underline{K}_{\underline{A}} = K_{B}$ ;  $K_{A} = P$ ;  $K_{B} = Q$

#### Karnaugh Map

: To derive Logic function from the logic statement or truth table

Step1: Make Truth table

Step2: Karnaugh Map that is to align as the sequence of only one bit change from one location to the next

Step3: Identify the 1's location on the map,

and this gives the Logic function

Step 4: Verify the Karnaugh Map, by checking the Truth table

Ex) Design an Electronic Voting System of 3 inputs of (A,B,C) such that at least two inputs are 1, then output(Q) gives 1.

| <u>A</u> | В | С | Q |

|----------|---|---|---|

| 0        | 0 | 0 | 0 |

| 0        | 0 | 1 | 0 |

| 0        | 1 | 0 | 0 |

| 0        | 1 | 1 | 1 |

| 1        | 0 | 0 | 0 |

| 1        | 0 | 1 | 1 |

| 1        | 1 | 0 | 1 |

| 1        | 1 | 1 | 1 |

## Karnaugh Map

| С | AB | 00 | 01 | 11 | 10 |

|---|----|----|----|----|----|

| 0 |    | 0  | 0  | 1  | 0  |

| 1 |    | 0  | 1  | 1  | 1  |

$\therefore$  Logic Function : The 1's location gives Q=AB+AC+BC

Logic Gates

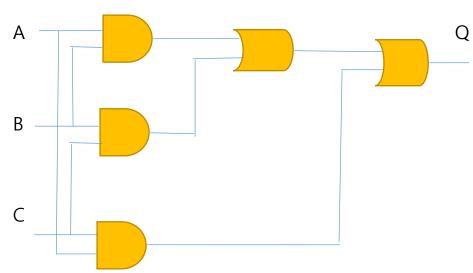

Therefore the logic gates are widely used for the logic calculation Similarly, the arithmetic gates such as Adder, Subtractor, Multiplier, Divider gates can be used for the arithmetic calculation as follows;

$A_4A_3A_2A_1$

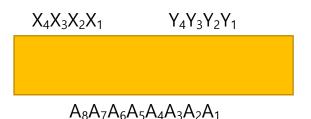

Multiplier Gate, X\*Y=A; SHL(SHift Left) and Add

Divider Gate, X/Y=A; SHR(SHift Right) and Subtract

where quotient (lower 4bits), Remainder (higher 4bits)

$X_4X_3X_2X_1$   $Y_4Y_3Y_2Y_1$  $A_8A_7A_6A_5A_4A_3A_2A_1$