## **Chapter 9 Cascode Stages and Current Mirrors**

9.2 Current Mirrors

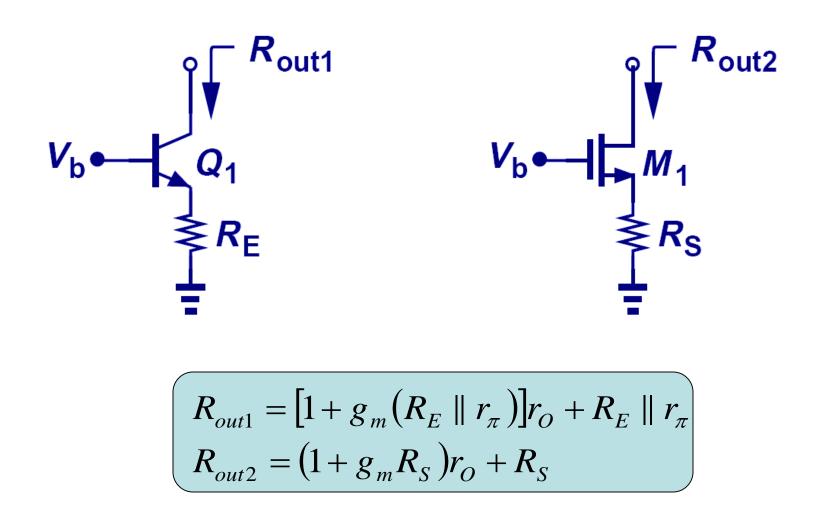

#### **Boosted Output Impedances**

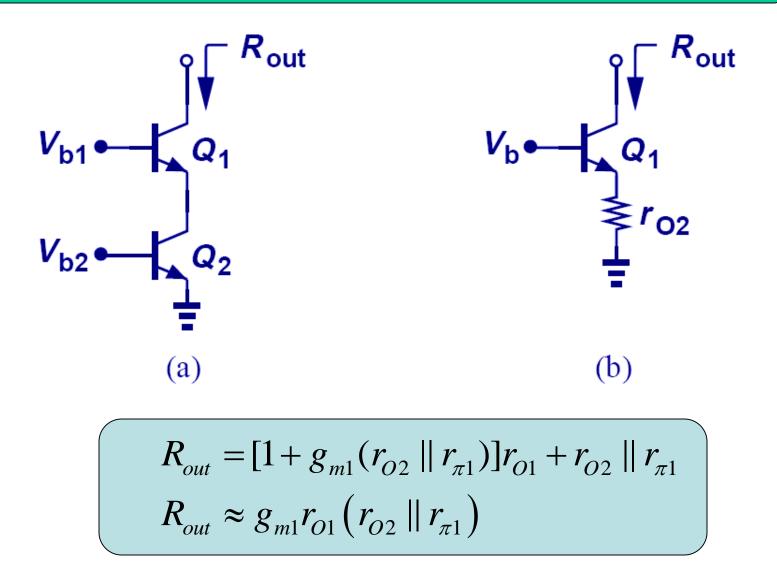

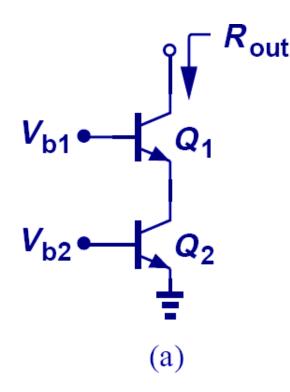

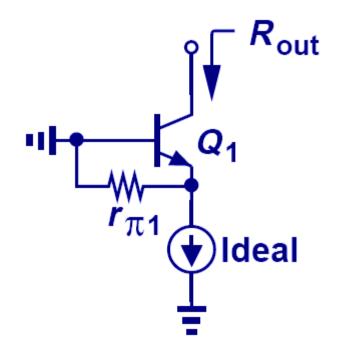

#### **Bipolar Cascode Stage**

If Q<sub>1</sub> and Q<sub>2</sub> in Fig.9.2(a) are biased at a collector current of 1mA, determine the output resistance. Assume β =100 and V<sub>A</sub>=5V for both transistors.

$$g_m = I_C / V_T, r_O = V_A / I_C,$$

$$r_\pi = \beta V_T / I_C$$

$$R_{out} \approx \frac{I_{C1}}{V_T} \cdot \frac{V_{A1}}{I_{C1}} \cdot \frac{\frac{V_{A2}}{I_{C2}} \cdot \frac{\beta V_T}{I_{C1}}}{\frac{V_{A2}}{I_{C2}} + \frac{\beta V_T}{I_{C1}}}$$

$$\approx \frac{1}{I_{C1}} \cdot \frac{V_A}{V_T} \cdot \frac{\beta V_A V_T}{V_A + \beta V_T},$$

$$I_C = I_{C1} = I_{C2} \text{ and } V_A = V_{A1} = V_{A2}$$

$R_{out} \approx 328.9 \text{ k}\Omega.$

## **Maximum Bipolar Cascode Output Impedance**

$$\begin{array}{c} \hline R_{out,\max} \approx g_{m1}r_{O1}r_{\pi 1} \\ \hline R_{out,\max} \approx \beta_1 r_{O1} \end{array} \end{array}$$

#### The maximum output impedance of a bipolar cascode is bounded by the ever-present r<sub>π</sub> between emitter and ground of Q<sub>1</sub>.

Suppose in Example 9.1, the Early voltage of Q<sub>2</sub> is equal to 50V. Compare the resulting output impedence of the cascade with the upper bound given by Eq.(9.12).

Since

$$g_{m1} = (26 \ \Omega)^{-1}$$

,  $r_{\pi 1} = 2.6 \ \mathrm{k}\Omega$ ,  $r_{O1} = 5 \ \mathrm{k}\Omega$ , and  $r_{O2} = 50 \ \mathrm{k}\Omega$ , we have

$R_{out} \approx g_{m1} r_{O1} (r_{O1} || r_{\pi 1})$

$\approx 475 \ \mathrm{k}\Omega$ .

The upper bound is equal to 500 k $\Omega$ , about 5% higher.

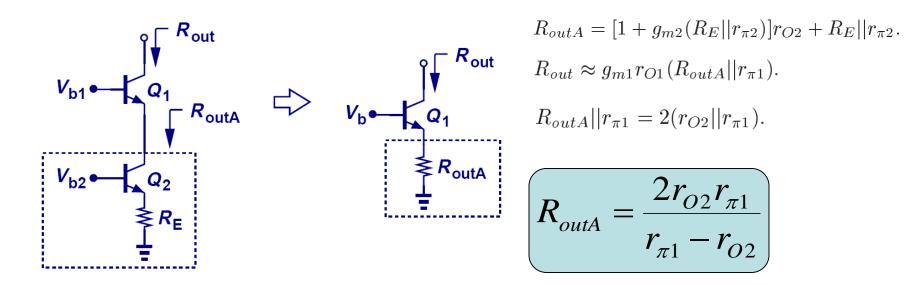

We wish to increase the output resistance of the bipolar cascade of Fig. 9.2(a) by a factor of two through the use of resistive degeneration in the emitter of  $Q_2$ . Determine the required value of the degeneration resistor if  $Q_1$  and  $Q_2$  are identical.

> Typically  $r_{\pi}$  is smaller than  $r_0$ , so in general it is impossible to double the output impedance by degenerating  $Q_2$  with a resistor.

#### **PNP Cascode Stage**

$$R_{out} = [1 + g_{m1}(r_{O2} || r_{\pi 1})]r_{O1} + r_{O2} || r_{\pi 1}$$

$$R_{out} \approx g_{m1}r_{O1}(r_{O2} || r_{\pi 1})$$

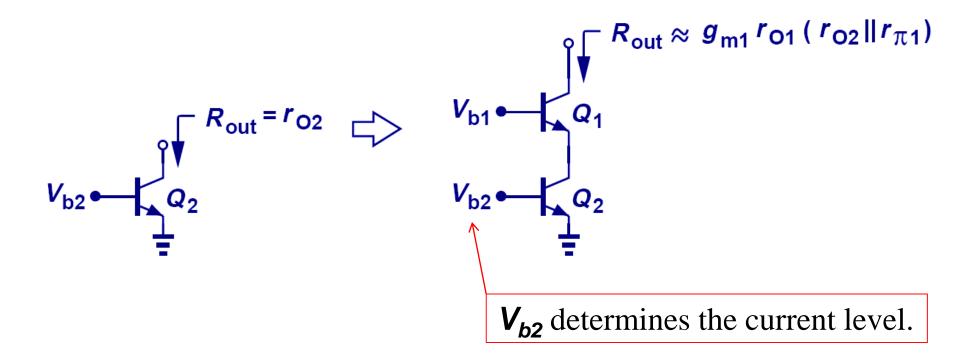

## **Another Interpretation of Bipolar Cascode**

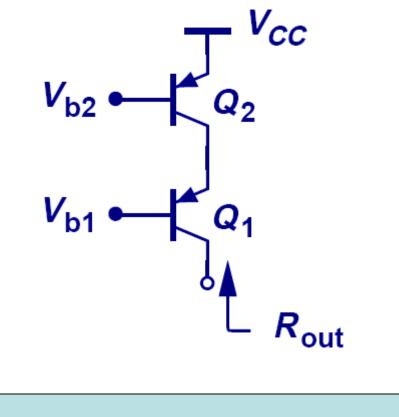

Instead of treating cascode as Q<sub>2</sub> degenerating Q<sub>1</sub>, we can also think of it as Q<sub>1</sub> stacking on top of Q<sub>2</sub> (current source) to boost Q<sub>2</sub>'s output impedance.

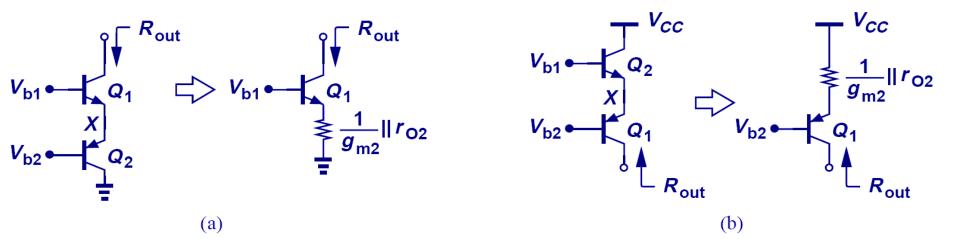

#### **False Cascodes**

$$\begin{split} & \left[ R_{out} = \left[ 1 + g_{m1} \left( \frac{1}{g_{m2}} \parallel r_{O2} \parallel r_{\pi 1} \right) \right] r_{O1} + \frac{1}{g_{m2}} \parallel r_{O2} \parallel r_{\pi 1} \\ & R_{out} \approx \left( 1 + \frac{g_{m1}}{g_{m2}} \right) r_{O1} + \frac{1}{g_{m2}} \approx 2r_{O1} \end{split} \right] \end{split}$$

When the emitter of Q<sub>1</sub> is connected to the emitter of Q<sub>2</sub>, it's no longer a cascode since Q<sub>2</sub> becomes a diode-connected device instead of a current source.

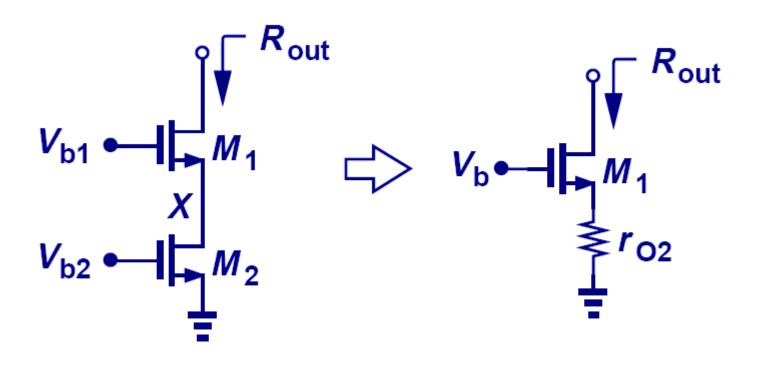

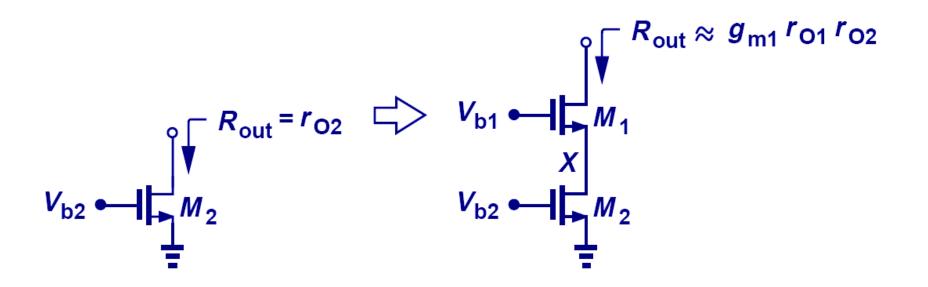

#### **MOS Cascode Stage**

$$R_{out} = (1 + g_{m1}r_{O2})r_{O1} + r_{O2}$$

$$R_{out} \approx g_{m1}r_{O1}r_{O2}$$

**>** Design an NMOS cascade for an output impedance of 500kΩ and a current of 0.5mA. For simplicity, assume  $M_1$  and  $M_2$  in Fig 9.8 are identical (they need not be). Assume  $\mu_n C_{ox} = 100 \mu A/V^2$  and  $\lambda = 0.1V^{-1}$ .

We must determine W/L for both transistors such that

$g_{m1}r_{O1}r_{O2} = 500 \text{ k}\Omega.$

Since  $r_{O1} = r_{O2} = (\lambda I_D)^{-1} = 20 \text{ k}\Omega$ , we require that  $g_{m1} = (800 \Omega)^{-1}$  and hence

$$\sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} = \frac{1}{800 \ \Omega}.$$

It follows that

$$\frac{W}{L} = 15.6.$$

We should also note that  $g_{m1}r_{O1} = 25 \gg 1$ .

CH 9 Cascode Stages and Current Mirrors

## **Another Interpretation of MOS Cascode**

- Similar to its bipolar counterpart, MOS cascode can be thought of as stacking a transistor on top of a current source.

- Unlike bipolar cascode, the output impedance is not limited by β.

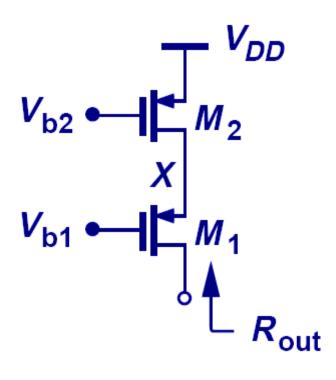

#### **PMOS Cascode Stage**

$$R_{out} = (1 + g_{m1}r_{O2})r_{O1} + r_{O2}$$

$$R_{out} \approx g_{m1}r_{O1}r_{O2}$$

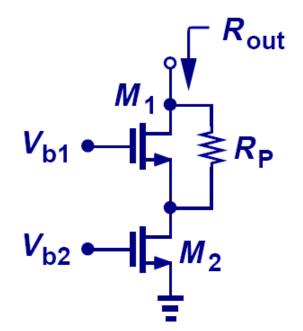

During manufacturing, a large parasitic resistor, R<sub>P</sub>, has appeared in a cascode as shown in Fig. 9. 11. Determine the output resistance.

$R_p$  is in parallel with  $r_{O1}$ .

$$R_{out} = g_{m1}(r_{O1}||R_p)r_{O2}.$$

If  $g_{m1}(r_{O1}||R_p)$  is not much greater than unity, we return to the original equation, (9.22),

$$R_{out} = (1 + g_{m1}r_{O2})(r_{O1} \parallel R_P) + r_{O2}$$

R<sub>P</sub> will lower the output impedance, since its parallel combination with r<sub>01</sub> will always be lower than r<sub>01</sub>.

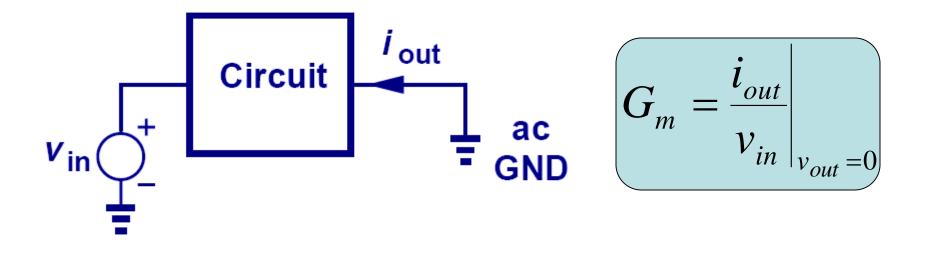

## **Short-Circuit Transconductance**

#### The short-circuit transconductance of a circuit measures its strength in converting input voltage to output current.

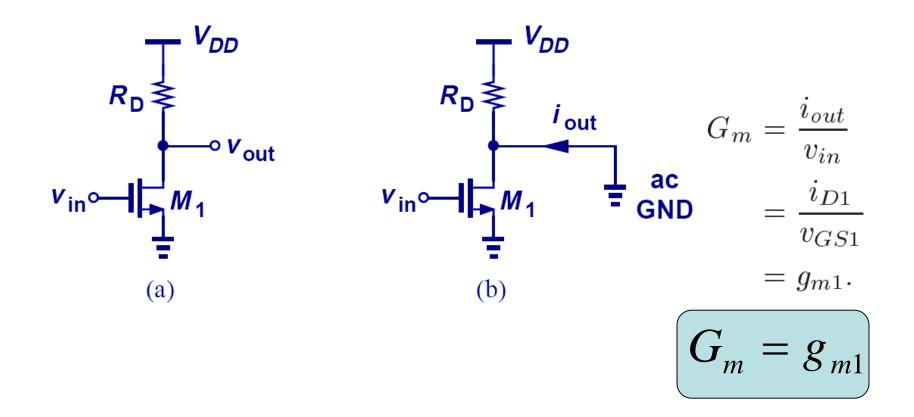

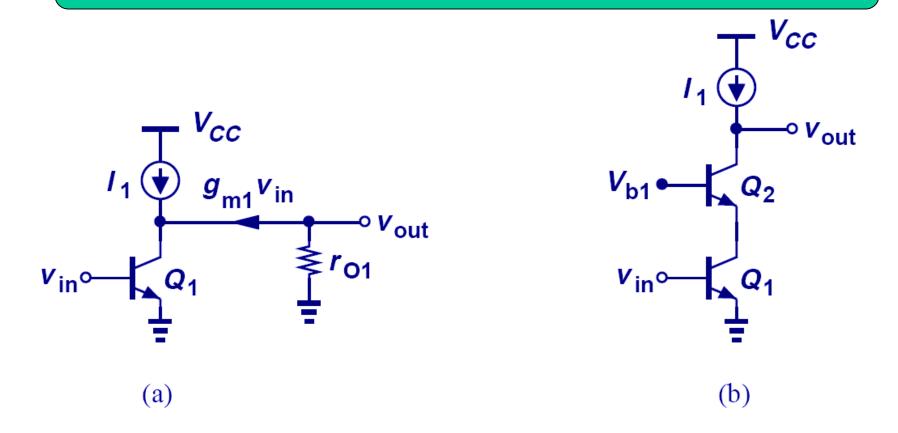

#### Calculate the transconductance of the CS stage shown in Fig. 9.13(a).

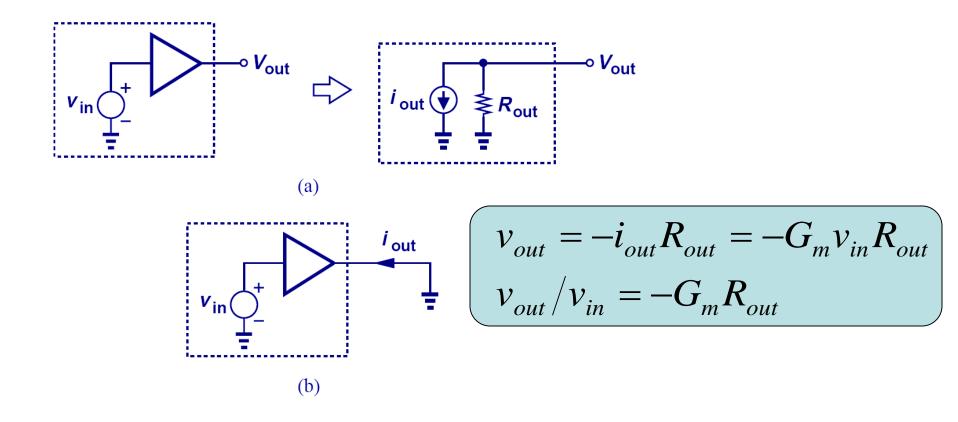

## **Derivation of Voltage Gain**

By representing a linear circuit with its Norton equivalent, the relationship between V<sub>out</sub> and V<sub>in</sub> can be expressed by the product of G<sub>m</sub> and R<sub>out</sub>.

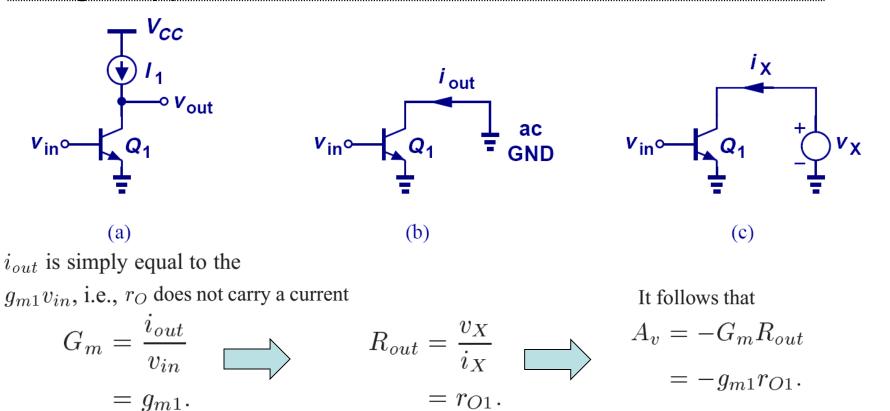

Determine the voltage gain of the common-emitter stage shown in Fig. 9.15(a).

$$A_v = -g_{m1}r_{O1}$$

## **Comparison between Bipolar Cascode and CE Stage**

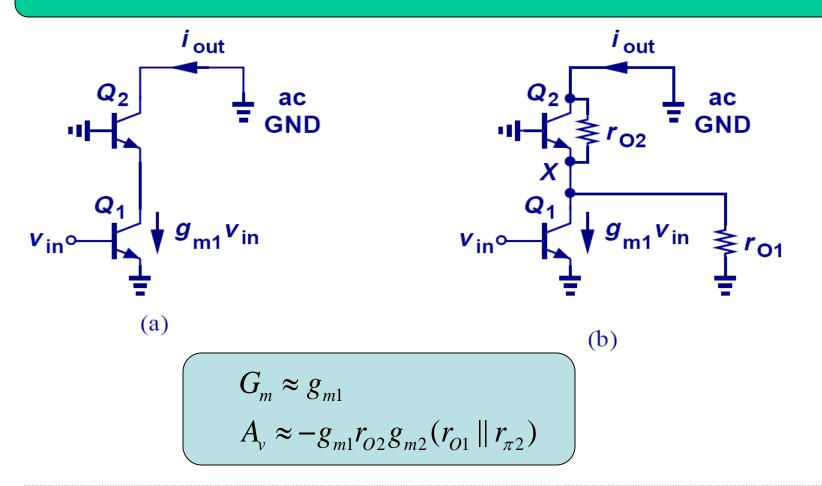

Since the output impedance of bipolar cascode is higher than that of the CE stage, we would expect its voltage gain to be higher as well.

## **Voltage Gain of Bipolar Cascode Amplifier**

Since r<sub>o</sub> is much larger than 1/g<sub>m</sub>, most of I<sub>C,Q1</sub> flows into the diode-connected Q<sub>2</sub>. Using R<sub>out</sub> as before, A<sub>V</sub> is easily calculated.

The bipolar cascade of Fig.9.16(b) is biased at a current of 1mA. If V<sub>A</sub>=5V and β=100 for both transistors, determine the voltage gain. Assume the load is an ideal current source.

$g_{m1} = (26 \ \Omega)^{-1}, r_{\pi 1} \approx r_{\pi 2} \approx 2600 \ \Omega,$   $r_{O1} \approx r_{O2} = 5 \ \text{k}\Omega. \text{ Thus,}$   $g_{m1}(r_{O1} || r_{\pi 2}) = 65.8$   $G_m \approx g_{m1}$   $A_v \approx -g_{m1} r_{O2} g_{m2}(r_{O1} || r_{\pi 2})$  $|A_v| = 12,654.$

Cascoding thus raises the voltage gain by a factor of 65.8.

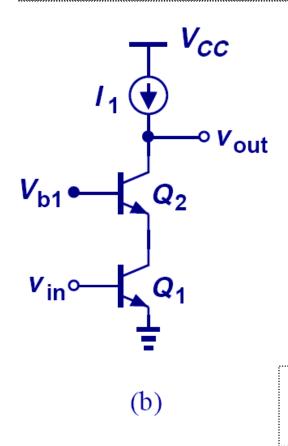

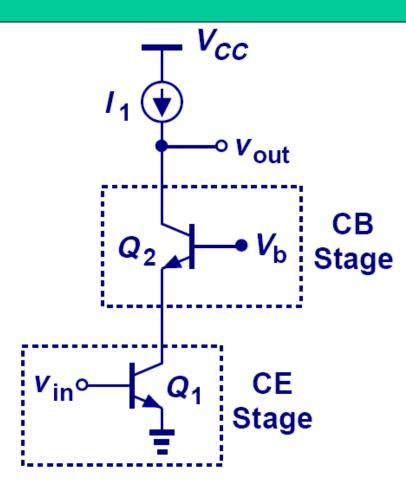

#### **Alternate View of Cascode Amplifier**

A bipolar cascode amplifier is also a CE stage in series with a CB stage.

#### **Practical Cascode Stage**

# Since no current source can be ideal, the output impedance drops.

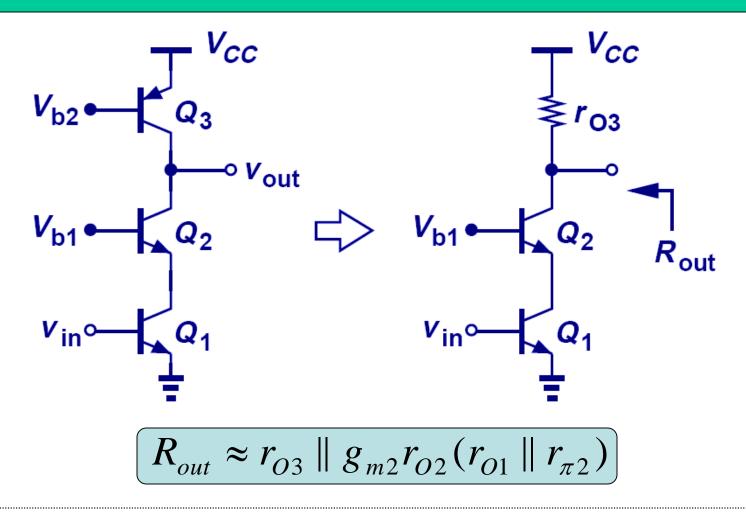

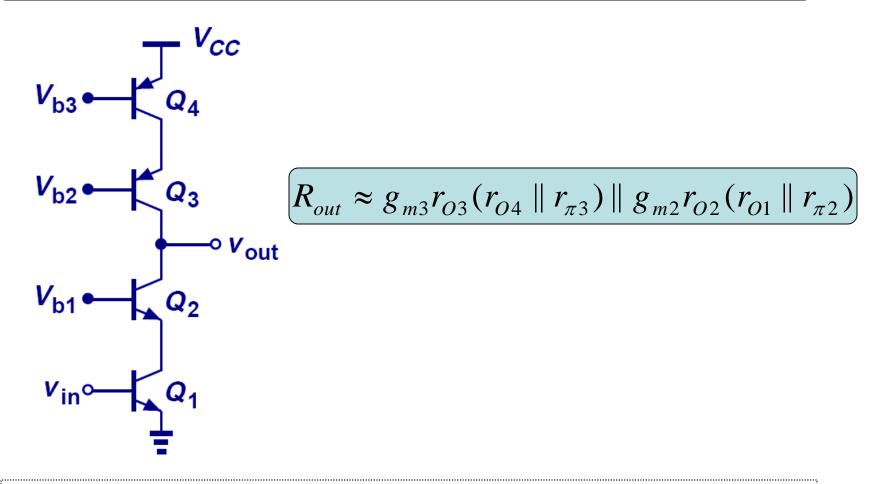

#### **Improved Cascode Stage**

#### In order to preserve the high output impedance, a cascode PNP current source is used.

Suppose the circuit of Example 9.9 incorporates a cascode load using *pnp* transistors with V<sub>A</sub> = 4V and β = 50. What is the voltage gain?

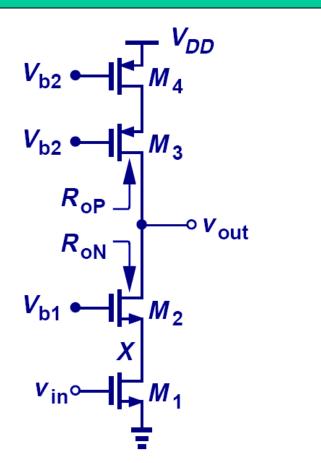

$R_{on} \approx g_{m2} r_{O2}(r_{O1} || r_{\pi 2})$

$R_{op} \approx g_{m3} r_{O3}(r_{O4} || r_{\pi 3}).$

The load transistors carry a collector current of approximately 1 mA. Thus,

$$R_{op} = g_{m3} r_{O3} (r_{O4} || r_{\pi 3})$$

$$= 151 \text{ k}\Omega$$

$$R_{on} = 329 \text{ k}\Omega.$$

$|A_v| = g_{m1}(R_{on}||R_{op})$ = 3,981.

Compared to the ideal current source case, the gain has fallen by approximately a factor of 3 because the *pnp* devices suffer from a lower Early voltage and  $\beta$ .

#### **MOS Cascode Amplifier**

$$A_{v} = -G_{m}R_{out}$$

$$A_{v} \approx -g_{m1} [(1 + g_{m2}r_{O2})r_{O1} + r_{O2}]$$

$$A_{v} \approx -g_{m1}r_{O1}g_{m2}r_{O2}$$

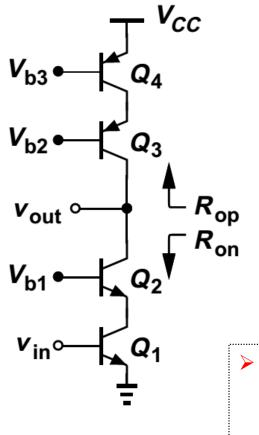

#### **Improved MOS Cascode Amplifier**

$$R_{on} \approx g_{m2} r_{O2} r_{O1}$$

$$R_{op} \approx g_{m3} r_{O3} r_{O4}$$

$$R_{out} = R_{on} \parallel R_{op}$$

Similar to its bipolar counterpart, the output impedance of a MOS cascode amplifier can be improved by using a PMOS cascode current source.

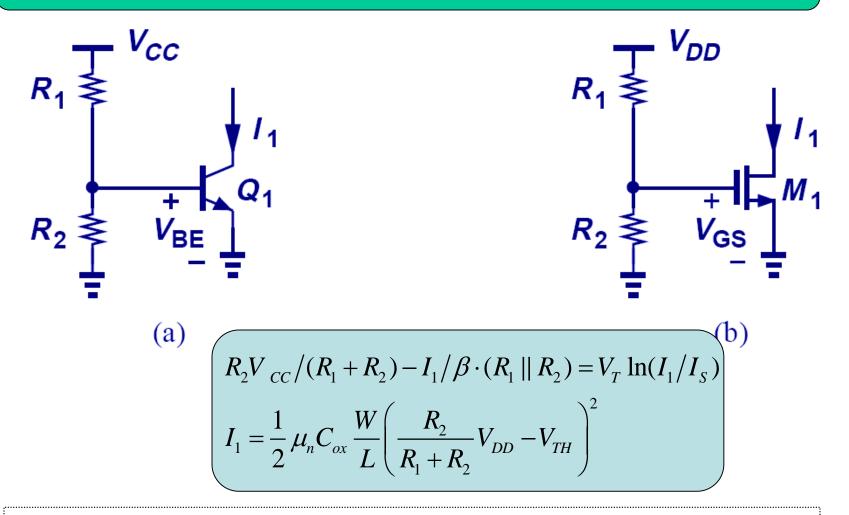

## **Temperature and Supply Dependence of Bias Current**

Since  $V_T$ ,  $I_S$ ,  $\mu_n$ , and  $V_{TH}$  all depend on temperature,  $I_1$  for both bipolar and MOS depends on temperature and supply.

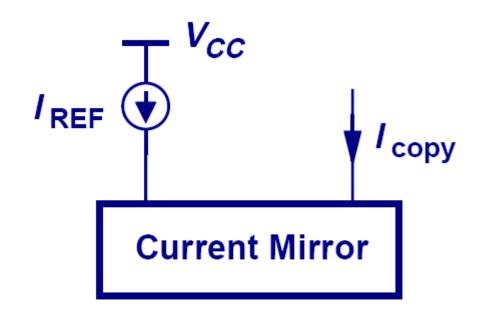

## **Concept of Current Mirror**

The motivation behind a current mirror is to sense the current from a "golden current source" and duplicate this "golden current" to other locations.

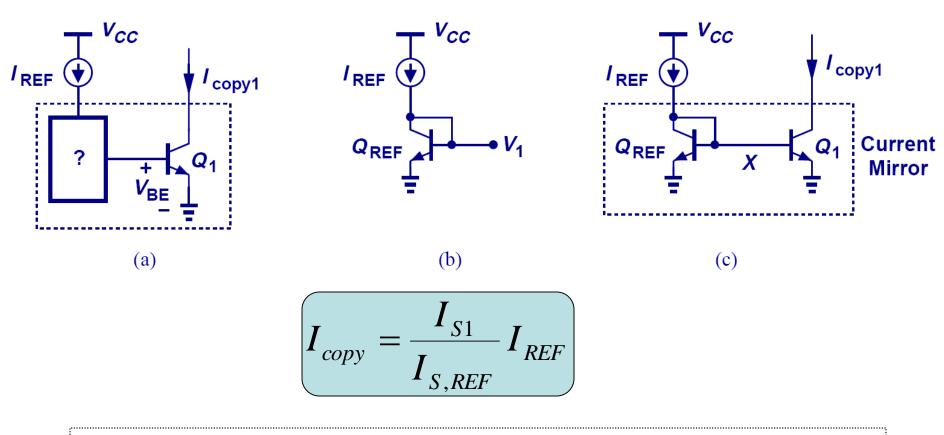

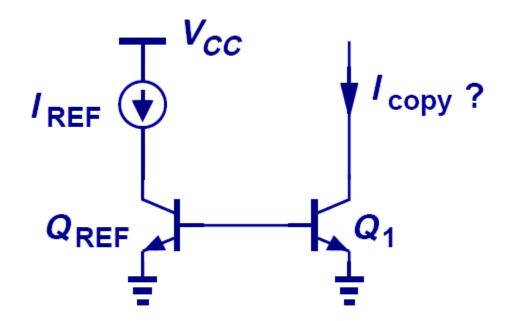

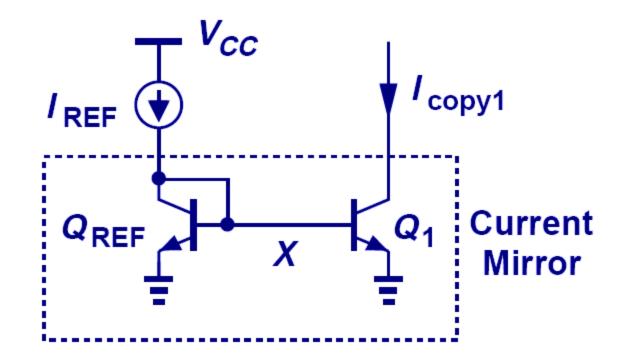

## **Bipolar Current Mirror Circuitry**

The diode-connected Q<sub>REF</sub> produces an output voltage V<sub>1</sub> that forces I<sub>copy1</sub> = I<sub>REF</sub>, if Q<sub>1</sub> = Q<sub>REF</sub>.

## **Bad Current Mirror Example I**

Without shorting the collector and base of Q<sub>REF</sub> together, there will not be a path for the base currents to flow, therefore, I<sub>copy</sub> is zero.

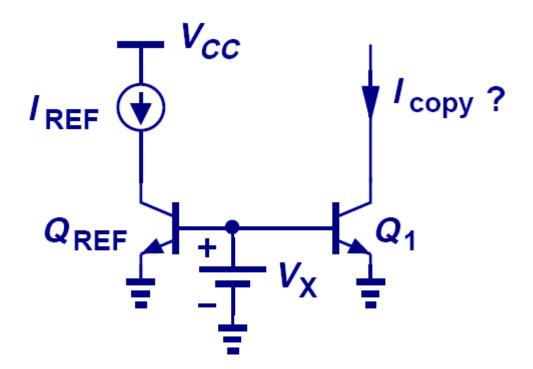

## **Bad Current Mirror Example II**

# Although a path for base currents exists, this technique of biasing is no better than resistive divider.

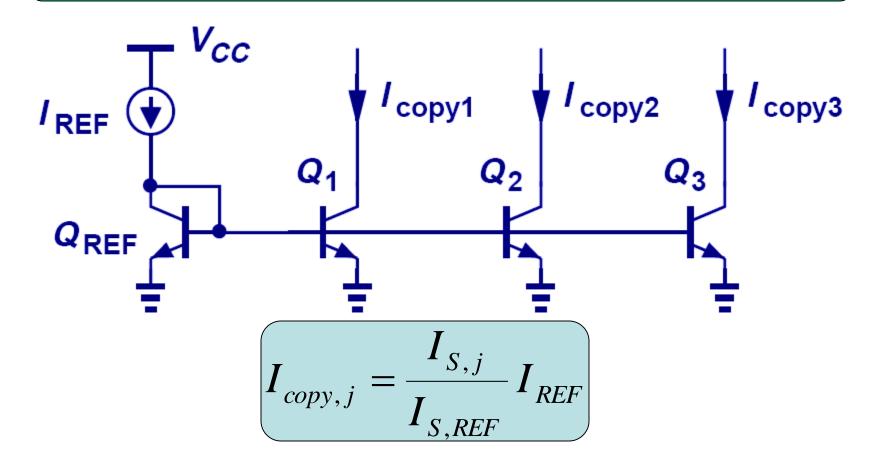

## **Multiple Copies of I<sub>REF</sub>**

Multiple copies of I<sub>REF</sub> can be generated at different locations by simply applying the idea of current mirror to more transistors.

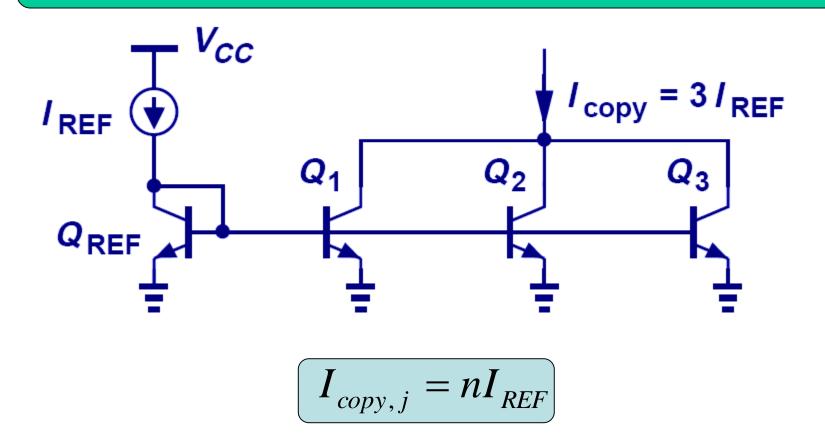

## **Current Scaling**

#### By scaling the emitter area of Q<sub>j</sub> n times with respect to Q<sub>REF</sub>, I<sub>copy,j</sub> is also n times larger than I<sub>REF</sub>. This is equivalent to placing n unit-size transistors in parallel.

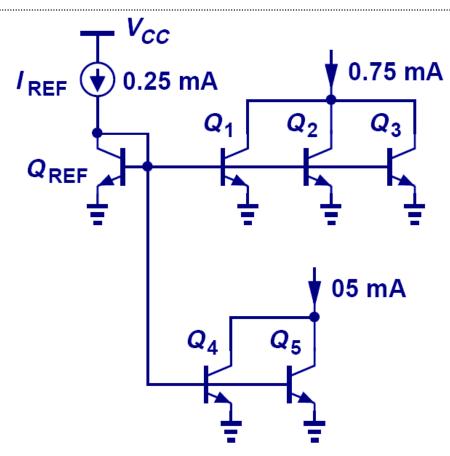

#### **Example 9.14 : Scaled Current**

A multistage amplifier incorporates two current sources of values 0.75mA and 0.5mA. Using a bandgap reference current of 0.25mA, design the require current sources. Neglect the effect of the base current for now.

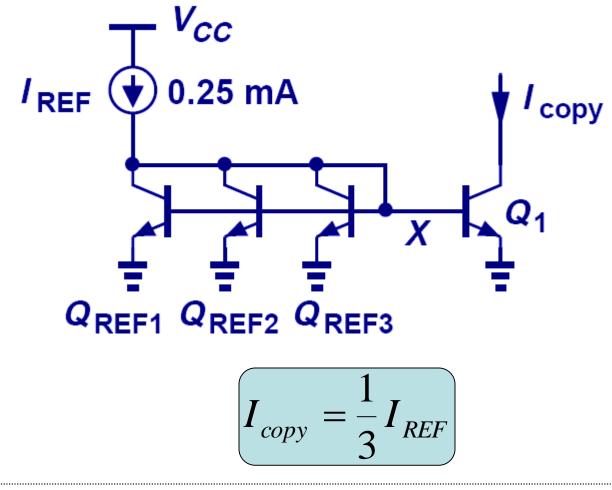

#### **Fractional Scaling**

A fraction of I<sub>REF</sub> can be created on Q<sub>1</sub> by scaling up the emitter area of Q<sub>REF</sub>.

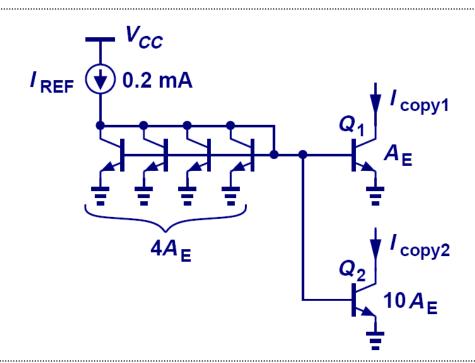

# **Example 9.15 : Different Mirroring Ratio**

It is desired to generate two currents equal to 50uA and 500uA from a reference of 200uA. Design the current mirror circuit.

Using the idea of current scaling and fractional scaling, I<sub>copy2</sub> is 0.5mA and I<sub>copy1</sub> is 0.05mA respectively. All coming from a source of 0.2mA.

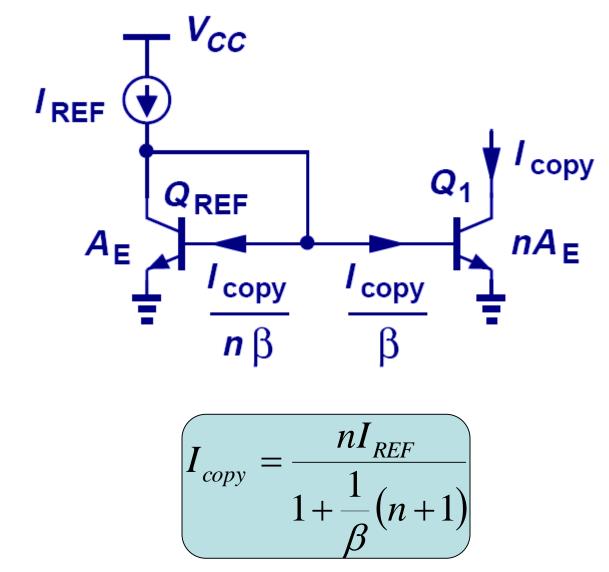

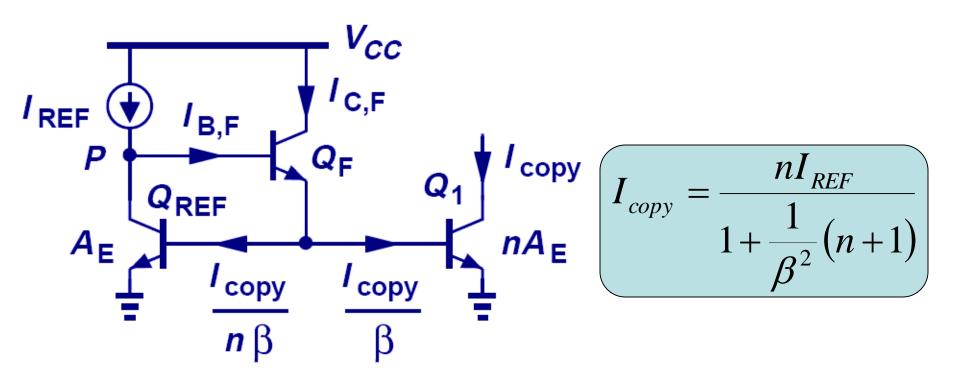

#### **Mirroring Error Due to Base Currents**

#### **Improved Mirroring Accuracy**

Because of Q<sub>F</sub>, the base currents of Q<sub>REF</sub> and Q<sub>1</sub> are mostly supplied by Q<sub>F</sub> rather than I<sub>REF</sub>. Mirroring error is reduced β times.

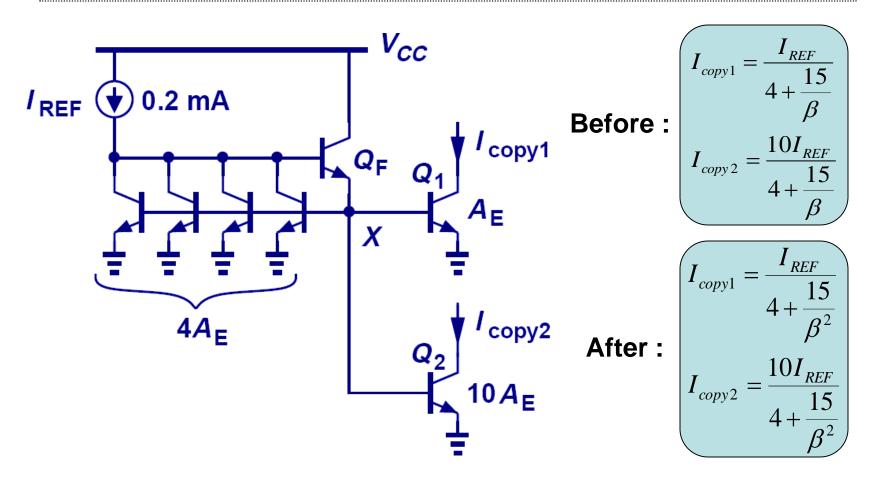

# **Example 9.16 : Different Mirroring Ratio Accuracy**

Compute the I<sub>copy1</sub> and I<sub>copy2</sub> in this figure before and after adding a follower.

# **Example 9.17 : Different Mirroring Ratio Accuracy**

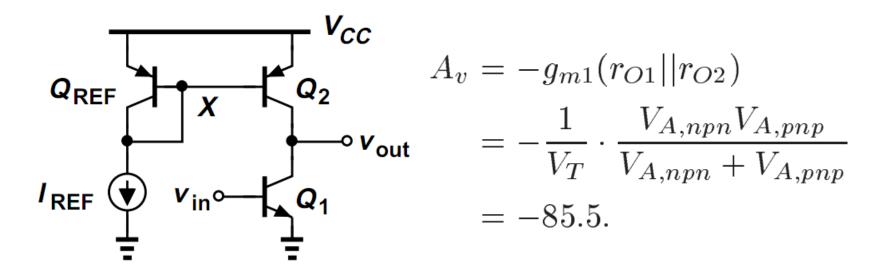

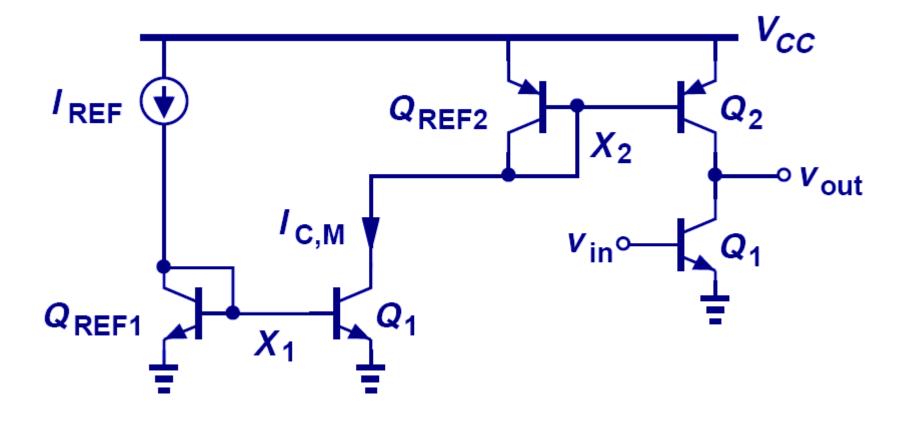

Design this circuit for a voltage gain 100 and a power budget of 2mW. Assume V<sub>A,npn</sub> = 5V, V<sub>A,pnp</sub> = 4V, I<sub>REF</sub> = 100uA, and V<sub>CC</sub> = 2.5V.

The gain is smaller than 100 because low Early voltages and V<sub>T</sub>, a fundamental constant of the technology, independent of the bias current.

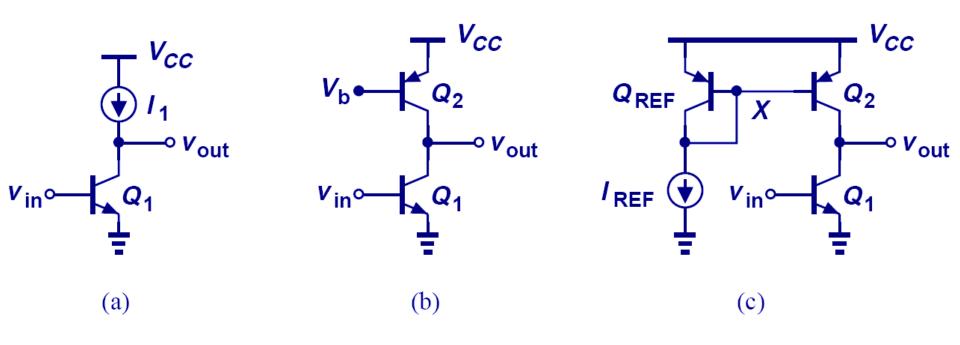

# **PNP Current Mirror**

# PNP current mirror is used as a current source load to an NPN amplifier stage.

#### **Generation of I<sub>REF</sub> for PNP Current Mirror**

#### **Current Mirror with Discrete Devices**

Let Q<sub>REF</sub> and Q<sub>1</sub> be discrete NPN devices. I<sub>REF</sub> and I<sub>copy1</sub> can vary in large magnitude due to I<sub>s</sub> mismatch.

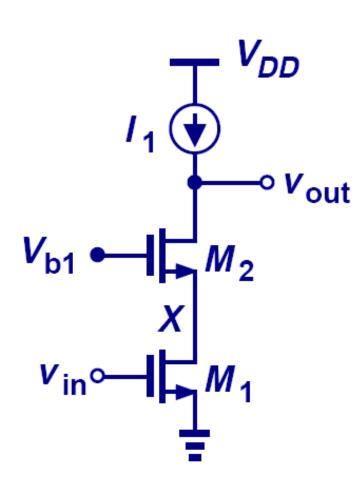

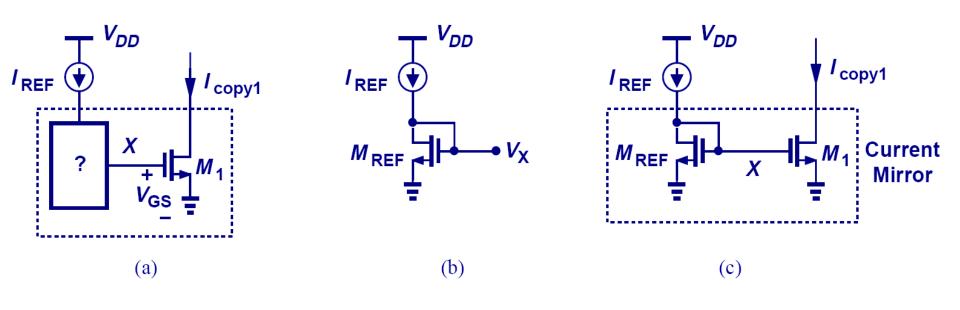

#### **MOS Current Mirror**

# The same concept of current mirror can be applied to MOS transistors as well.

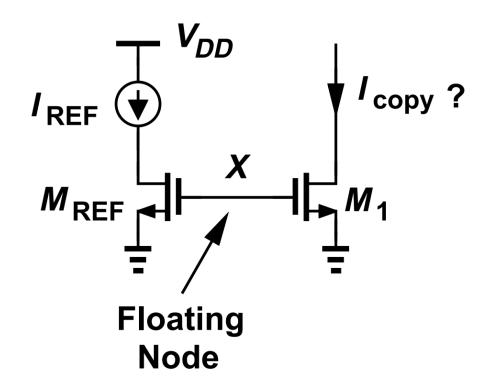

#### **Bad MOS Current Mirror Example**

- This is not a current mirror since the relationship between V<sub>X</sub> and I<sub>REF</sub> is not clearly defined.

- The only way to clearly define V<sub>X</sub> with I<sub>REF</sub> is to use a diodeconnected MOS since it provides square-law I-V relationship.

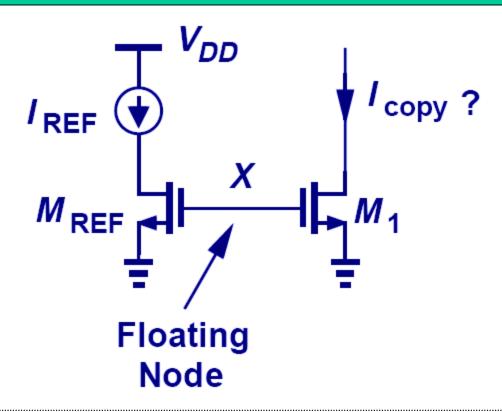

# **Example 9.20 : Current Mirror ?**

Is this current mirror? Explain what happens.

This circuit is not a current mirror because the gates of MREF and M1 are floating.

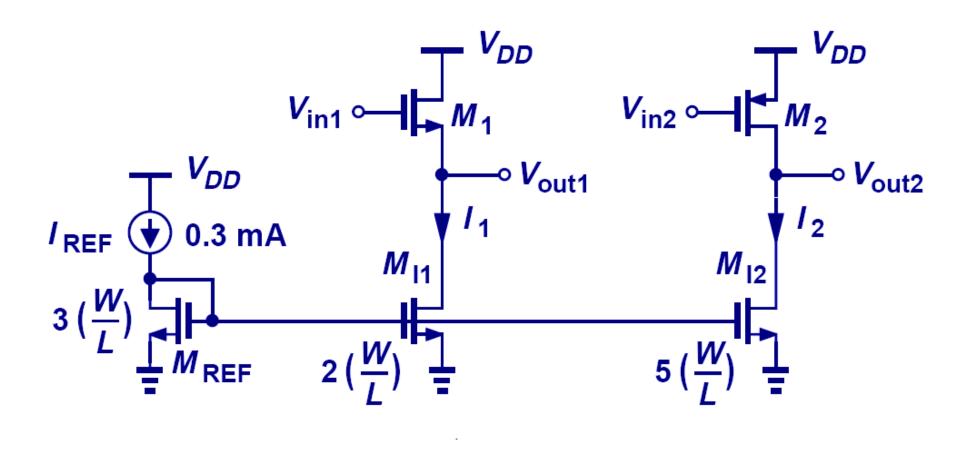

#### **Example 9.21 : Current Scaling**

> Similar to their bipolar counterpart, MOS current mirrors can also scale  $I_{REF}$  up or down ( $I_1 = 0.2mA$ ,  $I_2 = 0.5mA$ ).

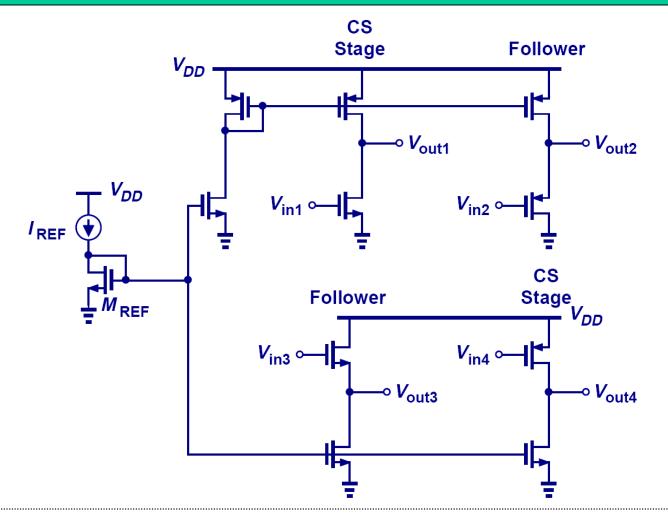

# **CMOS Current Mirror**

The idea of combining NMOS and PMOS to produce CMOS current mirror is shown above.