# **Chapter 10 Differential Amplifiers**

- 10.1 General Considerations

- 10.2 Bipolar Differential Pair

- > 10.3 MOS Differential Pair

- 10.4 Cascode Differential Amplifiers

- > 10.5 Common-Mode Rejection

- 10.6 Differential Pair with Active Load

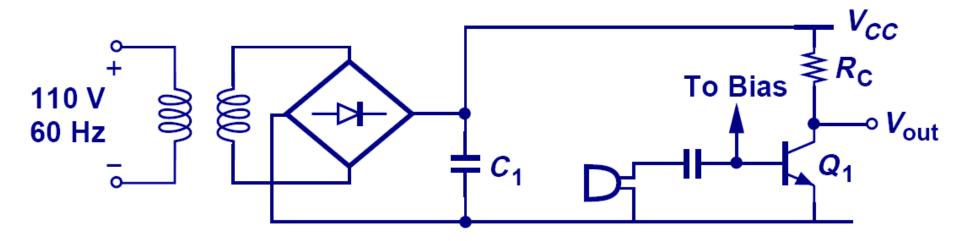

## **Audio Amplifier Example**

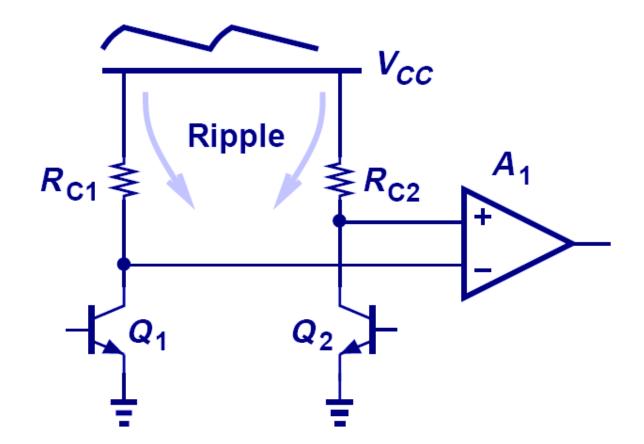

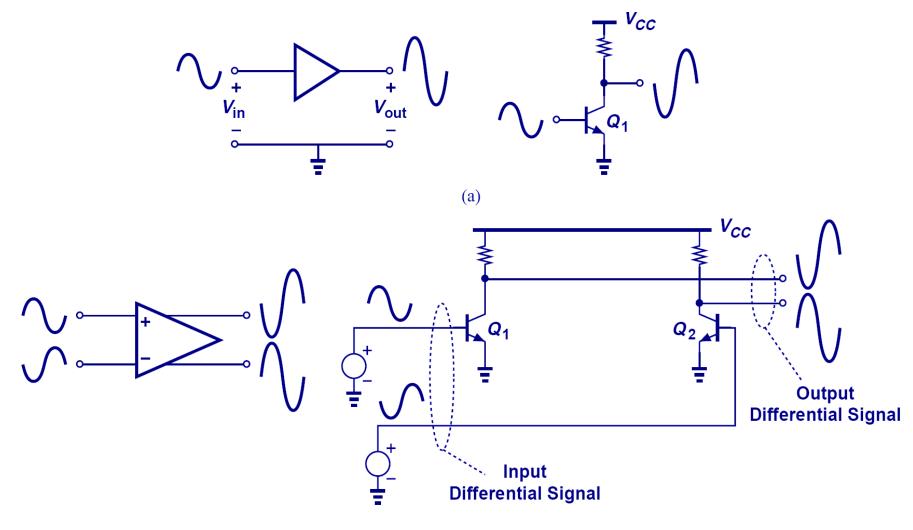

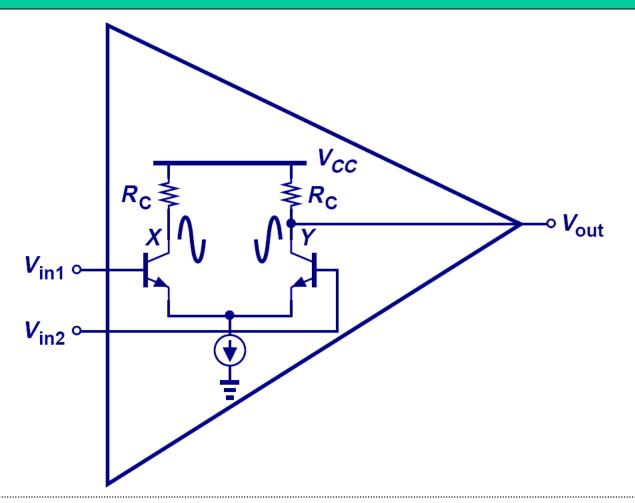

An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone.

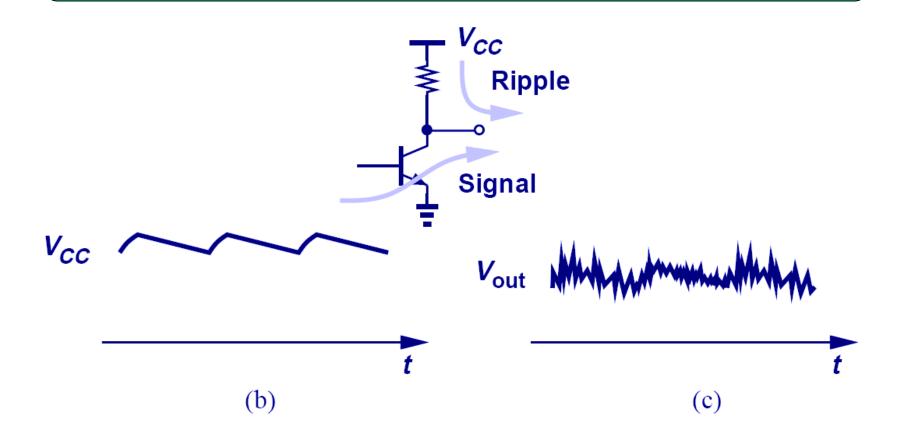

# "Humming" Noise in Audio Amplifier Example

However, V<sub>CC</sub> contains a ripple from rectification that leaks to the output and is perceived as a "humming" noise by the user.

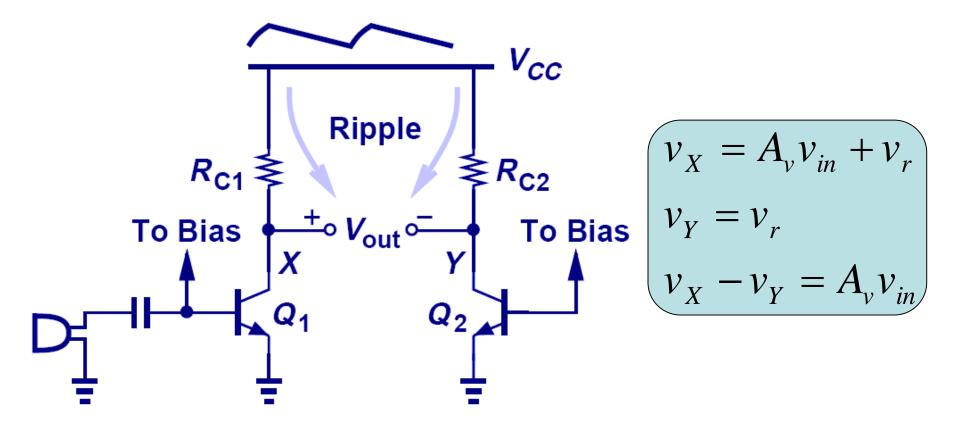

## **Supply Ripple Rejection**

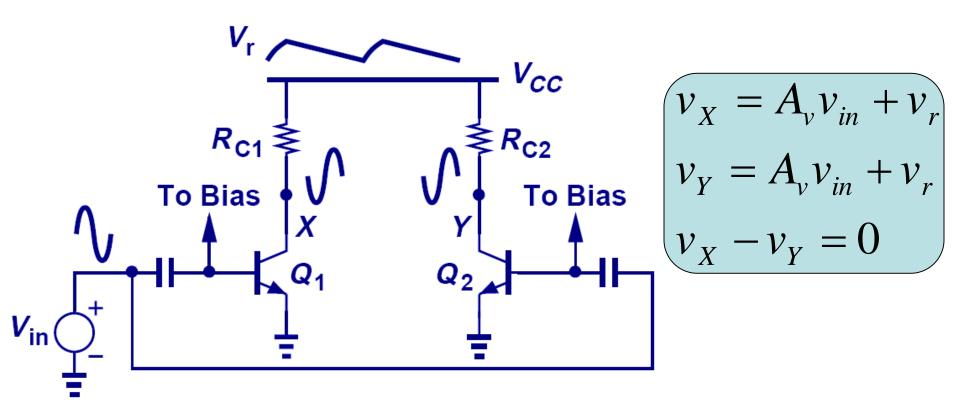

Since both node X and Y contain the same ripple, their difference will be free of ripple.

#### **Ripple-Free Differential Output**

Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed.

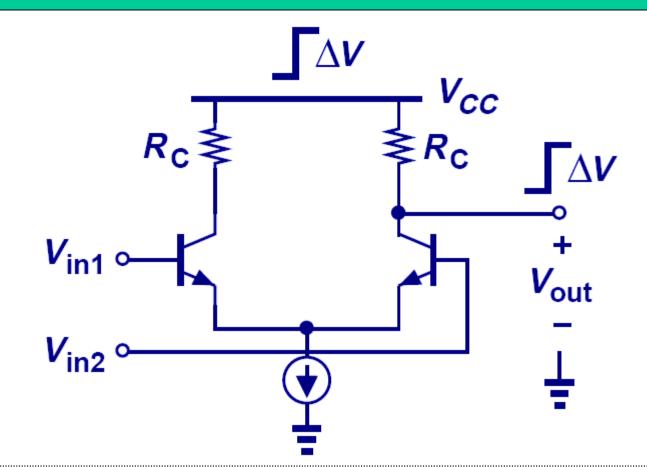

#### **Common Inputs to Differential Amplifier**

Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output.

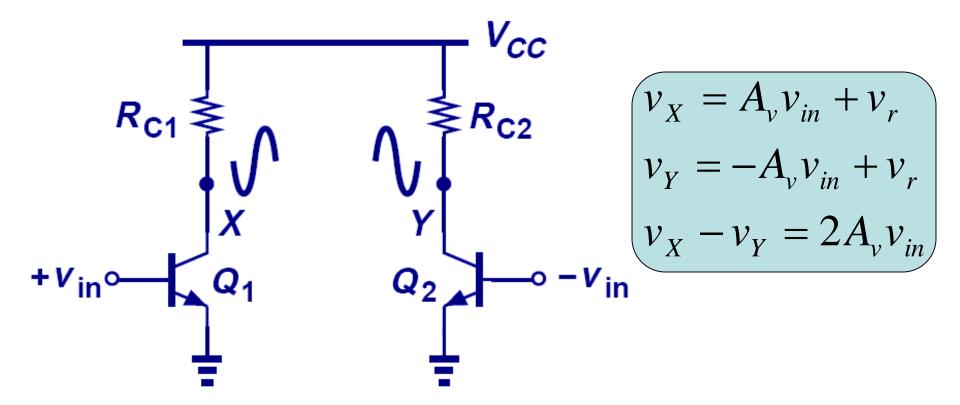

### **Differential Inputs to Differential Amplifier**

When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially.

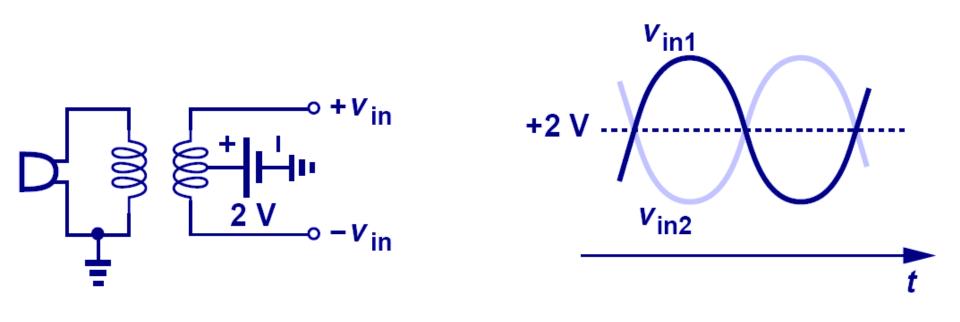

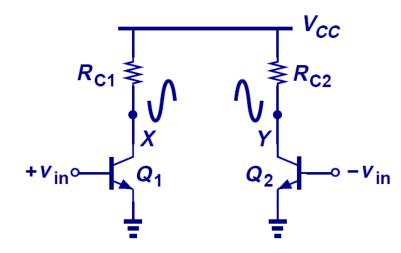

## **Differential Signals**

A pair of differential signals can be generated, among other ways, by a transformer.

Differential signals have the presents that they also as the

Differential signals have the property that they share the same average value (DC) to ground and AC values are equal in magnitude but opposite in phase.

#### **Single-ended vs. Differential Signals**

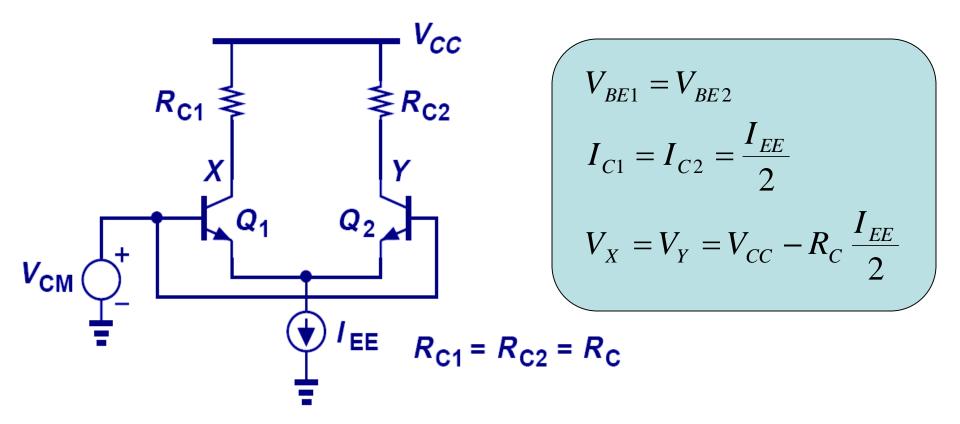

Determine the common-mode level at the output of the circuit shown in Fig. 10.3(b).

In the absence of signals,

$$V_X = V_Y = V_{CC} - R_C I_C$$

where  $R_C = R_{C1} = R_{C2}$  and  $I_C$  denotes the bias current of  $Q_1$  and  $Q_2$

Thus,

$$V_{CM} = V_{CC} - R_C I_C$$

Interestingly, the ripple affects  $V_{CM}$  but not the differential output.

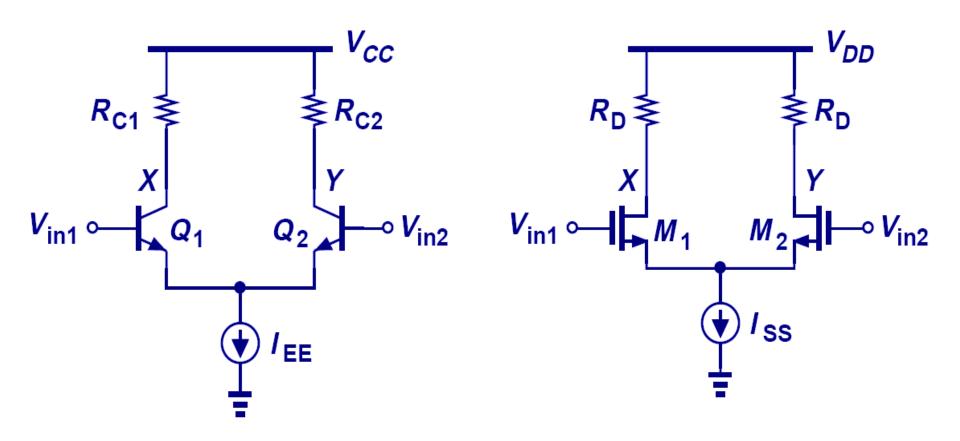

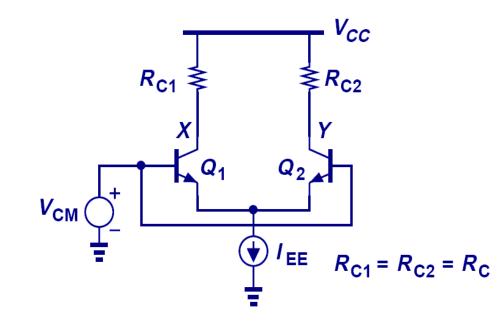

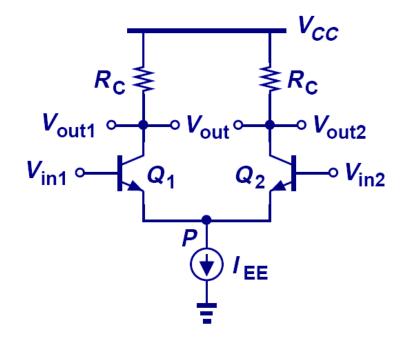

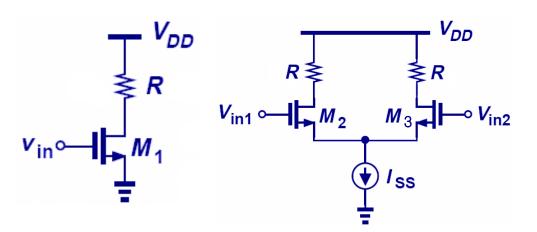

### **Differential Pair**

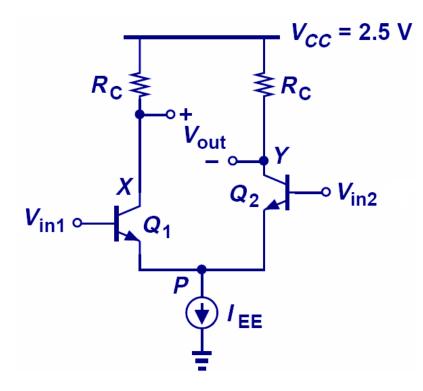

With the addition of a tail current, the circuits above operate as an elegant, yet robust differential pair.

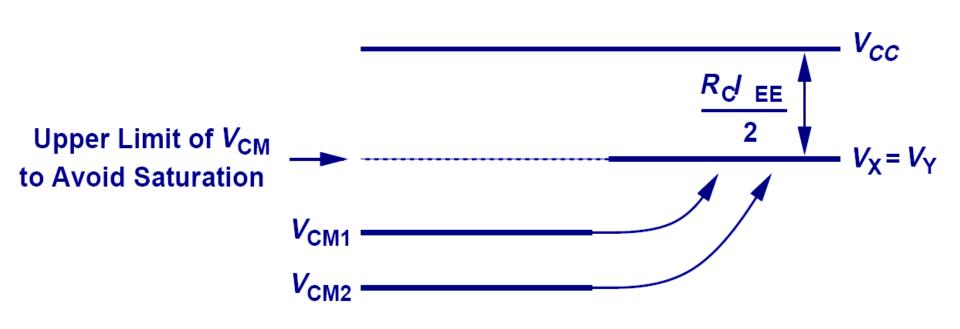

#### **Common-Mode Response**

To avoid saturation, the collector voltages must not fall below the base voltages:

$$V_{CC} - R_C \frac{I_{EE}}{2} \ge V_{CM}$$

A bipolar differential pair employs a load resistance of 1 kΩ and a tail current of 1 mA. How close to V<sub>cc</sub> can V<sub>cM</sub> be chosen?

$$V_{CC} - V_{CM} \ge R_C \frac{I_{EE}}{2} \ge 0.5 \text{V}$$

That is,  $V_{CM}$  must remain below  $V_{CC}$  by at least 0.5 V.

#### **Common-Mode Rejection**

Due to the fixed tail current source, the input commonmode value can vary without changing the output commonmode value.

#### **Differential Response I**

#### **Differential Response II**

#### **Differential Pair Characteristics**

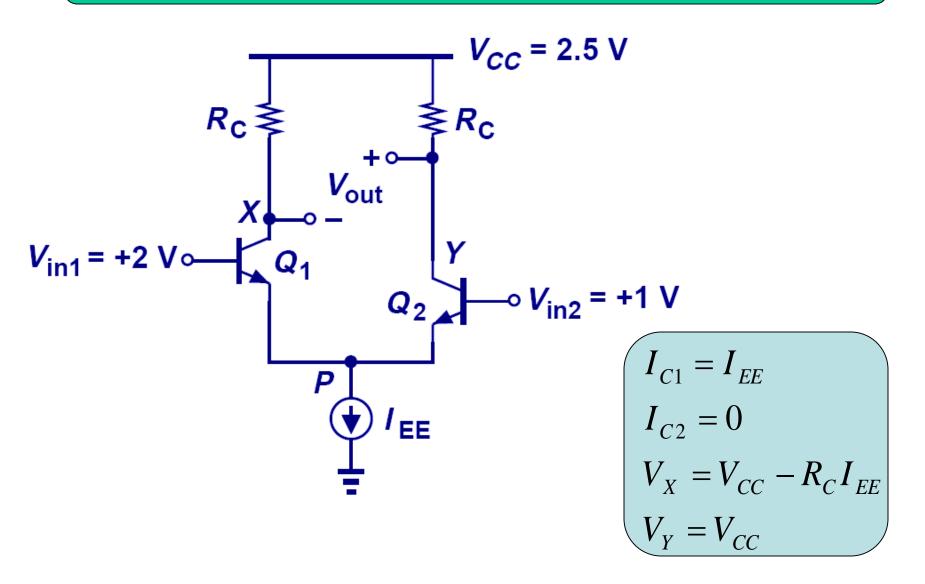

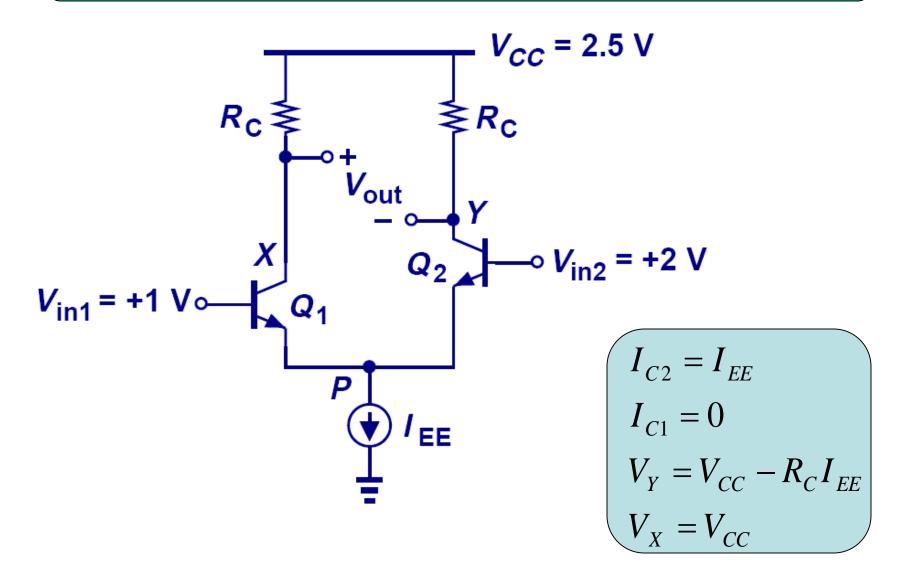

None-zero differential input produces variations in output currents and voltages, whereas common-mode input produces no variations.

A bipolar differential pair employs a tail current of 0.5 mA and a collector resistance of 1 kΩ. What is the maximum allowable base voltage if the differential input is large enough to completely steer the tail current? Assume V<sub>cc</sub>=2.5V.

Because  $I_{EE}$  is completely steered,  $V_{CC} - R_C I_{EE} = 2 V$  at one collector. To avoid saturation,  $V_B \le 2 V$ .

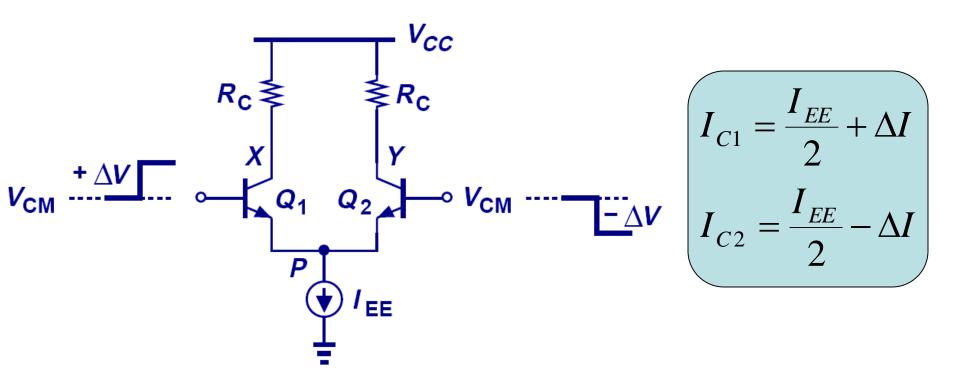

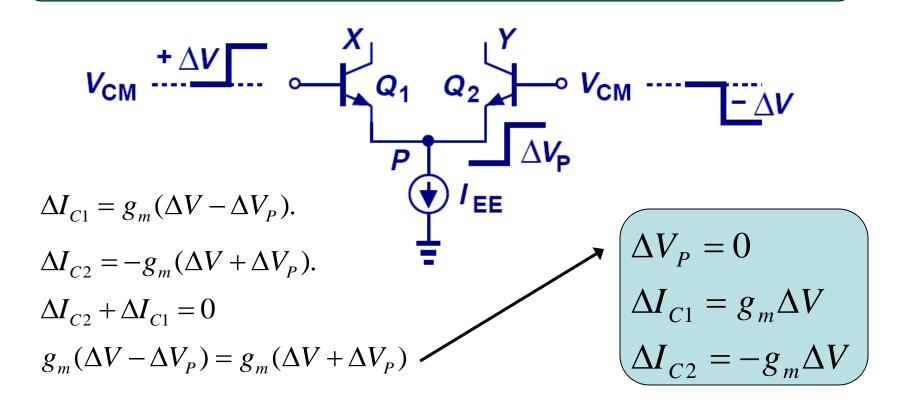

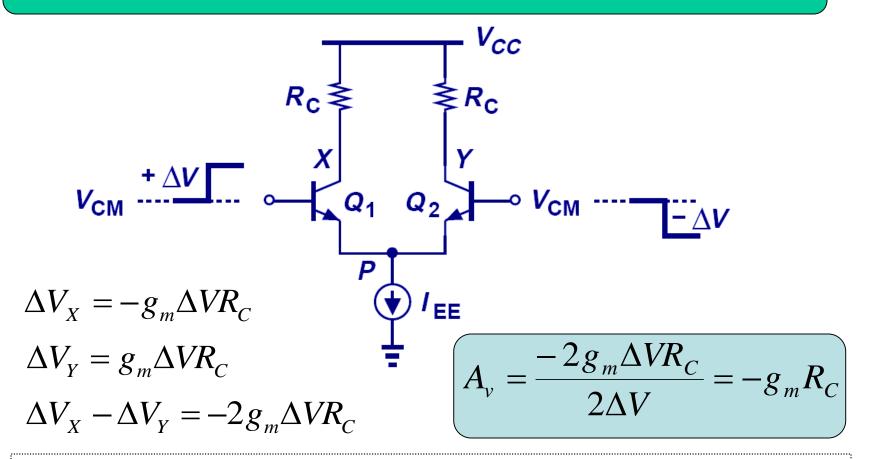

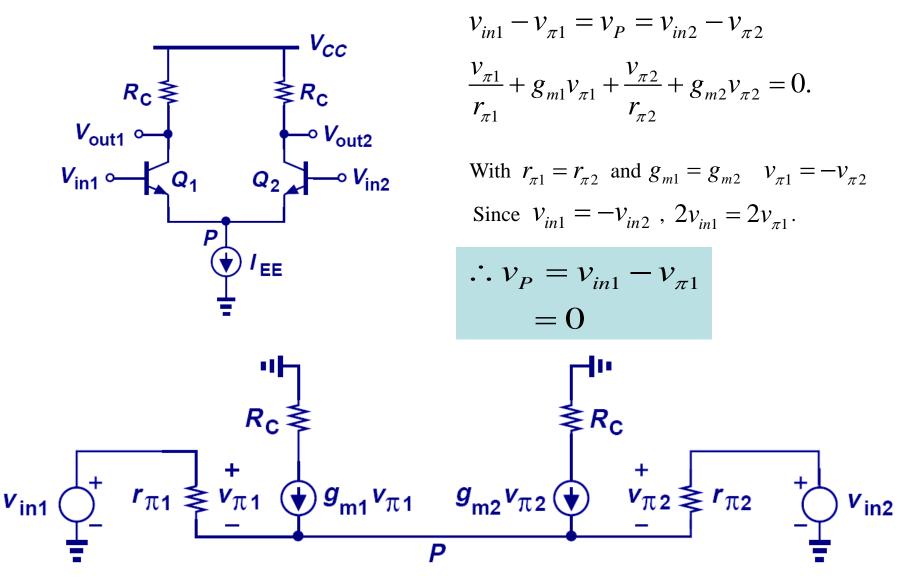

## **Small-Signal Analysis**

Since the input to Q<sub>1</sub> and Q<sub>2</sub> rises and falls by the same amount, and their emitters are tied together, the rise in I<sub>C1</sub> has the same magnitude as the fall in I<sub>C2</sub>.

### **Virtual Ground**

For small changes at inputs, the g<sub>m</sub>'s are the same, and the respective increase and decrease of I<sub>C1</sub> and I<sub>C2</sub> are the same, node P must stay constant to accommodate these changes. Therefore, node P can be viewed as AC ground.

## **Small-Signal Differential Gain**

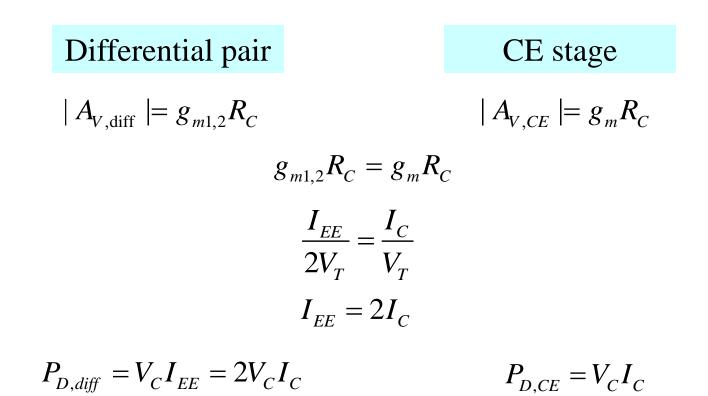

Since the output changes by -2g<sub>m</sub>∆VR<sub>C</sub> and input by 2∆V, the small signal gain is -g<sub>m</sub>R<sub>C</sub>, similar to that of the CE stage. However, to obtain same gain as the CE stage, power dissipation is doubled.

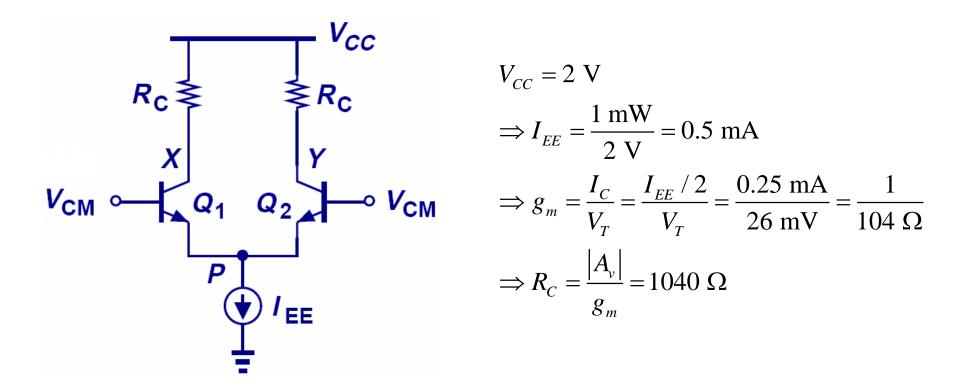

Design a bipolar differential pair for a gain of 10 and a power budget of 1mW with a supply voltage of 2V.

Compare the power dissipation of a bipolar differential pair with that of a CE stage if both circuits are designed for equal voltage gains, collector resistances, and supply voltages.

### **Large Signal Analysis**

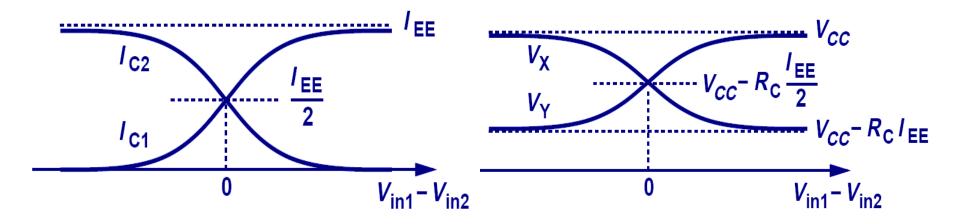

$V_{in1} - V_{in2} = V_{BE1} - V_{BE2}$  $=V_{T} \ln \frac{I_{C1}}{I_{S1}} - V_{T} \ln \frac{I_{C2}}{I_{S2}}$ and  $I_{C1} + I_{C2} = I_{FE}$  $\Rightarrow I_{C2} \exp \frac{V_{in1} - V_{in2}}{V_{T}} + I_{C2} = I_{EE}$  $\Rightarrow I_{C2} = \frac{I_{EE}}{1 + \exp \frac{V_{in1} - V_{in2}}{V_T}}$  $\Rightarrow I_{C1} = \frac{I_{EE} \exp \frac{V_{in1} - V_{in2}}{V_T}}{1 + \exp \frac{V_{in1} - V_{in2}}{V_T}}$

Determine the differential input voltage that steers 98% of the tail current to one transistor.

$$I_{C1} = 0.02I_{EE}$$

$$\approx I_{EE} \exp \frac{V_{in1} - V_{in2}}{V_T}$$

$$V_{in1} - V_{in2} \approx -3.91 \cdot V_T.$$

We often say a differential input of  $4 \cdot V_T$ is sufficient to turn one side of the bipolar pair nearly off.

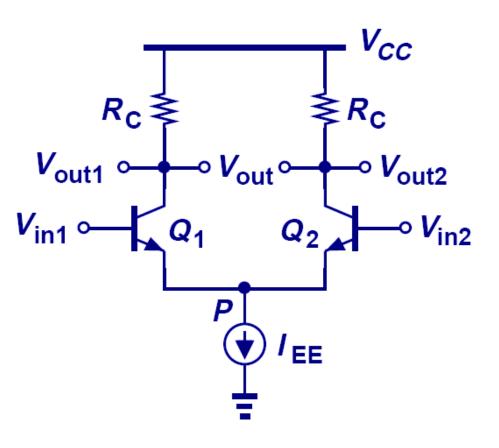

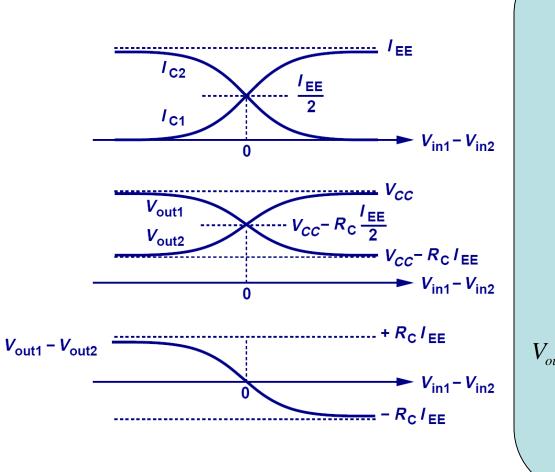

## **Input/Output Characteristics**

$$V_{out1} = V_{CC} - R_C I_{C1}$$

=  $V_{CC} - R_C \frac{I_{EE} \exp \frac{V_{in1} - V_{in2}}{V_T}}{1 + \exp \frac{V_{in1} - V_{in2}}{V_T}}$

$V_{out2} = V_{CC} - R_C I_{C2}$

=  $V_{CC} - R_C \frac{I_{EE}}{1 + \exp \frac{V_{in1} - V_{in2}}{V_T}}$

$V_{out1} - V_{out2} = R_C I_{EE} \frac{1 - \exp \frac{V_{in1} - V_{in2}}{V_T}}{1 + \exp \frac{V_{in1} - V_{in2}}{V_T}}$

$= -R_C I_{EE} \tanh \frac{V_{in1} - V_{in2}}{2 \cdot V_T}$

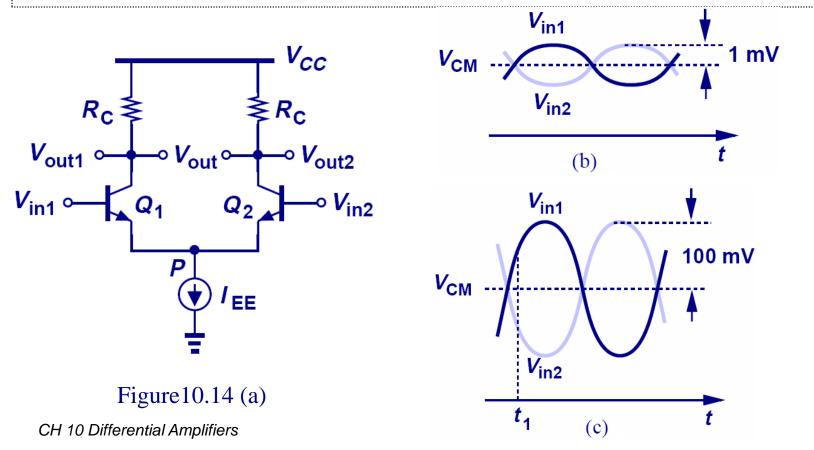

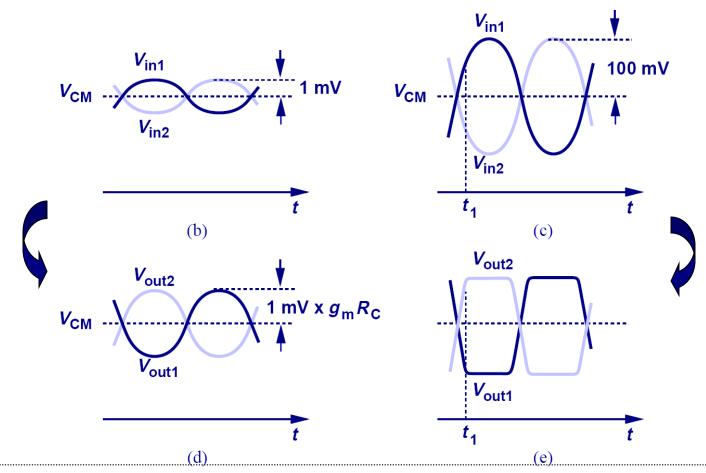

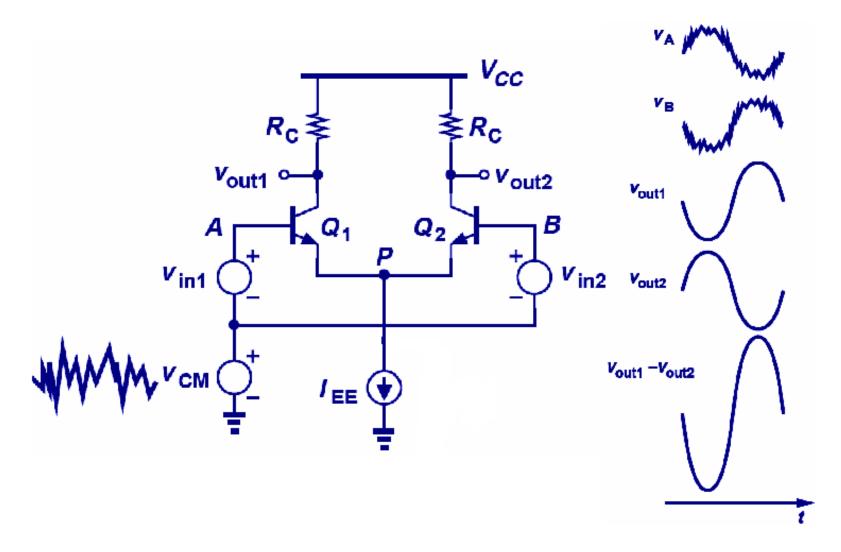

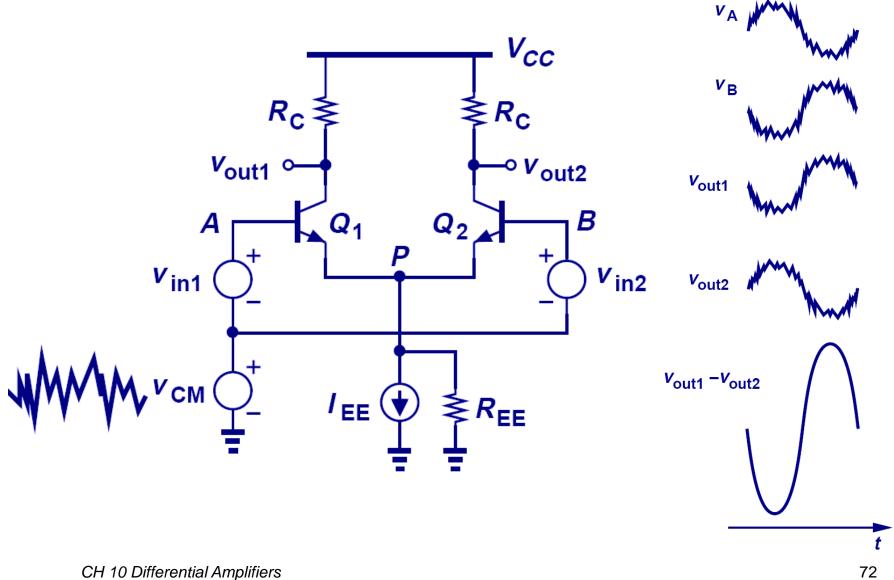

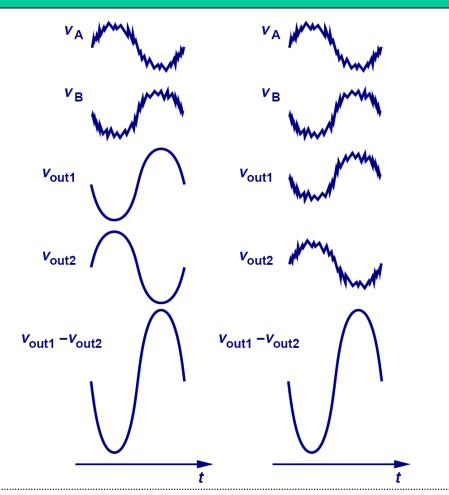

Sketch the output waveforms of the bipolar differential pair in Fig. 10.14(a) in response to the sinusoidal inputs shown in Figs. 10.14(b) and (c). Assume Q<sub>1</sub> and Q<sub>2</sub> remain in the forward active region.

### Example 10.9 (cont'd)

The left column operates in linear region (small-signal), whereas the right column operates in nonlinear region (large-signal).

### **Small-Signal Model**

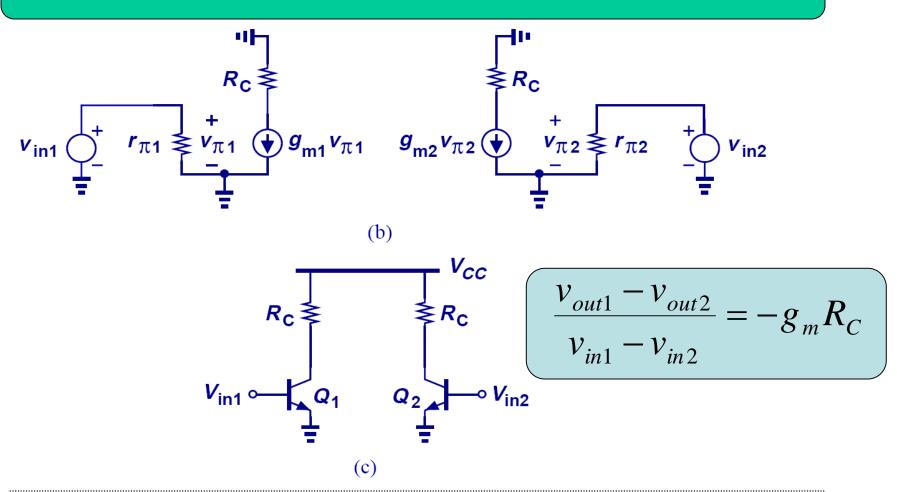

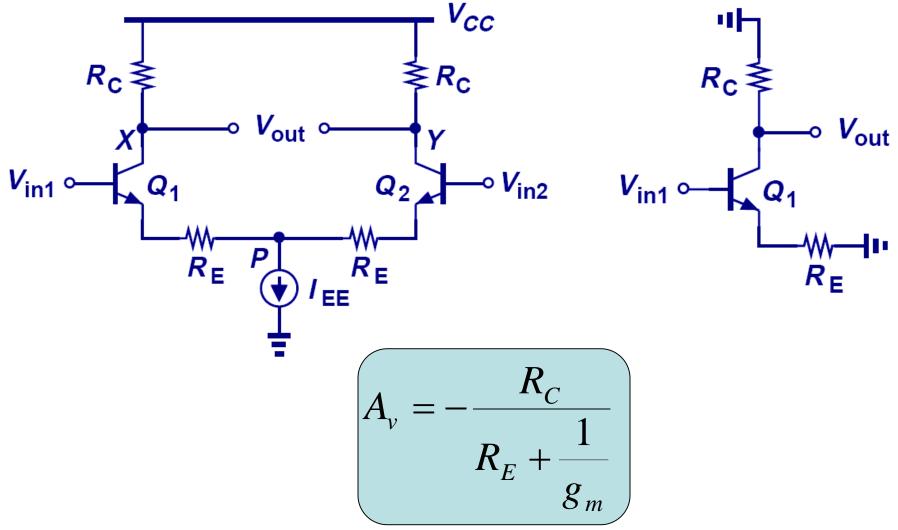

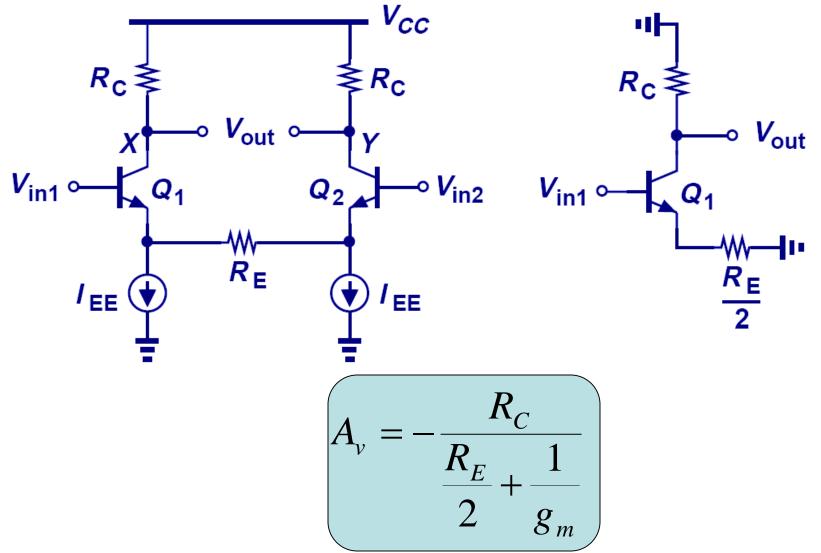

# **Half Circuits**

Since V<sub>P</sub> is grounded, we can treat the differential pair as two CE "half circuits", with its gain equal to one half circuit's single-ended gain.

Compute the differential gain of the circuit shown in Fig. 10.16(a), where ideal current sources are used as loads to maximize the gain.

$$\left(\frac{v_{out1} - v_{out2}}{v_{in1} - v_{in2}} = -g_m r_0\right)$$

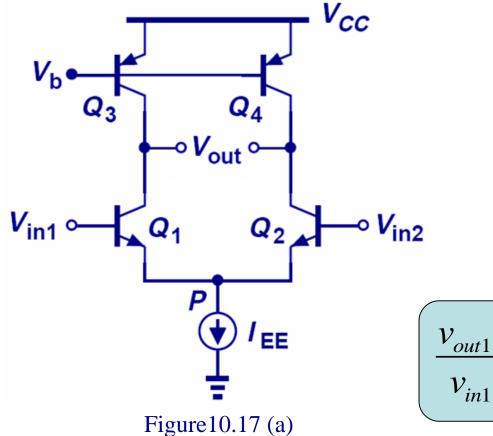

Figure 10.17(a) illustrates an implementation of the topology shown in Fig. 10.16(a). Calculate the differential voltage gain.

$V_{in1} \circ Q_1$

$$\frac{v_{out1} - v_{out2}}{v_{in1} - v_{in2}} = -g_m \left( r_{ON} \| r_{OP} \right)$$

CH 10 Differential Amplifiers

## **Extension of Virtual Ground**

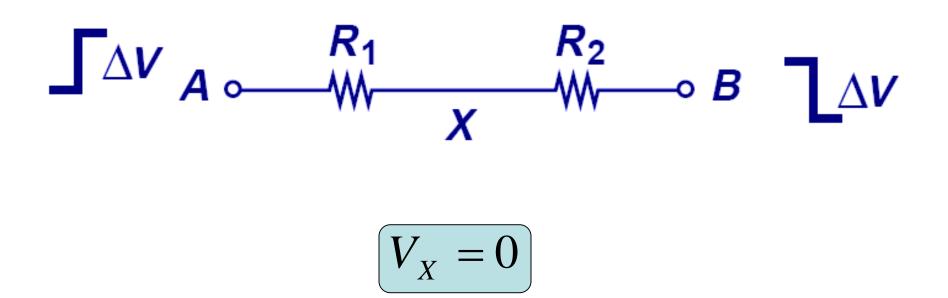

➢ It can be shown that if  $R_1 = R_2$ , and points A and B go up and down by the same amount respectively, V<sub>X</sub> does not move. This property holds for any other node that appears on the axis of symmetry.

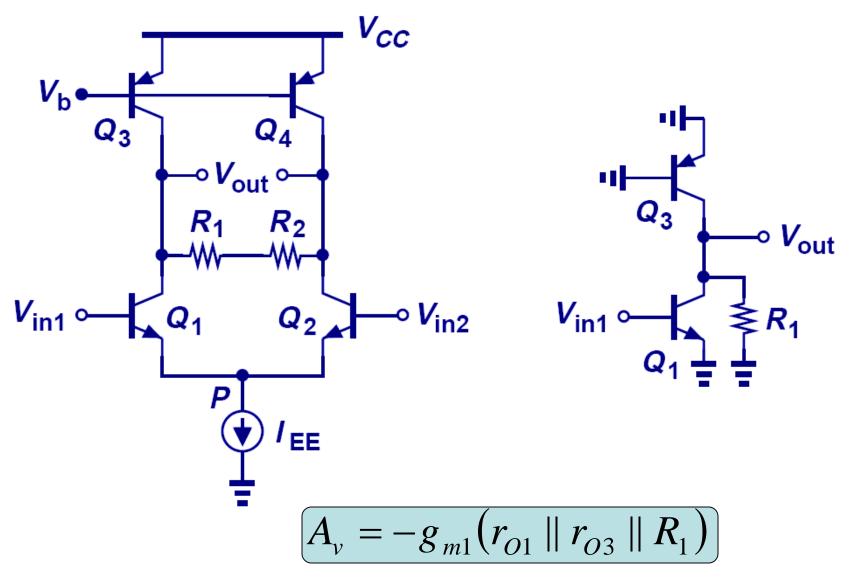

#### Half Circuit Example I

#### Half Circuit Example II

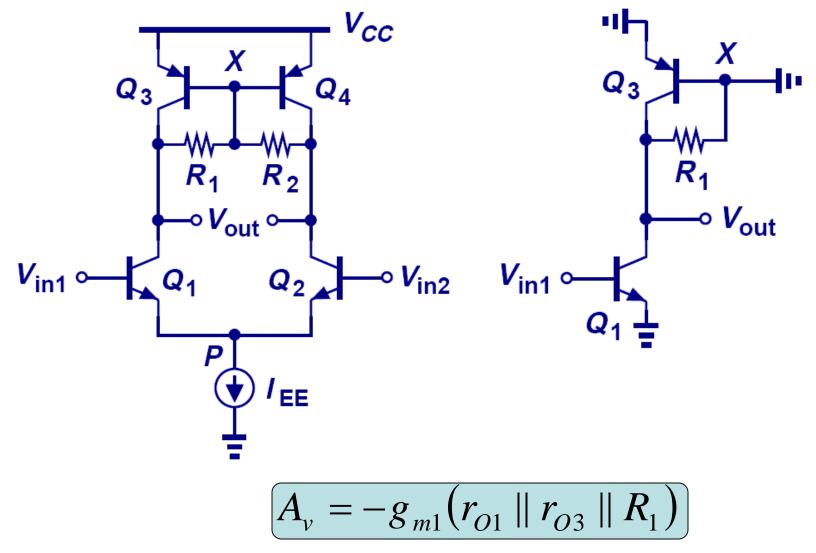

## Half Circuit Example III

# Half Circuit Example IV

CH 10 Differential Amplifiers

### I/O Impedances

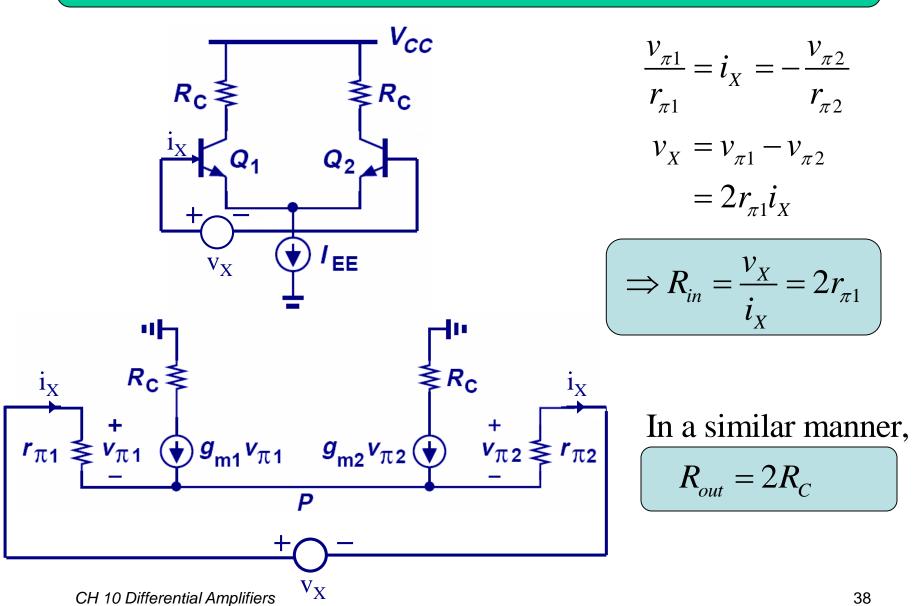

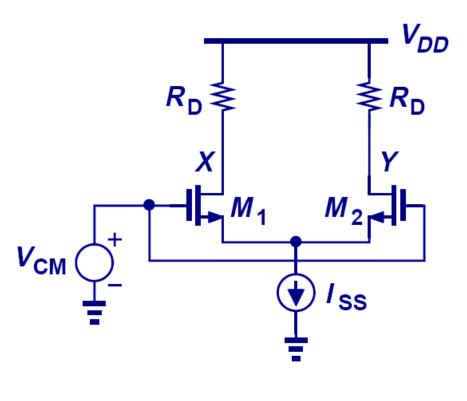

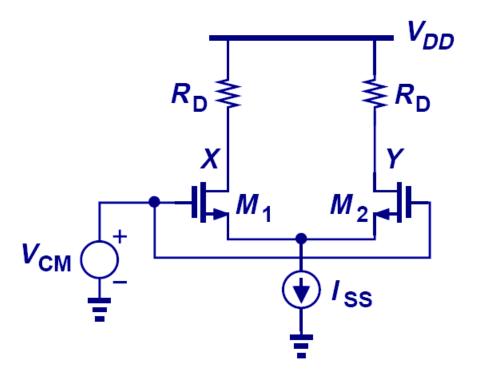

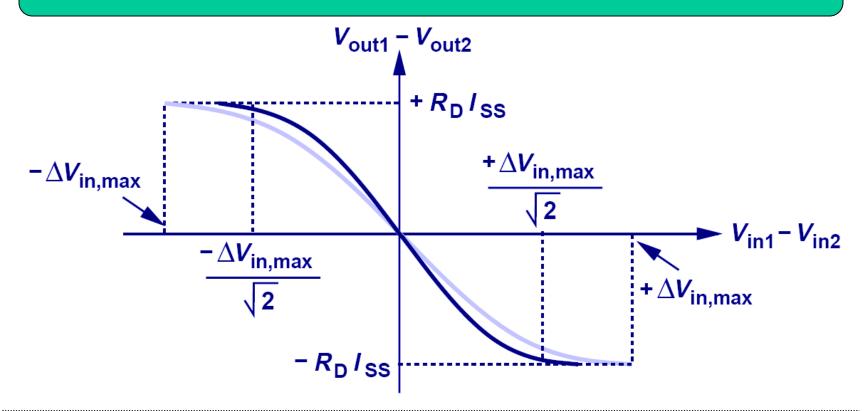

# **MOS Differential Pair's Common-Mode Response**

Similar to its bipolar counterpart, MOS differential pair produces zero differential output as V<sub>CM</sub> changes.

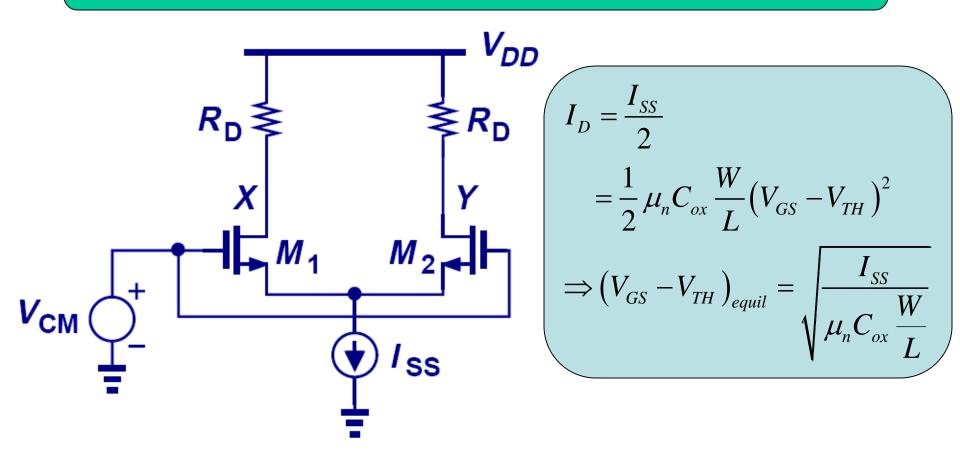

# **Equilibrium Overdrive Voltage**

The equilibrium overdrive voltage is defined as the overdrive voltage seen by M<sub>1</sub> and M<sub>2</sub> when both of them carry a current of I<sub>SS</sub>/2.

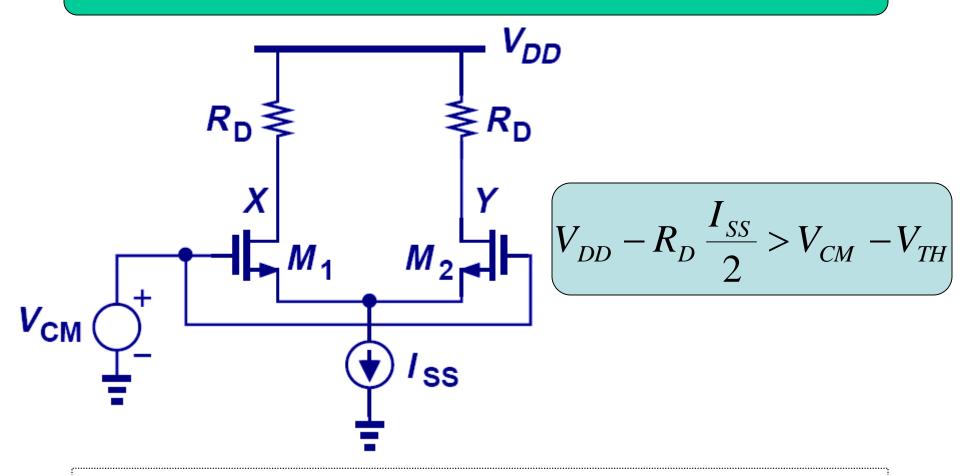

# **Minimum Common-mode Output Voltage**

In order to maintain M<sub>1</sub> and M<sub>2</sub> in saturation, the common-mode output voltage cannot fall below the value above.

This value usually limits voltage gain.

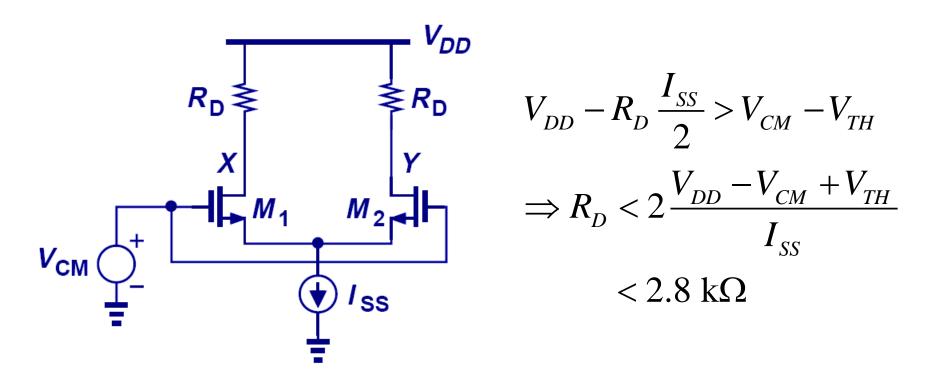

> A MOS differential pair is driven with an input CM level of 1.6V. If  $I_{SS}$ =0.5mA,  $V_{TH}$ =0.5 V, and  $V_{DD}$ =1.8 V, what is the maximum allowable load resistance?

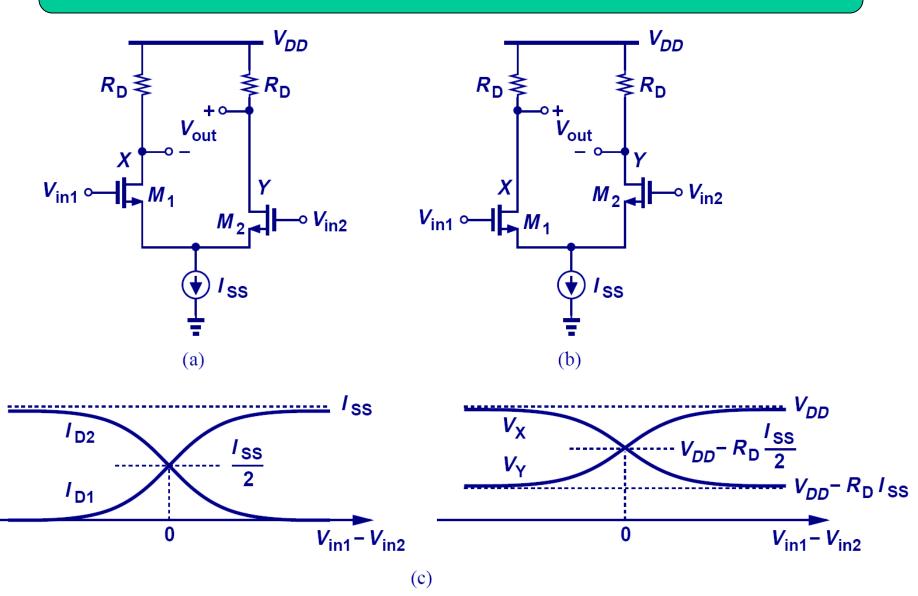

#### **Differential Response**

CH 10 Differential Amplifiers

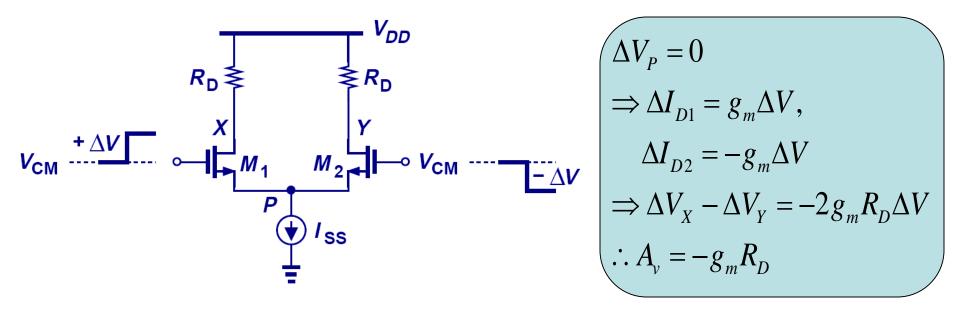

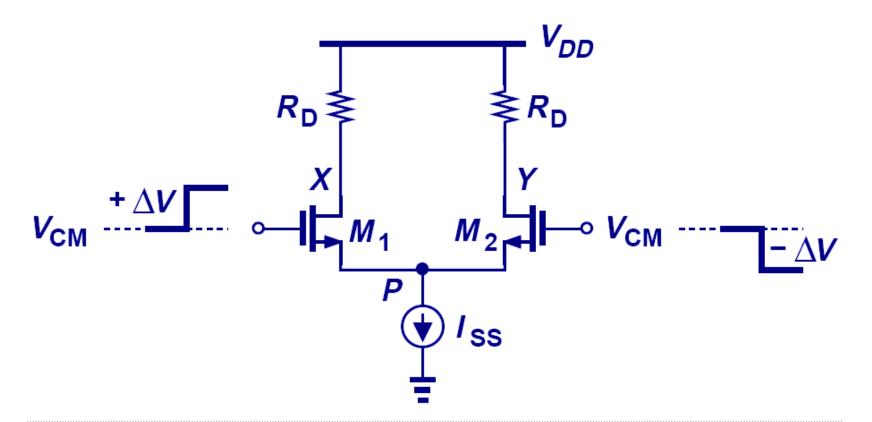

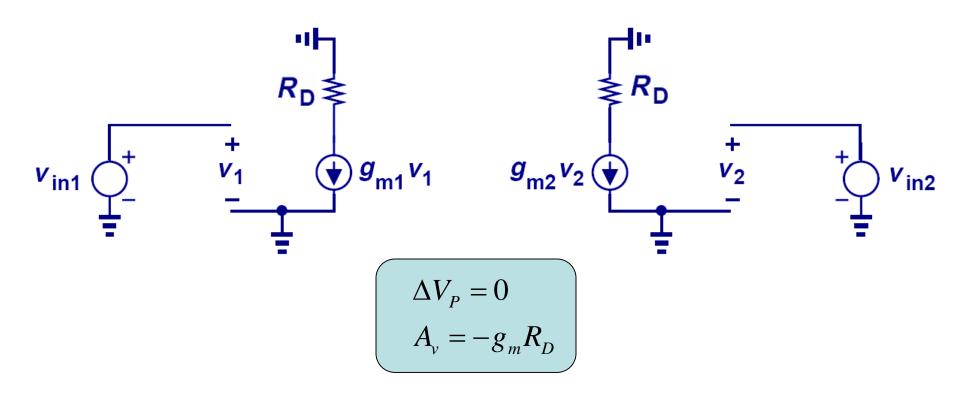

## **Small-Signal Response**

Similar to its bipolar counterpart, the MOS differential pair exhibits the same virtual ground node and small signal gain.

# **Power and Gain Tradeoff**

In order to obtain the same gain as a CS stage, a MOS differential pair must dissipate twice the amount of current. This power and gain tradeoff is also echoed in its bipolar counterpart.

> Design an NMOS differential pair for a voltage gain of 5 and a power budget of 2 mW subject to the condition that the stage following the differential pair requires an output CM level of at least 1.6V. Assume  $\mu_n C_{ox}$ =100  $\mu$ A/V<sup>2</sup>,  $\lambda$ =0, and  $V_{DD}$ = 1.8 V.

$$I_{SS} = \frac{2 \text{ mW}}{1.8 \text{ V}} = 1.11 \text{ mA}$$

$$V_{CM,out} = V_{DD} - R_D \frac{I_{SS}}{2} \ge 1.6 \text{ V}$$

$$\Rightarrow R_D \le 360 \Omega$$

For

$$R_D = 360 \Omega$$

,

$g_m = \frac{A_v}{R_D} = \frac{5}{360 \Omega} = \sqrt{2\mu_n C_{ox}} \frac{W}{L} \frac{I_{SS}}{2}$

$\Rightarrow \frac{W}{L} = 1738$

What is the maximum allowable input CM level in the previous example if V<sub>TH</sub>=0.4 V?

To guarantee that  $M_1$  and  $M_2$ operate in saturation,  $V_{CM,in} < V_{DD} - R_D \frac{I_{SS}}{2} + V_{TH}$  $< V_{CM,out} + V_{TH}$ .

Thus,  $V_{CM,in} < 2 \text{ V}$

The common-source stage and the differential pair shown in Fig. 10.28 incorporate equal load resistors. If the two circuits are designed for the same voltage gain and the same supply voltage, discuss the choice of (a) transistor dimensions for a given power budget, (b) power dissipation for given transistor dimensions.

Figure10.28

CH 10 Differential Amplifiers

(a) for same power budget,

$$I_{D1} = I_{SS} = 2I_{D2} = 2I_{D3}$$

$$\Rightarrow \frac{W_1}{L_1} = \frac{1}{2} \frac{W_2}{L_2} = \frac{1}{2} \frac{W_3}{L_3}$$

$$\left( \because g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} \right)$$

(b) for same transistor dimensions,

$$I_{SS} = 2I_{D1}$$

$$\Rightarrow P_{diff} = 2P_{CS}$$

48

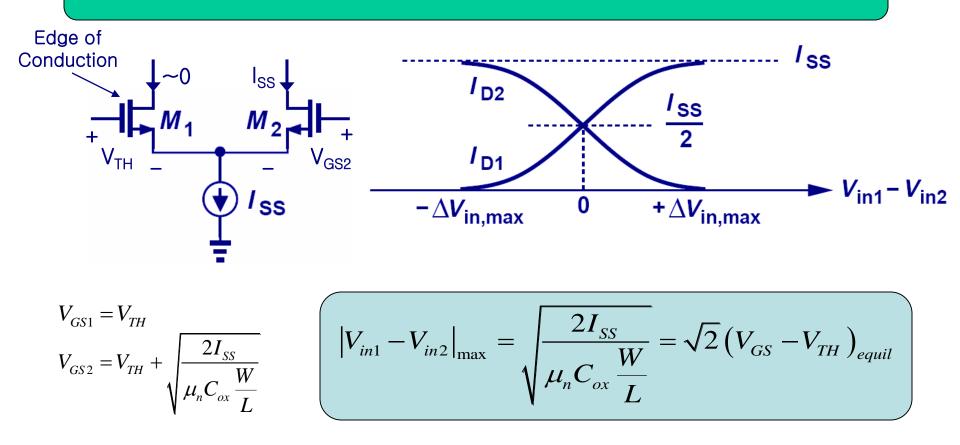

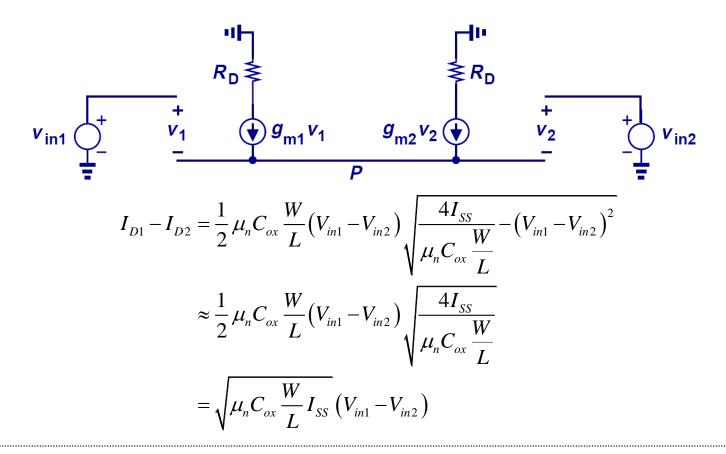

## **MOS Differential Pair's Large-Signal Response**

$$V_{in1} - V_{GS1} = V_{in2} - V_{GS2}.$$

$$I_{D1} + I_{D2} = I_{SS}.$$

$$I_{D} = (1/2)\mu_{n}C_{ox}(W/L)(V_{GS} - V_{TH})^{2}.$$

$$\Rightarrow V_{GS} = V_{TH} + \sqrt{\frac{2I_{D}}{\mu_{n}C_{ox}\frac{W}{L}}}.$$

$$\Rightarrow V_{in1} - V_{in2} = V_{GS1} - V_{GS2}$$

$$= \sqrt{\frac{2}{\mu_{n}C_{ox}\frac{W}{L}}}(\sqrt{I_{D1}} - \sqrt{I_{D2}}).$$

Goal is to obtain  $I_{D1}$  -  $I_{D2}$

# MOS Differential Pair's Large-Signal Response (cont'd)

$$(V_{in1} - V_{in2})^{2} = \frac{2}{\mu_{n}C_{ox}}\frac{W}{L}(I_{D1} + I_{D2} - 2\sqrt{I_{D1}I_{D2}})$$

$$= \frac{2}{\mu_{n}C_{ox}}\frac{W}{L}(I_{SS} - 2\sqrt{I_{D1}I_{D2}}).$$

$$\Rightarrow 4\sqrt{I_{D1}I_{D2}} = 2I_{SS} - \mu_n C_{ox} \frac{W}{L} (V_{in1} - V_{in2})^2$$

$$\Rightarrow 16I_{D1}I_{D2} = \left[2I_{SS} - \mu_n C_{ox} \frac{W}{L} (V_{in1} - V_{in2})^2\right]^2$$

$$\Rightarrow 16I_{D1}(I_{SS} - I_{D1}) = \left[2I_{SS} - \mu_n C_{ox} \frac{W}{L} (V_{in1} - V_{in2})^2\right]^2$$

# MOS Differential Pair's Large-Signal Response (cont'd)

$$\Rightarrow 16I_{D1}^{2} - 16I_{SS}I_{D1} + \left[2I_{SS} - \mu_{n}C_{ox}\frac{W}{L}(V_{in1} - V_{in2})^{2}\right]^{2} = 0$$

$$\Rightarrow I_{D1} = \frac{I_{SS}}{2} \pm \frac{1}{4}\sqrt{4I_{SS}^{2} - \left[\mu_{n}C_{ox}\frac{W}{L}(V_{in1} - V_{in2})^{2} - 2I_{SS}\right]^{2}}$$

$$= \frac{I_{SS}}{2} + \frac{V_{in1} - V_{in2}}{4}\sqrt{\mu_{n}C_{ox}\frac{W}{L}\left[4I_{SS} - \mu_{n}C_{ox}\frac{W}{L}(V_{in1} - V_{in2})^{2}\right]}$$

$$\Rightarrow I_{D2} = \frac{I_{SS}}{2} + \frac{V_{in2} - V_{in1}}{4}\sqrt{\mu_{n}C_{ox}\frac{W}{L}\left[4I_{SS} - \mu_{n}C_{ox}\frac{W}{L}(V_{in2} - V_{in1})^{2}\right]}$$

(:: the symmetry of the circuit)

$$\left(I_{D1} - I_{D2} = \frac{1}{2}\mu_{n}C_{ox}\frac{W}{L}\left(V_{in1} - V_{in2}\right)\sqrt{\frac{4I_{SS}}{\mu_{n}C_{ox}\frac{W}{L}} - (V_{in1} - V_{in2})^{2}}\right)$$

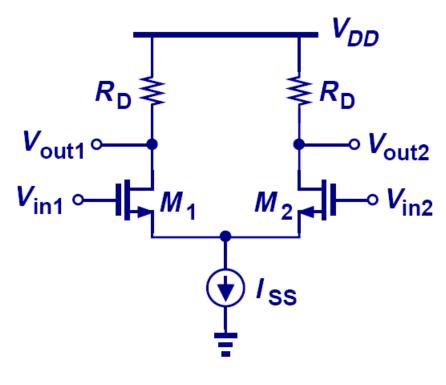

# **Maximum Differential Input Voltage**

There exists a finite differential input voltage that completely steers the tail current from one transistor to the other. This value is known as the maximum differential input voltage.

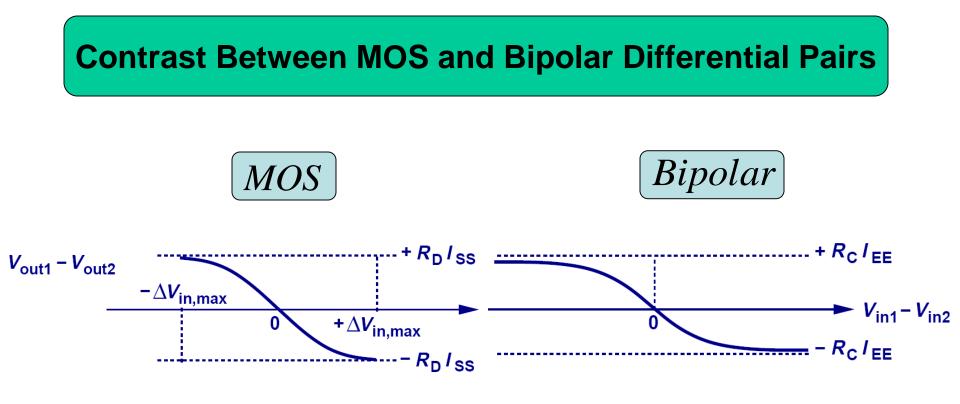

In a MOS differential pair, there exists a finite differential input voltage to completely switch the current from one transistor to the other, whereas, in a bipolar pair that voltage is infinite.

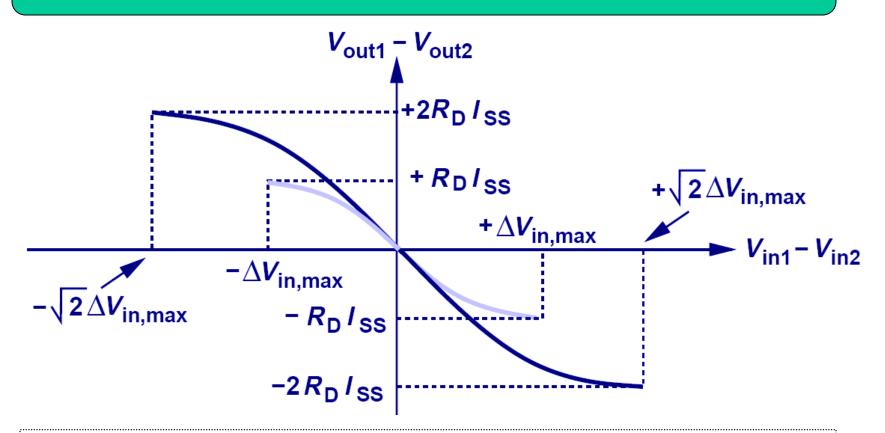

# The effects of Doubling the Tail Current

Since  $I_{SS}$  is doubled and W/L is unchanged, the equilibrium overdrive voltage for each transistor must increase by  $\sqrt{2}$  to accommodate this change, thus  $\Delta V_{in,max}$  increases by  $\sqrt{2}$  as well. Moreover, since  $I_{SS}$  is doubled, the differential output swing will double.

## The effects of Doubling W/L

Since W/L is doubled and the tail current remains unchanged, the equilibrium overdrive voltage will be lowered by  $\sqrt{2}$  to accommodate this change, thus  $\Delta V_{in,max}$  will be lowered by as well. Moreover, the differential output swing will remain unchanged since neither  $I_{SS}$  nor  $R_D$  has changed

> Design an NMOS differential pair for a power budget of 3 mW and  $\Delta V_{in,max}$ =500 mV. Assume  $\mu_n C_{ox}$ =100  $\mu$ A/V<sup>2</sup> and  $V_{DD}$ =1.8 V.

$$I_{SS} = \frac{3 \text{ mW}}{1.8 \text{ V}} = 1.67 \text{ mA}$$

From  $|V_{in1} - V_{in2}|_{\text{max}} = \sqrt{\frac{2I_{SS}}{\mu_n C_{ox}} \frac{W}{L}}$

$\frac{W}{L} = \frac{2I_{SS}}{\mu_n C_{ox} \Delta V_{in,\text{max}}^2} = 133.6$

$R_D$  is determined by the required voltage gain.

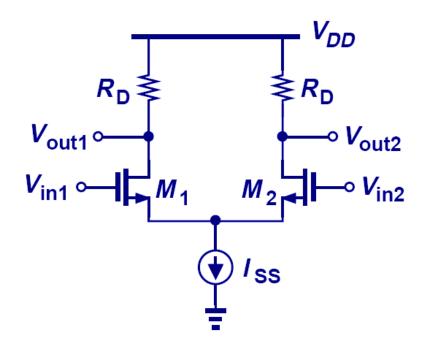

# **Small-Signal Analysis of MOS Differential Pair**

▶ When the input differential signal is small compared to  $[4I_{SS}/\mu_nC_{ox}(W/L)]^{1/2}$ , the output differential current is linearly proportional to it, and small-signal model can be applied.

# **Virtual Ground and Half Circuit**

Applying the same analysis as the bipolar case, we will arrive at the same conclusion that node P will not move for small input signals and the concept of half circuit can be used to calculate the gain.

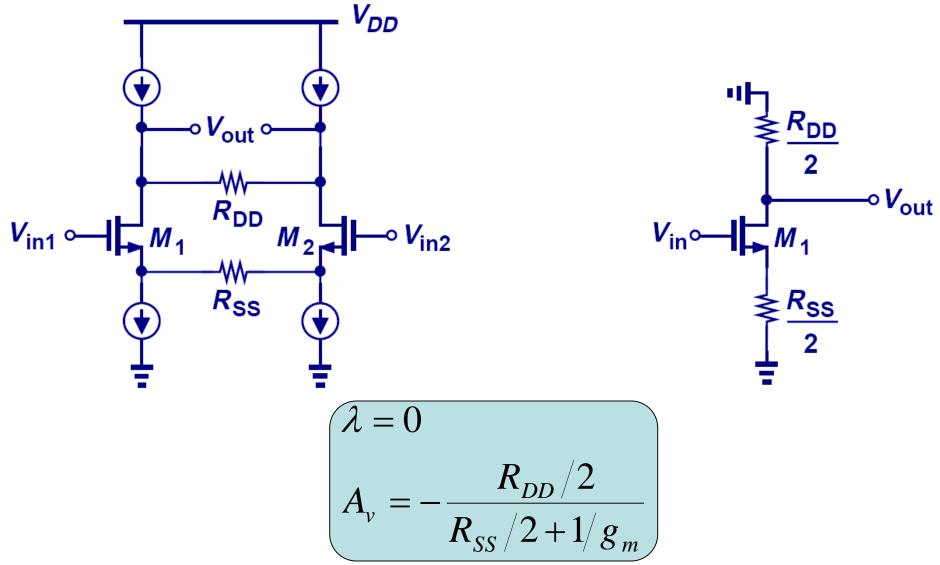

### **MOS Differential Pair Half Circuit Example I**

CH 10 Differential Amplifiers

## **MOS Differential Pair Half Circuit Example II**

CH 10 Differential Amplifiers

# **MOS Differential Pair Half Circuit Example III**

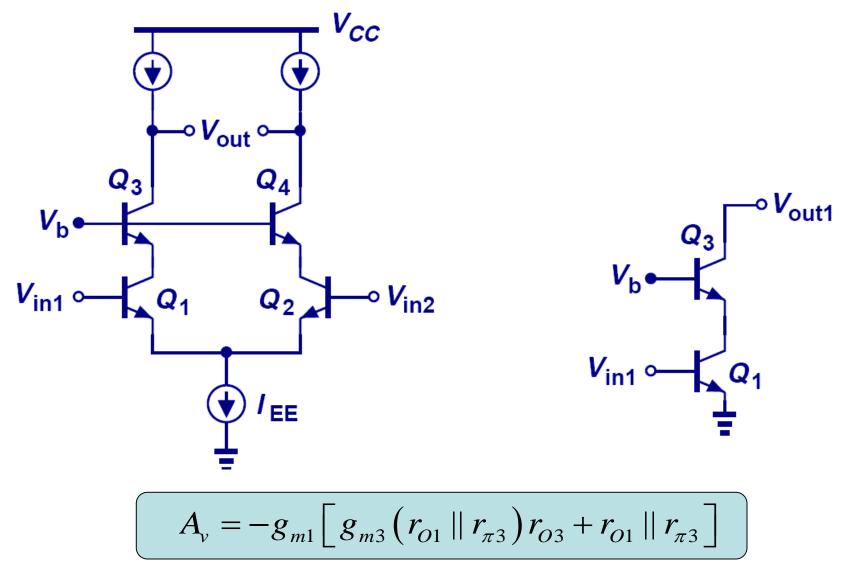

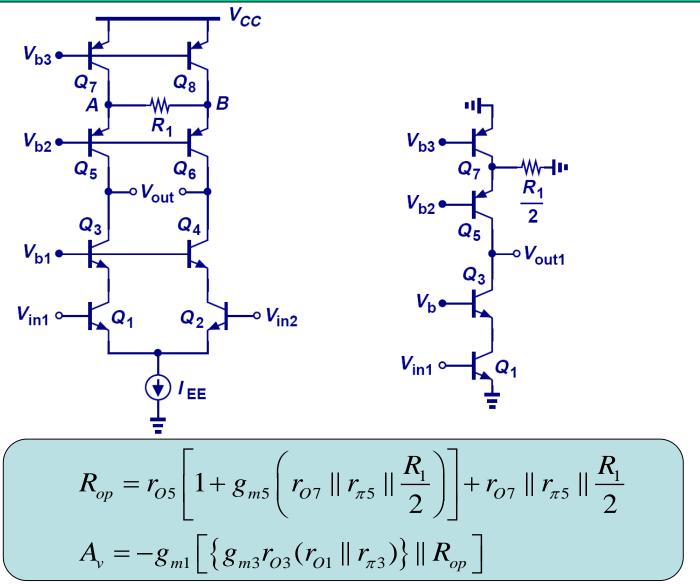

### **Bipolar Cascode Differential Pair**

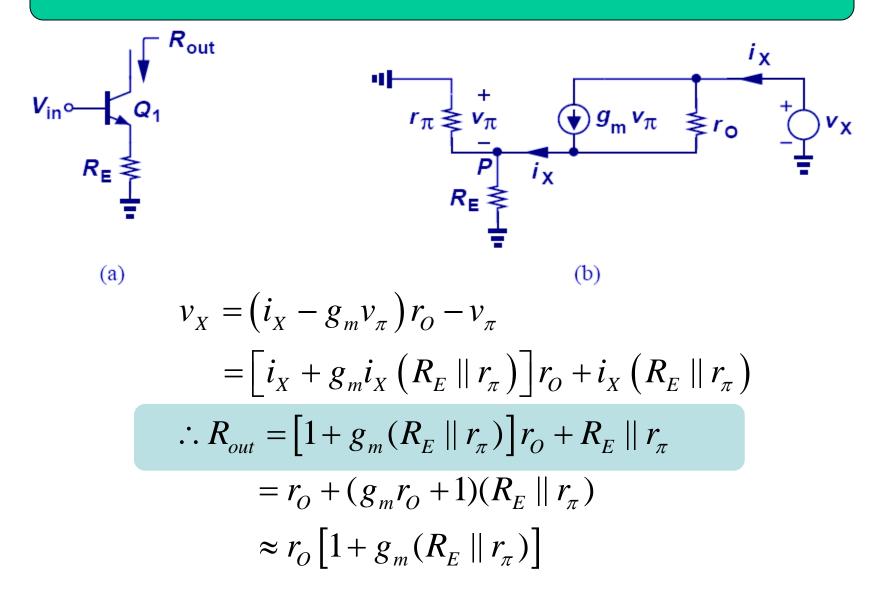

## **Output Impedance of CE Stage with Degeneration**

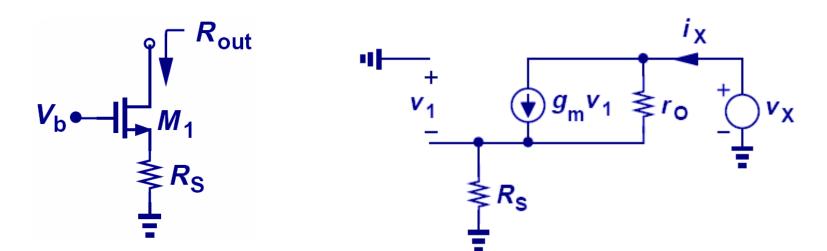

## **Output Impedance of CS Stage with Degeneration**

$$i_{X} - g_{m}v_{1} = i_{X} - g_{m}(-i_{X}R_{S}) = i_{X} + g_{m}i_{X}R_{S}$$

$$\Rightarrow r_{O}(i_{X} + g_{m}i_{X}R_{S}) + i_{X}R_{S} = v_{X}$$

$$\therefore R_{out} = r_{O}(1 + g_{m}R_{S}) + R_{S}$$

$$= (1 + g_{m}r_{O})R_{S} + r_{O}$$

$$\approx g_{m}r_{O}R_{S} + r_{O}$$

#### **Bipolar Telescopic Cascode**

CH 10 Differential Amplifiers

### **Example: Bipolar Telescopic Parasitic Resistance**

CH 10 Differential Amplifiers

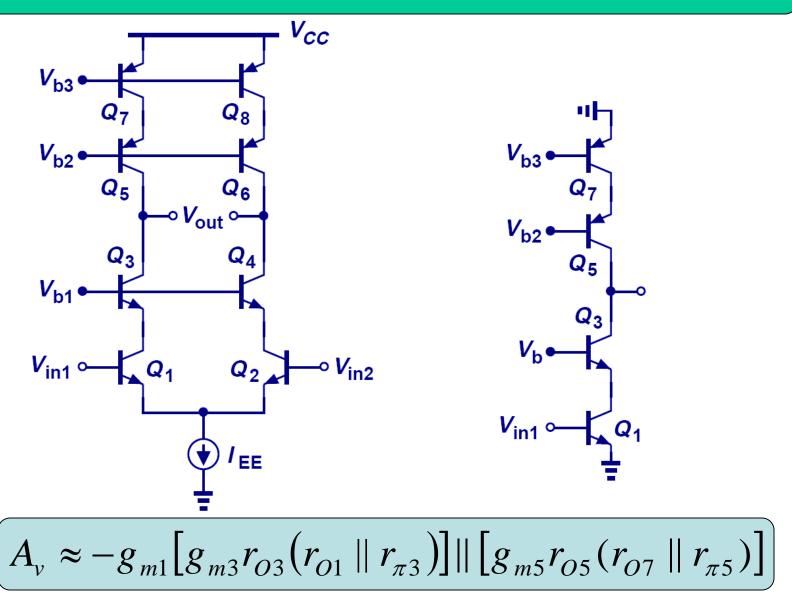

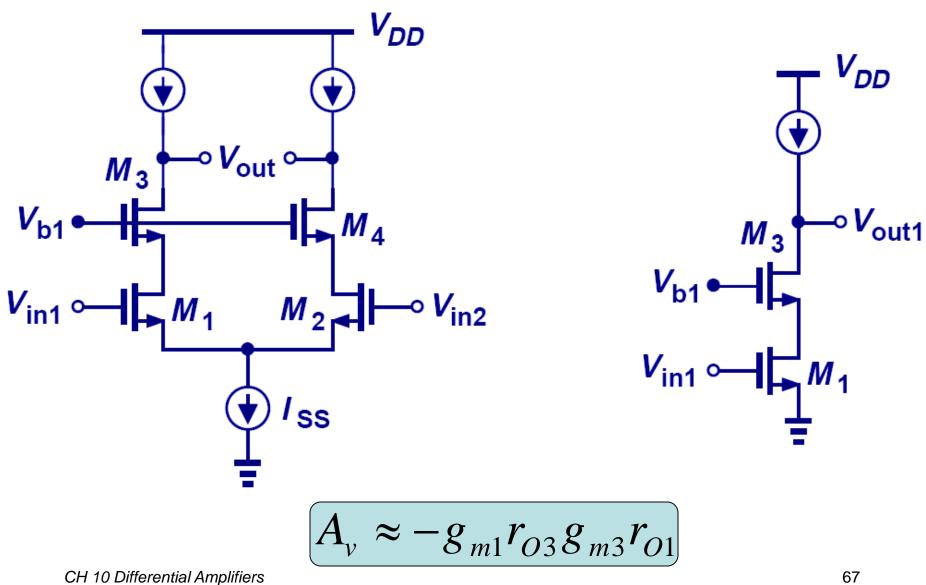

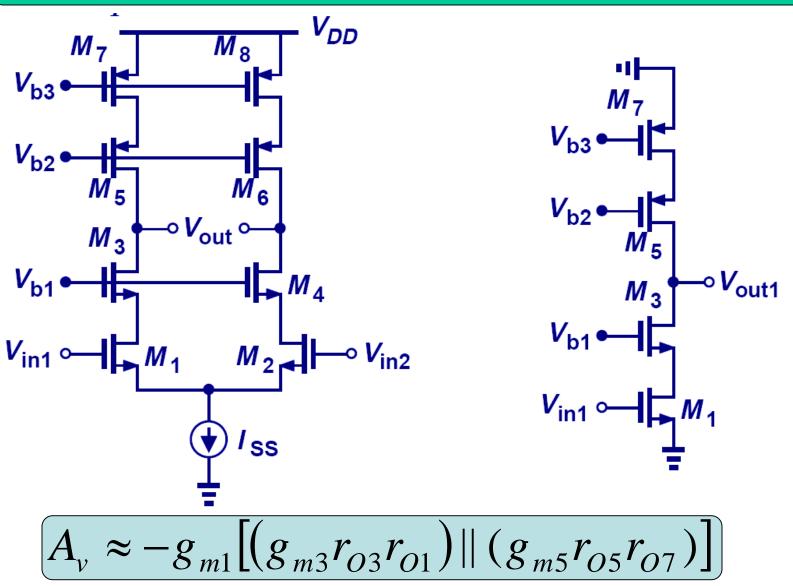

### **MOS Cascode Differential Pair**

### **MOS Telescopic Cascode**

### **Example: MOS Telescopic Parasitic Resistance**

CH 10 Differential Amplifiers

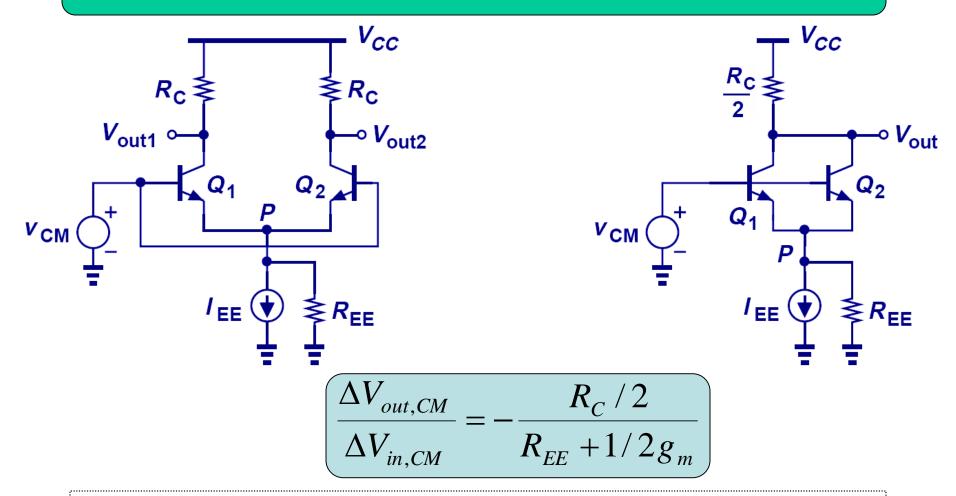

# **Effect of Finite Tail Impedance**

If the tail current source is not ideal, then when a input CM voltage is applied, the currents in Q<sub>1</sub> and Q<sub>2</sub> and hence output CM voltage will change.

### Input CM Noise with Ideal Tail Current

# Input CM Noise with Non-ideal Tail Current

#### Comparison

As it can be seen, the differential output voltages for both cases are the same. So for small input CM noise, the differential pair is not affected.

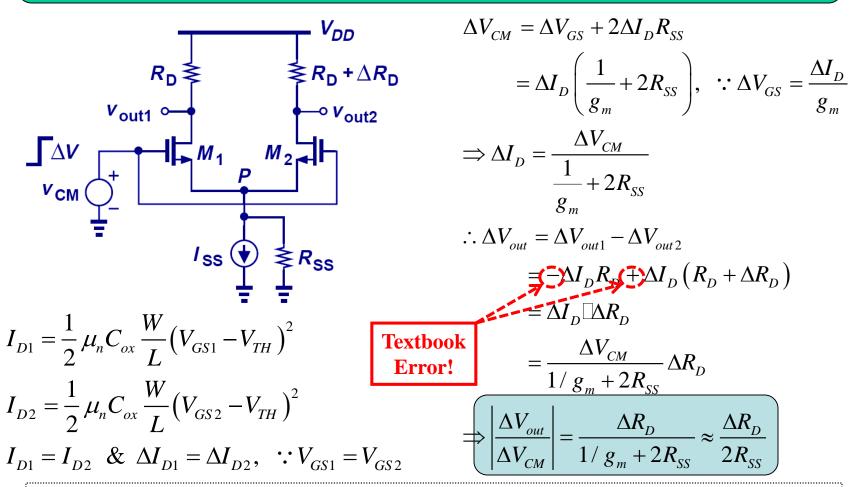

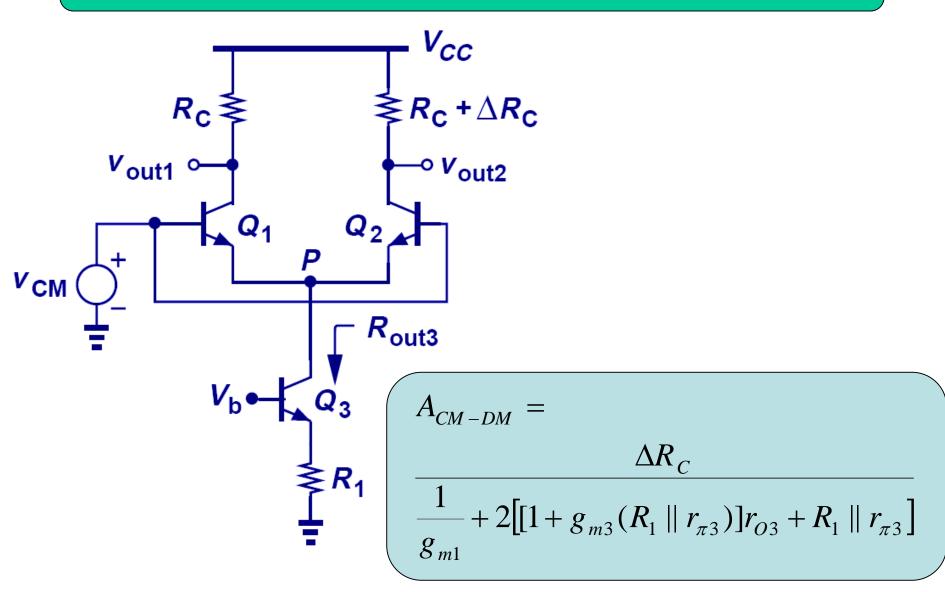

# CM to DM Conversion, A<sub>CM-DM</sub>

If finite tail impedance and asymmetry are both present, then the differential output signal will contain a portion of input common-mode signal.

CH 10 Differential Amplifiers

# Example: A<sub>CM-DM</sub>

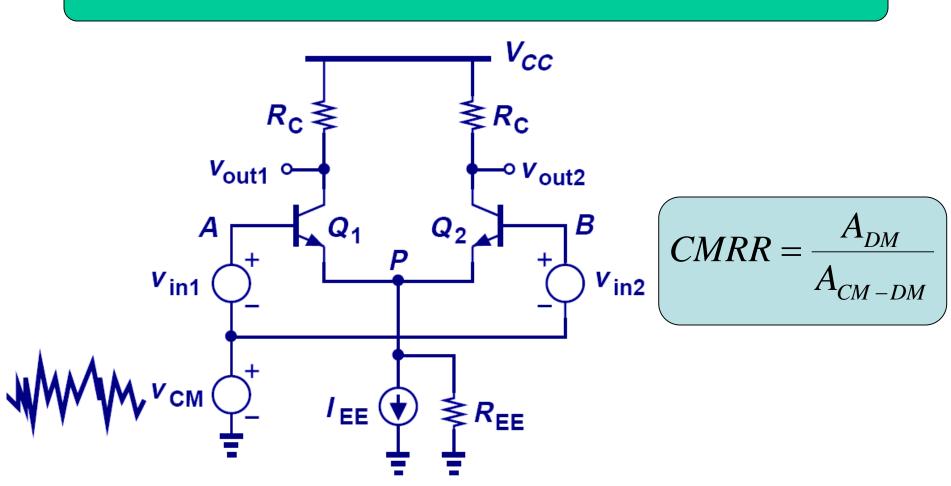

### **CMRR**

CMRR defines the ratio of wanted amplified differential input signal to unwanted converted input common-mode noise that appears at the output.

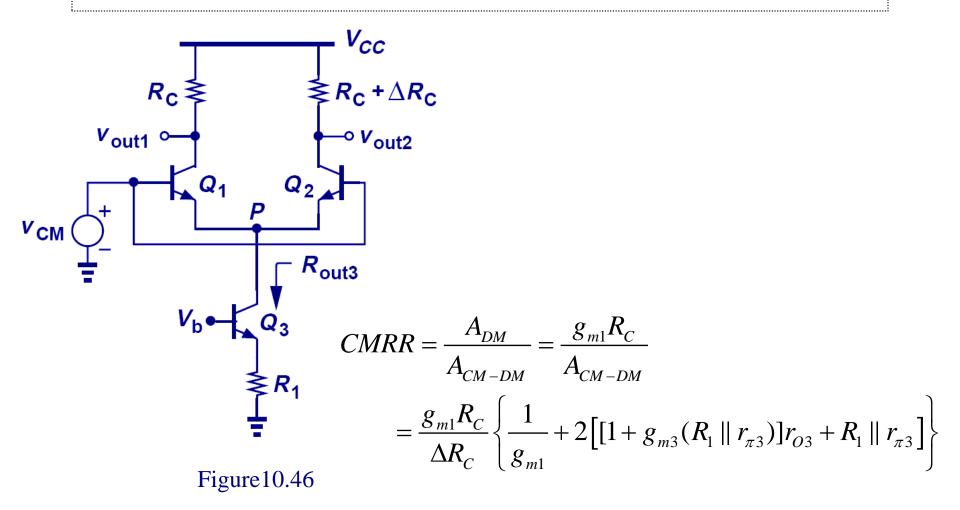

## Example 10.28

Calculate the CMRR of the circuit in Fig. 10.46.

CH 10 Differential Amplifiers

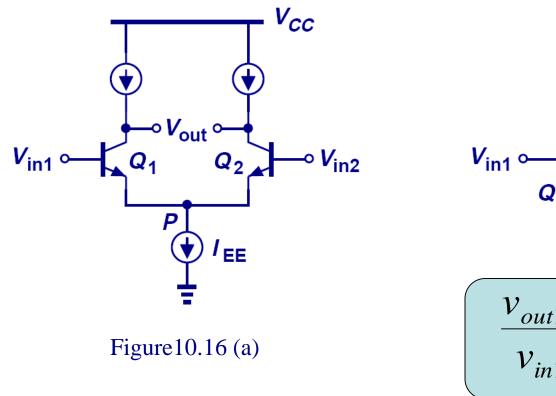

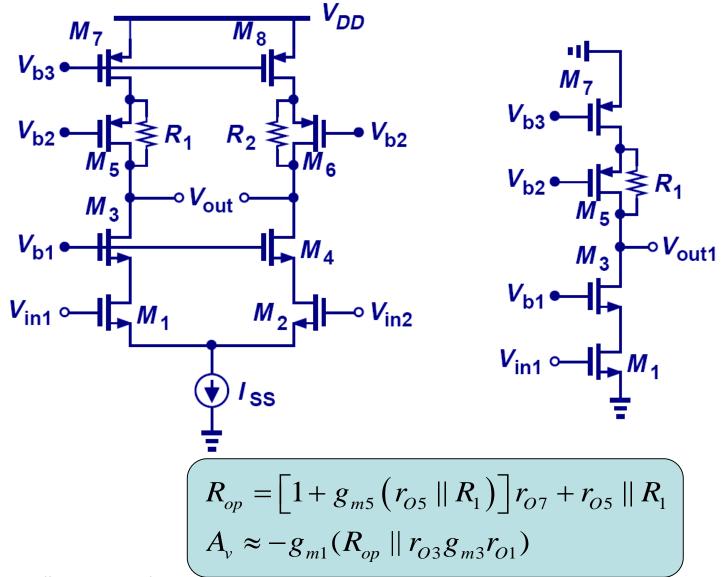

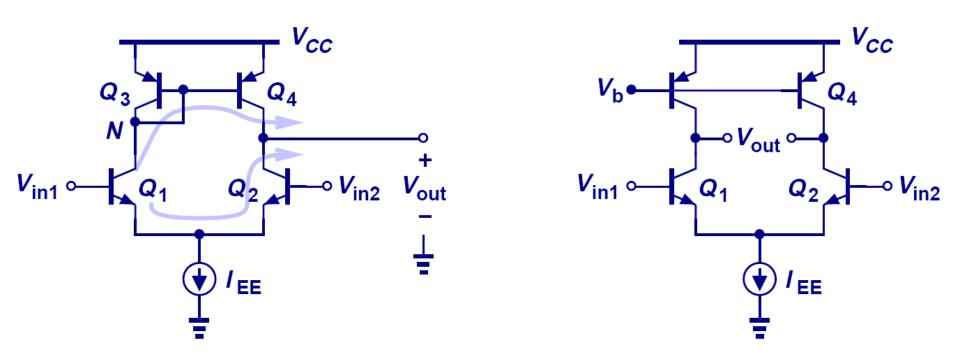

#### **Differential to Single-ended Conversion**

Many circuits require a differential to single-ended conversion, however, the above topology is not very good.

# **Supply Noise Corruption**

The most critical drawback of this topology is supply noise corruption, since no common-mode cancellation mechanism exists. Also, we lose half of the signal.

### **Better Alternative**

This circuit topology performs differential to single-ended conversion with no loss of gain.

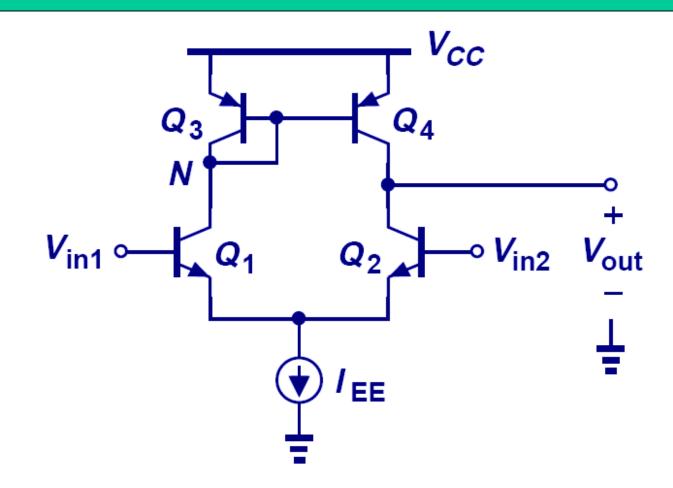

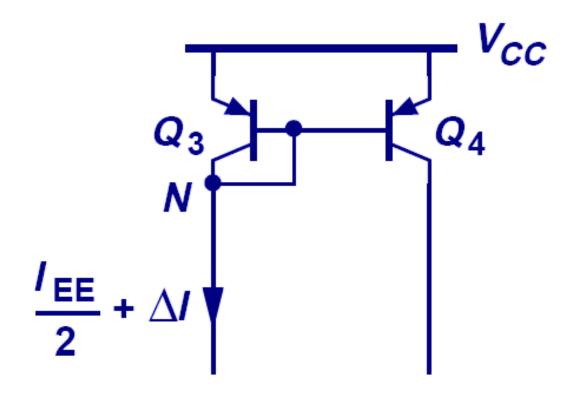

## **Active Load**

- With current mirror used as the load, the signal current produced by the  $Q_1$  can be replicated onto  $Q_4$ .

- This type of load is different from the conventional "static load" and is known as an "active load".

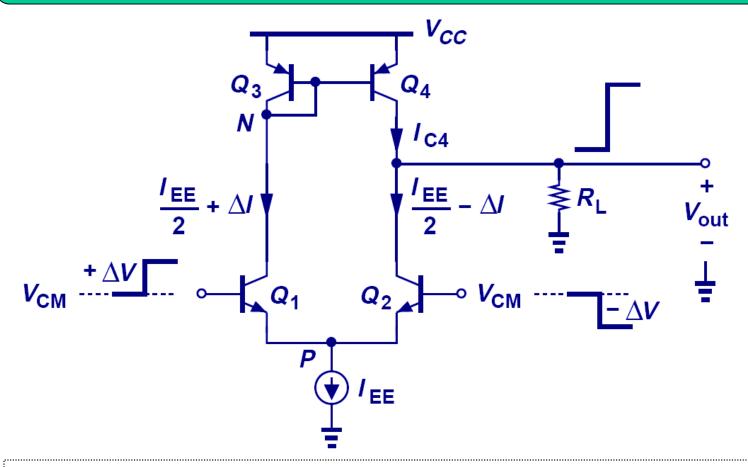

#### **Differential Pair with Active Load**

> The input differential pair decreases the current drawn from  $R_L$  by  $\Delta I$  and the active load pushes an extra  $\Delta I$  into  $R_L$  by current mirror action; these effects enhance each other.

#### Active Load vs. Static Load

The load on the left responds to the input signal and enhances the single-ended output, whereas the load on the right does not.

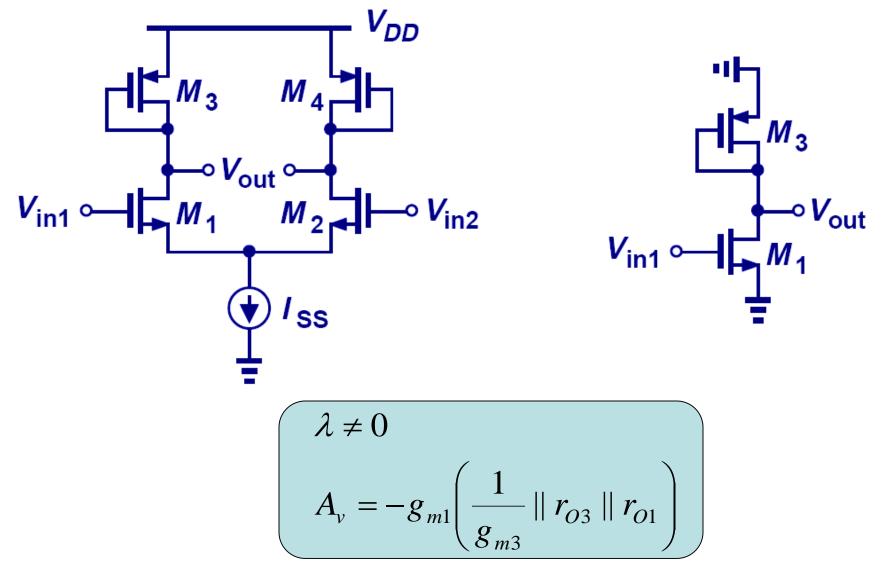

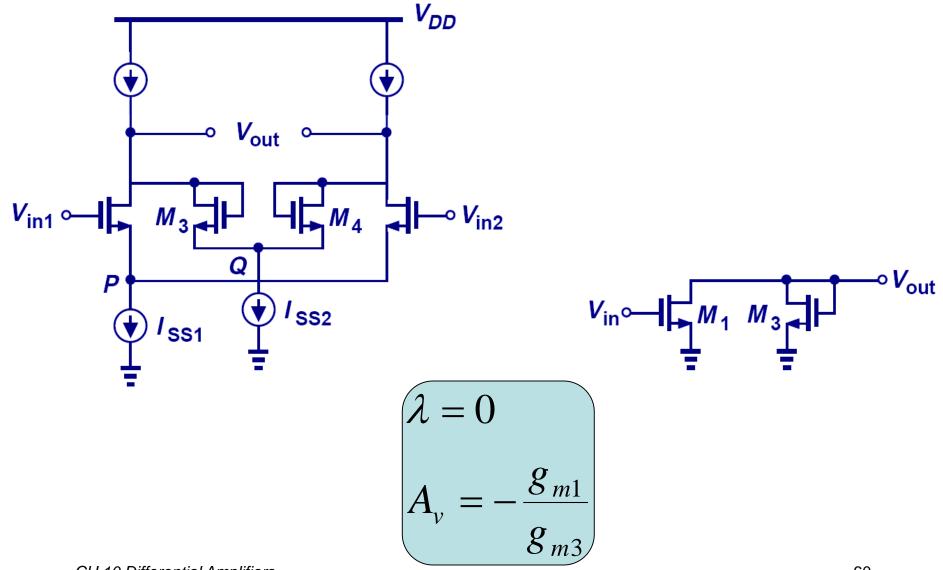

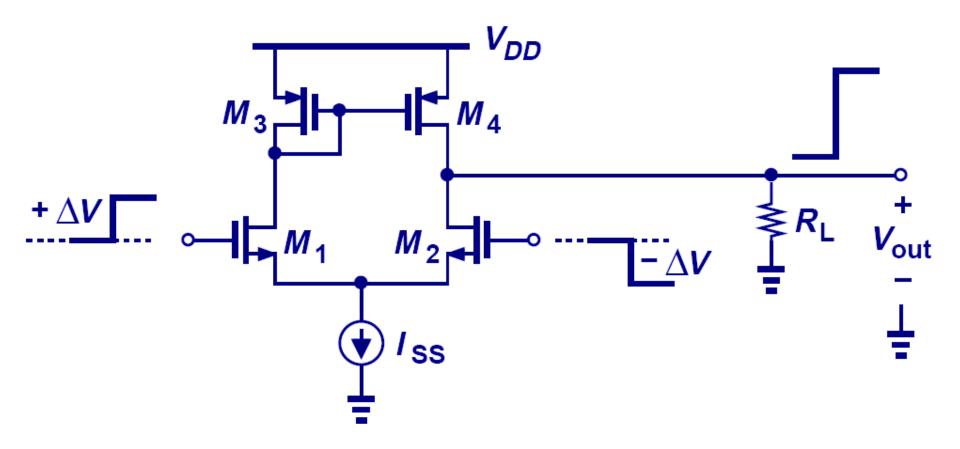

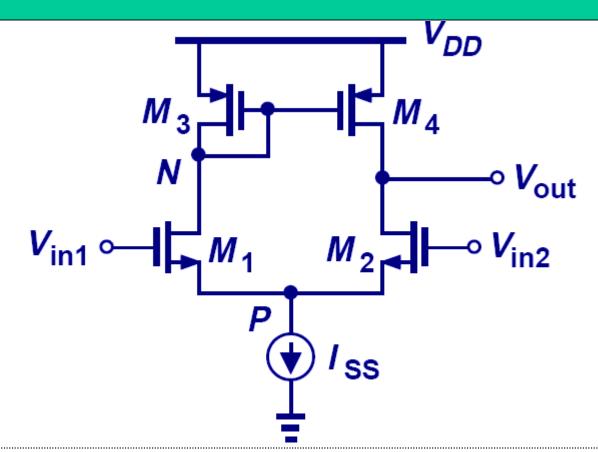

## **MOS Differential Pair with Active Load**

Similar to its bipolar counterpart, MOS differential pair can also use active load to enhance its single-ended output.

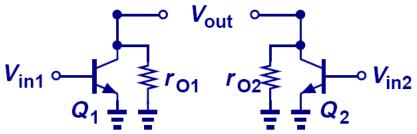

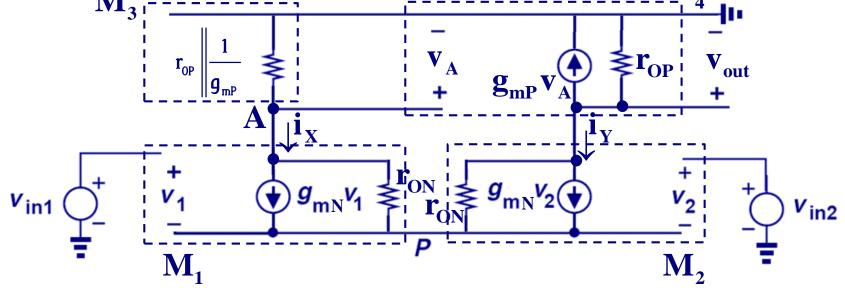

# **Asymmetric Differential Pair**

Because of the vastly different resistance magnitude at the drains of M<sub>1</sub> and M<sub>2</sub>, the voltage swings at these two nodes are different and therefore node P cannot be viewed as a virtual ground when V<sub>in2</sub>=-V<sub>in1</sub>.

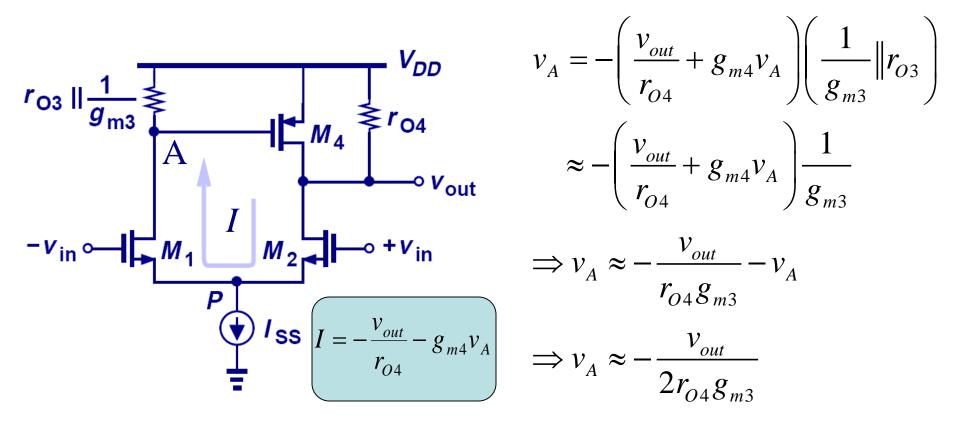

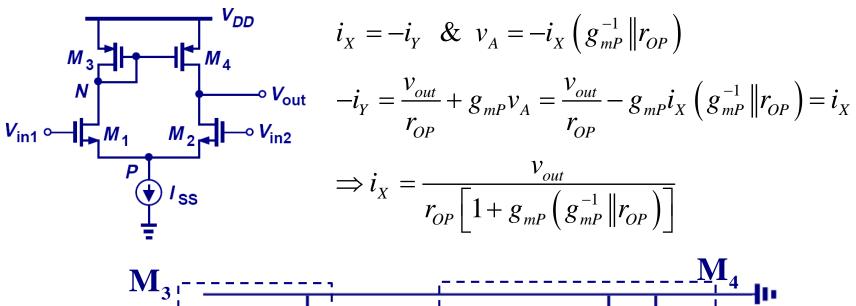

#### **Quantitative Analysis - Approach 1**

#### Quantitative Analysis - Approach 1 – cont'd

$$-v_{A} + (i_{X} - g_{mN}v_{1})r_{ON} - (i_{Y} - g_{mN}v_{2})r_{ON} + v_{out} = 0$$

$$\Rightarrow -v_{A} + 2i_{X}r_{ON} - g_{mN}r_{ON}(v_{in1} - v_{in2}) + v_{out} = 0$$

$$\because v_{1} - v_{2} = v_{in1} - v_{in2} \quad \& \quad i_{X} = -i_{Y}$$

Substituting for  $v_A$  and  $i_X$ ,

$$\frac{v_{out}}{r_{OP} \left[1 + g_{mP} \left(g_{mP}^{-1} \| r_{OP}\right)\right]} \left(g_{mP}^{-1} \| r_{OP}\right) + 2r_{ON} \frac{v_{out}}{r_{OP} \left[1 + g_{mP} \left(g_{mP}^{-1} \| r_{OP}\right)\right]} + v_{out} = g_{mN} r_{ON} \left(v_{in1} - v_{in2}\right)$$

$$\Rightarrow \frac{v_{out}}{v_{in1} - v_{in2}} = g_{mN} r_{ON} \frac{r_{OP} \left[1 + g_{mP} \left(g_{mP}^{-1} \| r_{OP}\right)\right]}{2r_{ON} + 2r_{OP}} \\\approx g_{mN} \left(r_{ON} \| r_{OP}\right)$$

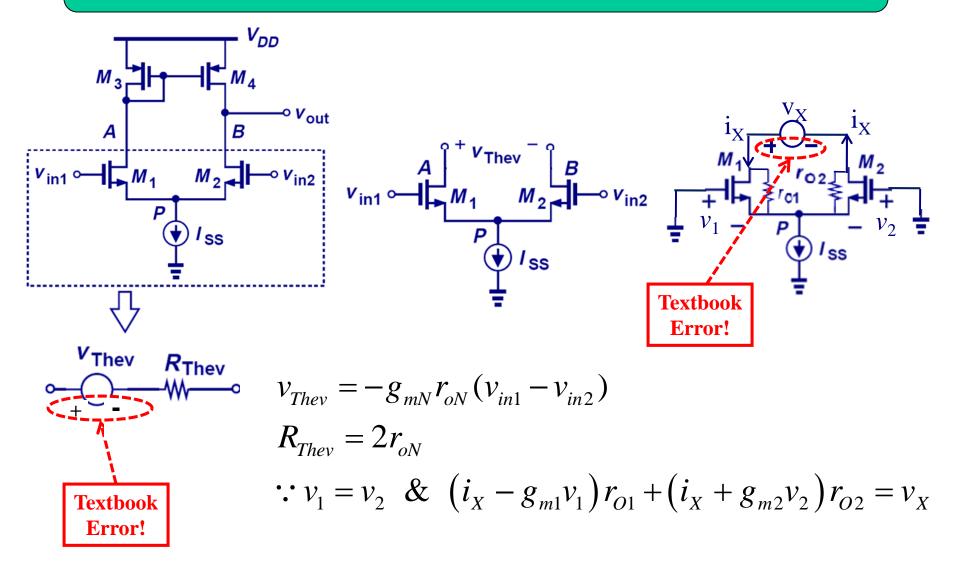

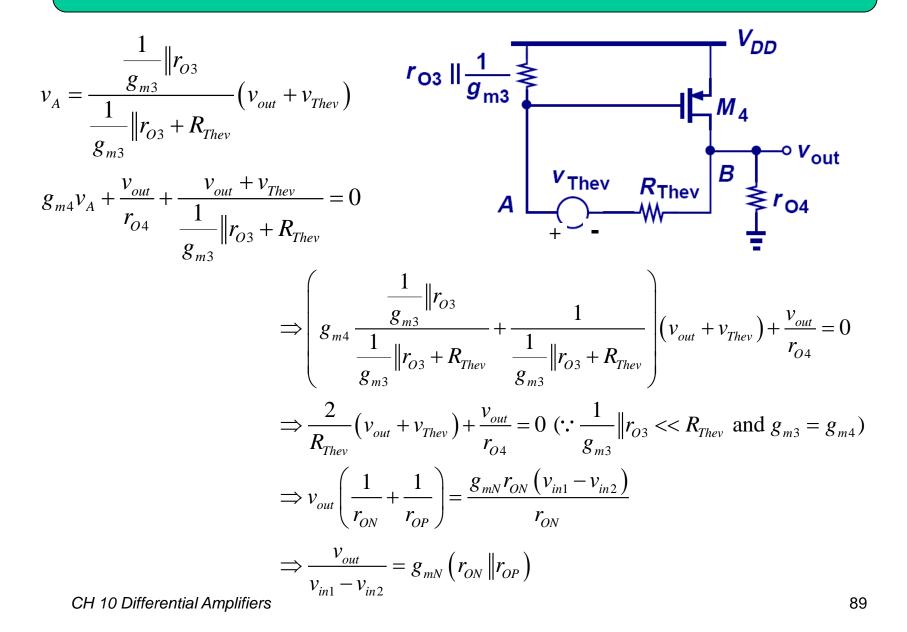

#### **Quantitative Analysis - Approach 2**

#### Quantitative Analysis - Approach 2 – cont'd

## Example 10.29

Prove that the voltage swing at node A is much less than that at the output.